[新連載]CPLD入門!

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

いつか使うことになるだろうと思ってはいたのですが。

何を今頃になって、というようなものですが。

ようやく本気で、CPLDと四つに取り組みます。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

[第42回]

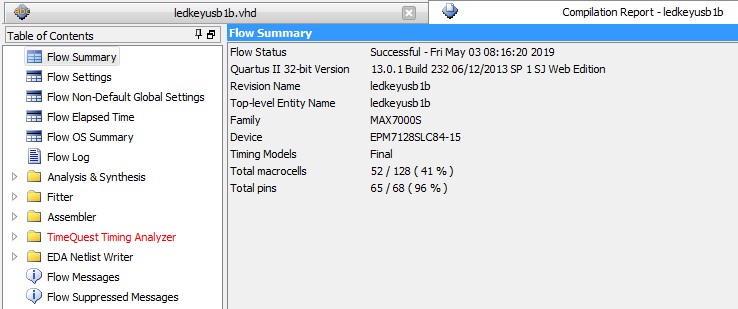

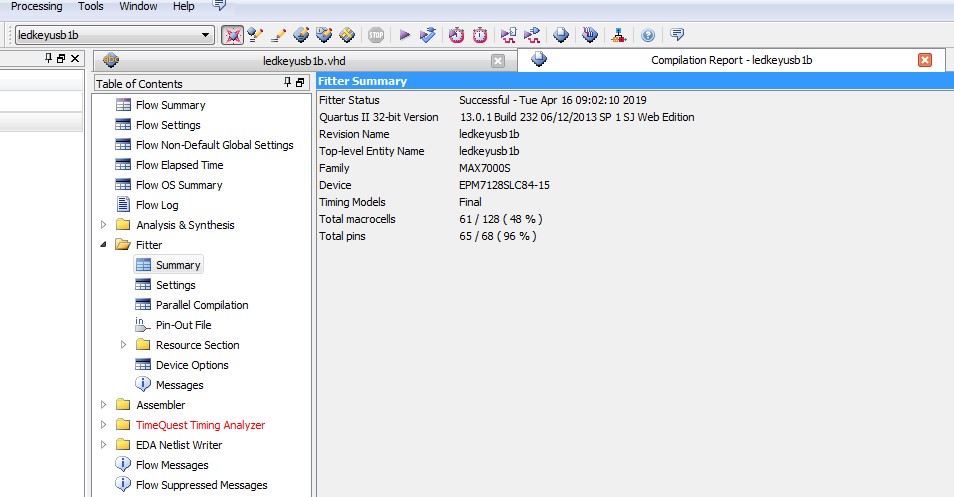

●ムダを省きました

本日になって前回を読み直していましたら、VHDLプログラムで無駄な事をやっているところをみつけましたので、修正いたしました。

--key in

の下記の部分です。

elsif AIN(7 downto 2)="100111" and IOR='0' then

keyinbf<=KEYIN;

DINOUT<=keyinbf;

|

architecture rtl of ledkeyusb1b is

signal ldtactiv:std_logic;

signal readyreset:std_logic;

signal ldatareadywk:std_logic;

signal keyoutbf:std_logic_vector(2 downto 0);

--signal keyinbf:std_logic_vector(7 downto 0);

signal ledadrs:std_logic_vector(2 downto 0);

signal segment:std_logic_vector(7 downto 0);

signal rcwk:std_logic;

signal rcwk2:std_logic_vector(3 downto 0);

|

elsif AIN(7 downto 2)="100111" and IOR='0' then

--keyinbf<=KEYIN;

--DINOUT<=keyinbf;

DINOUT<=KEYIN;

|