偦偙偺偲偙傠偺恾傪僐僺乕偟偰揧晅偟偰偄偨偩偒傑偟偨丅

側偵偟傠丄恄條偺傛偆側丄搱丂惓棙巵偑彂偐傟偨傕偺偩偲偄偆偙偲偱偡偐傜丄杮摉偼偦偺傑傑偙偙偵宖嵹偟偨偄偺偱偡偗傟偳丄侾俋俈俆擭摉帪偺乽僀儞僞乕僼僃乕僗乿帍偺婰帠丄偲偄偆偩偗偱丄巹帺恎偑弌揟傪妋擣偟偨傢偗偱傕偁傝傑偣傫偟丄栜榑丄搱丂惓棙巵偐傜傕俠俻弌斉幮偐傜傕丄摨堄傪摼偨傢偗偱偼偁傝傑偣傫偐傜丄偄偨偩偄偨傕偺乮俹俢俥僼傽僀儖乯傪偦偺傑傑偙偙偵倀俹偡傞偺偼丄傗偭傁傝傛偔側偄側偁偲巚偄傑偡丅巆擮偱偡偗傟偳乧丅

側偺偱丄偱偒傞偩偗丄尨堄傪懝側傢側偄掱搙偵丄偦偺奣棯傪偛徯夘偡傞偙偲偵偄偨偟傑偡丅

仠搱丂惓棙巵偺峫偊偨俢俙俙夞楬

搱丂惓棙巵偼丄俢俙俙柦椷偺僔乕働儞僗傪師偺傛偆偵夝愢偟偰偄傑偡丅

嘆僉儍儕乕傪僉儍儕乕丒僥儞億儔儕乕偵揮憲偡傞偲偲傕偵丄傾僉儏儉儗乕僞偺抣傪僥儞億儔儕儗僕僗僞偵揮憲偡傞

嘇傾僉儏儉儗乕僞偲僉儍儕乕偵傛偭偰丄曗惓悢傪傾僉儏儉儗乕僞丒僥儞億儔儕偵僗僩傾偡傞

嘊壛嶼寢壥傪傾僉儏儉儗乕僞偵僗僩傾偡傞

偦偟偰曗惓偺忦審偼壓婰偺捠傝丄偲偟偰偄傑偡丅

壓埵丂僴乕僼僉儍儕乕傑偨偼俙俁乣俙侽亞侾侽

忋埵丂僉儍儕乕傑偨偼俙俈乣俙係亞侾侽傑偨偼丄俙俈乣俙係亖俋偐偮俙俁乣俙侽亞侾侽

偙傟偼丄乵戞俀俀係夞乶偱愢柧偟偨丄乽俢俙俙柦椷偺夞楬偺峫偊曽乿偲摨偠偱偡丅

傕偭偲傕巹偑偨偳傝拝偄偨俢俙俙偺夞楬偺峫偊曽偱傛偄偺偩丄偲偄偆偙偲偵偮偄偰偼丄乵戞俀俀係夞乶偱彂偒傑偟偨傛偆偵丄俉侽俉侽倀倱倕倰乫倱丂俵倎値倳倎倢偺婰嵹偵傛偭偰丄妋擣嵪傒偺偙偲偱偡丅

偟偐偟丄搱丂惓棙巵偛帺恎偺挊嶌偵傛偭偰丄偦偺偙偲偑棤晅偗傜傟傞丄偲偄偆偺偼丄傑偨奿暿偺婐偟偝偱偡丅

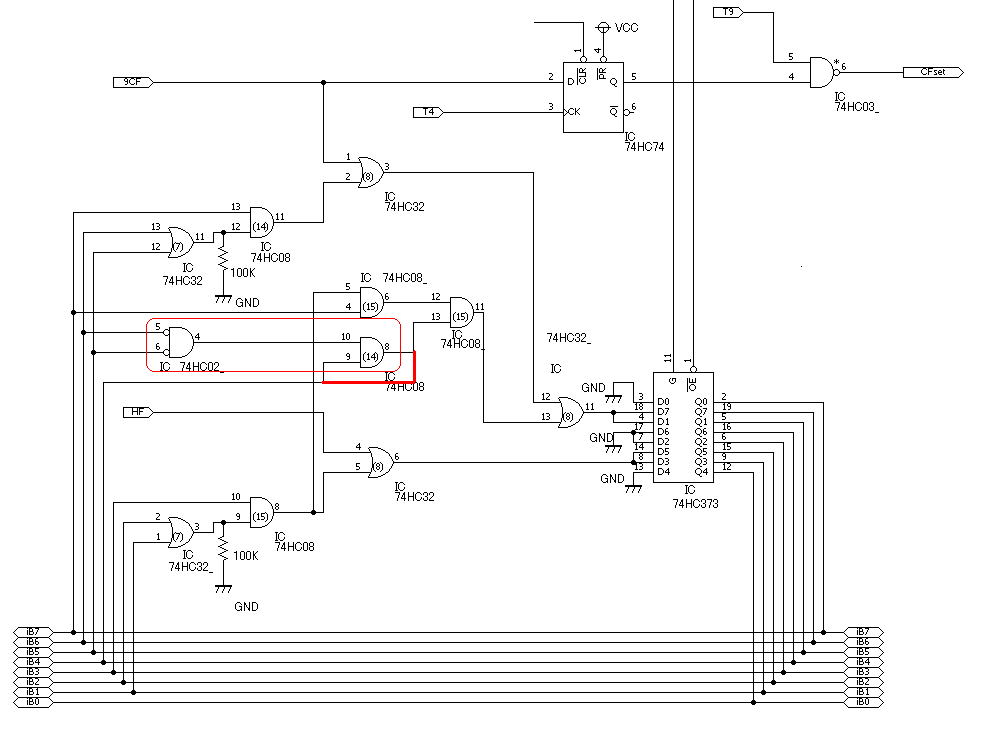

壓恾偼丄儊乕儖偵揧晅偟偰偄偨偩偄偨搱丂惓棙巵偺廫恑曗惓乮俢俙俙乯夞楬恾傪傕偲偵丄巹偑嶌恾偟傑偟偨丅

傗偨傜丄僥儞億儔儕儗僕僗僞側傞岅偑弌偰偒偰柺怘傜偭偰偟傑偄傑偡偑丄憗偄榖偑丄儚乕僋儗僕僗僞偺偙偲偱偡丅

恾偺塃壓曽偵偁傞丄僥儞億儔儕丒儗僕僗僞偲偄偆偺偼乽偮偔傞俠俹倀乿偺夞楬偱偼丄俙俴倀儗僕僗僞乭俙乭偵憡摉偟傑偡丅

偦偺忋偺傾僉儏儉儗乕僞丒僥儞億儔儕偲偄偆偺偼丄摨偠偔俙俴倀儗僕僗僞乭俛乭偵憡摉偟傑偡丅

俙俴倀儗僕僗僞乭俙乭偵傾僉儏儉儗乕僞乮俙儗僕僗僞乯偺抣傪擖傟丄俙俴倀偺儗僕僗僞乭俛乭偵乭俇侽乭偐乭侽俇乭偐乭俇俇乭傪擖傟偰壛嶼偡傞丄偲偄偆偙偲偱偡偐傜丄乽偮偔傞俠俹倀乿偺夞楬偲摨偠偱偡丅

偲偙傠偱丄俠乮僉儍儕乕僼儔僌乯丄俫乮僴乕僼僉儍儕乕僼儔僌乯偲俙儗僕僗僞偺抣偺忦審偵傛偭偰丄壛嶼抣偺乭俇乭偐乭侽乭傪慖戰偡傞晹暘偺僎乕僩榑棟夞楬偼偳偆側偭偰偄傞偱偟傚偆偐丅

偙偙偼側傫偩偐偪傚偄偲堘偭偰偄傞傛偆偱偡丅

棟孅偼摨偠側偺偱偡偑乧丅

乽偮偔傞俠俹倀乿偺丄偙偺晹暘偵憡摉偡傞夞楬恾偼乵戞俀俀係夞乶偵偁傝傑偡偑丄斾妑偺偨傔偵丄偦偺偆偪偺丄僎乕僩榑棟夞楬偩偗傪愗傝庢偭偰壓偵帵偟傑偡丅

價僢僩俁乣價僢僩侾傪擖椡偟偰偄傞晹暘偼慡偔摨偠偱偡丅俷俼亅俙俶俢亅俷俼偺慻傒崌傢偣偱偡丅

價僢僩俈乣價僢僩俆偺晹暘傕丄搱丂惓棙巵偺夞楬偑丄慜抜偺俷俼偑俁擖椡偵側偭偰偄傞偙偲傪彍偗偽丄偙偙傕摨偠偱偡丅

乽偮偔傞俠俹倀乿偺丄夞楬恾偺恀拞偵偁傞榑棟夞楬偑椉幰偱堎側偭偰偄傑偡丅

偙偙偼丄價僢僩俈乣係偑乭俋乭偱丄價僢僩俁乣侽偑乭俙乭乣乭俥乭偺応崌傪慖戰偟偰偄傞夞楬偱偡丅

巹偼攏幁惓捈偵丄忋埵偑乭俋乭偱丄壓埵偑乭俙乭埲忋丄偲偄偆忦審傪偦偺傑傑夞楬偵偟傑偟偨偑丄搱丂惓棙巵偼丄偙偙偺偲偙傠傪丄俁擖椡偺俷俼傪巊偭偰丄乮倐倝倲俈亖侾乯倎値倓乮乮倐倝倲俇亖侾乯倧倰乮倐倝倲俆亖侾乯倧倰乮乮倐倝倲係亖侾乯倎値倓乮倐倝倲俁乣侽亞乭俙乭乯乯乯偲偟偰偟傑偭偰偄傞偺偱偡丅

偆乕傫丅偙傟偼丄婥偑偮偒傑偣傫偱偟偨丅

偦偺峫偊傪丄乽偮偔傞俠俹倀乿偺夞楬偵庢傝擖傟傞偲丄恾偺愒巐妏偱埻偭偨俀屄偺僎乕僩偑晄梫偵側偭偰偟傑偄傑偡丅

偦偟偰丄偦偺屻抜偺俙俶俢傊偼丄愒懢慄偺傛偆偵丄倐倝倲係傪擖傟傟偽傛偄偺偱偡丅

偙傟偱丄摨偠峫偊偺夞楬偵側傝傑偟偨丅

偊丠傑偩丄堘偭偰偄傑偡丠

巆擮側偙偲偵丄俈係俫俠僔儕乕僘偵偼丄俁擖椡偺俷俼偑側偄偺偱偡丅

偱偡偐傜丄偙偆側傝傑偡丅

曄峏屻偺夞楬偺奩摉晹暘傪榑棟幃偱昞偡偲丄

乮乮倐倝倲俈亖侾乯倎値倓乮乮倐倝倲俇亖侾乯倧倰乮倐倝倲俆亖侾乯乯乯倧倰乮乮倐倝倲俈亖侾乯倎値倓乮乮倐倝倲係亖侾乯倎値倓乮倐倝倲俁乣侽亞乭俙乭乯乯乯

偵側傝傑偡偐傜丄椉幰偼摨偠偱偡丅

偝偭偦偔帋嶌婎斅傪丄忋偺夞楬恾偺傛偆偵曄峏偟偰乮傑偨僷僞乕儞僇僢僩偲僕儍儞僷偱偡乯丄俢俙俙僥僗僩僾儘僌儔儉乮乵戞俀俀俆夞乶乯傪憱傜偣偰丄寢壥傪妋擣偟偰傒傑偟偨丅

偙偆偄偆偲偒偵丄儊儌儕偺僶僢僋傾僢僾偼幚偵彆偐傝傑偡丅

傑偩丄愭夞僥僗僩偟偨僾儘僌儔儉偑偦偺傑傑儊儌儕偵巆偭偰偄傑偟偨偐傜丄偦傟傪幚峴偟偰丄僗僞僢僋傪妋擣偡傞偩偗偱偡丅

偪傚偄丄偪傚偄丄偱廔傢偭偰偟傑偄傑偟偨丅

栜榑丄寢壥偼俷俲丄偱偟偨丅

婱廳側忣曬傪儊乕儖偱偍抦傜偣偄偨偩偄偨丄婒晫導偺俲條丄杮摉偵桳擄偆偛偞偄傑偟偨丅

偠偮偼丄俲條偐傜偼丄傕偆傂偲偮丄倃俠俫俧偵偮偄偰偺忣曬傕偄偨偩偒傑偟偨丅

偦偺倃俠俫俧偵偮偄偰偼丄師夞偵彂偔偙偲偵偄偨偟傑偡丅

俀侽侽俋丏俆丏俀俆倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞