昗弨俿俿俴偩偗乮両乯偱CPU傪偮偔傠偆両乮慻棫偰僉僢僩偱偡両乯

(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞俀係俆夞乶

仠妱崬傒偺僥僗僩夞楬偱偡

俉侽俉侽偺妱崬傒偼丄妱崬傒怣崋乮俬俶俿乯傪庴晅偗偨捈屻偵奜晹僨乕僞僶僗偵忔偣傜傟偨俼俽俿柦椷傪撉傒崬傓偙偲偱峴傢傟傑偡丅

捠忢偼僨乕僞僶僗偵偼壗傕偺偣側偔偰傕丄俬俶俿怣崋偝偊擖椡偡傟偽丄妱崬傒偑幚峴偝傟傞丄俼俽俿俈妱崬傒偑嵟傕傛偔巊傢傟傑偡丅

偙偺乽偮偔傞俠俹倀乿偱傕丄偱偡偐傜俬俶俿怣崋傪庴偗晅偗偰丄俼俽俿俈傪幚峴偡傞傛偆側夞楬偝偊偮偔偭偰偍偗偽丄傑偁丄偦傟偱傛偄偺偱偼側偄偐丄廫暘偱偟傚偆丄偲傕峫偊偨偺偱偡偑丄傗偭傁傝偱偒傞偩偗俉侽俉侽偵嬤偄摦嶌傪幚尰偟偨偄偲偄偆偙偩傢傝偐傜丄俼俽俿俈偩偗偱偼側偔偰丄僨乕僞僶僗偵忔偣傜傟偨俼俽俿侽乣俼俽俿俇傪撉傒崬傫偱丄妱崬傒張棟傪峴偆偲偄偆丄乽杮暔巙岦乿偺夞楬傪嶌偭偰偟傑偄傑偟偨丅

嶌偭偨偐傜偵偼摦嶌僥僗僩傪偟側偗傟偽側傝傑偣傫丅

俼俽俿俈妱崬傒偼丄俬俶俿怣崋傪擖傟傞偩偗偱偡偐傜丄娙扨偱偡丅

偟偐偟丄偦偺懠偺丄俼俽俿侽乣俼俽俿俇偼丄俬俶俿怣崋傪擖傟傞偩偗偱偼偩傔偱丄僨乕僞僶僗偵俼俽俿侽乣俼俽俿俇偺俷俹僐乕僪傪忔偣側偗傟偽側傝傑偣傫丅

偱傕丄偦傟偼偦傟傎偳擄偟偄偙偲偱偼側偔偰丄恾偺傛偆偵偟偰娙扨偵僥僗僩偡傞偙偲偑偱偒傑偟偨丅

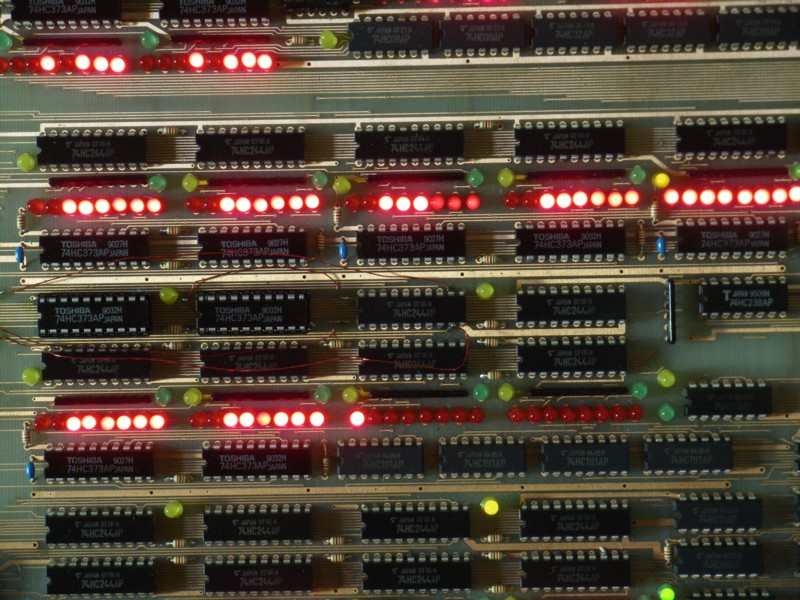

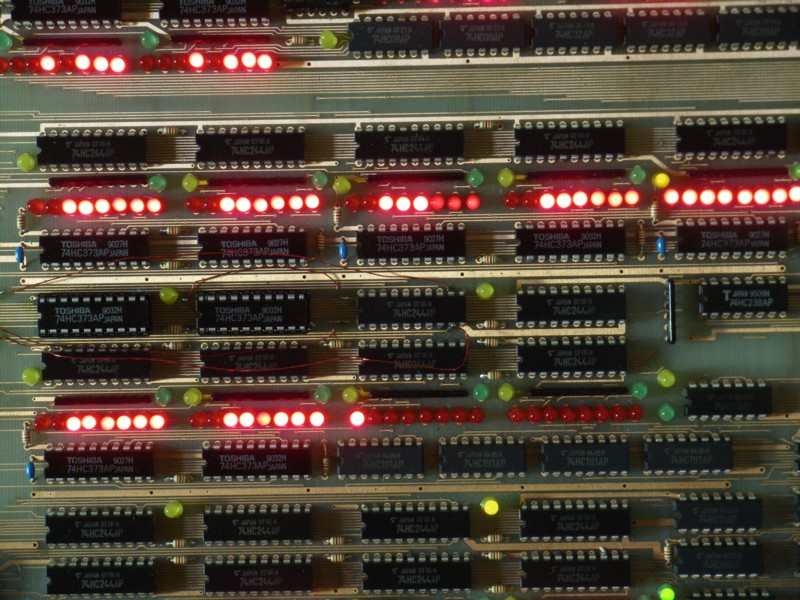

偙偙偱偺億僀儞僩偼恀拞偵偁傞俈係俫俠侾俀俇偱偡丅

嵍偵偁傞偺偼丄摉幮偺俛俙俽俬俠惂屼儃乕僪倅俛俀俆俲偱偡丅

憖嶌偑娙扨側偺偱丄崱夞偺僥僗僩偵棙梡偟傑偟偨丅

倅俛俀俆俲忋偺俬乛俷億乕僩俉俀俠俆俆偐傜俬俶俿怣崋傪乽偮偔傞俠俹倀乿婎斅偵弌椡偟傑偡丅

偦傟偵愭偩偭偰丄俼俽俿柦椷偺俁價僢僩偺儀僋僩儖傪弌椡偟傑偡丅

偙偺俁價僢僩偺弌椡偼丄乽偮偔傞俠俹倀乿偑俬俶俿怣崋傪庴偗晅偗偨偁偲偵弌偝傟傞丄俬俶俿俼俢怣崋偺婜娫拞偵僨乕僞僶僗偵忔偣傞昁梫偑偁傝傑偡丅

偦偙偱恾偺傛偆偵俈係俫俠侾俀俇傪巊偄傑偡丅偙偆偡傞偙偲偱丄奜晹偱偼摿暿偺僞僀儈儞僌側偳傪峫椂偟側偔偰傕丄偨偩俁價僢僩傪弌椡偟偰偍偔偩偗偱嵪傒傑偡偐傜旕忢偵娙扨偱偡丅

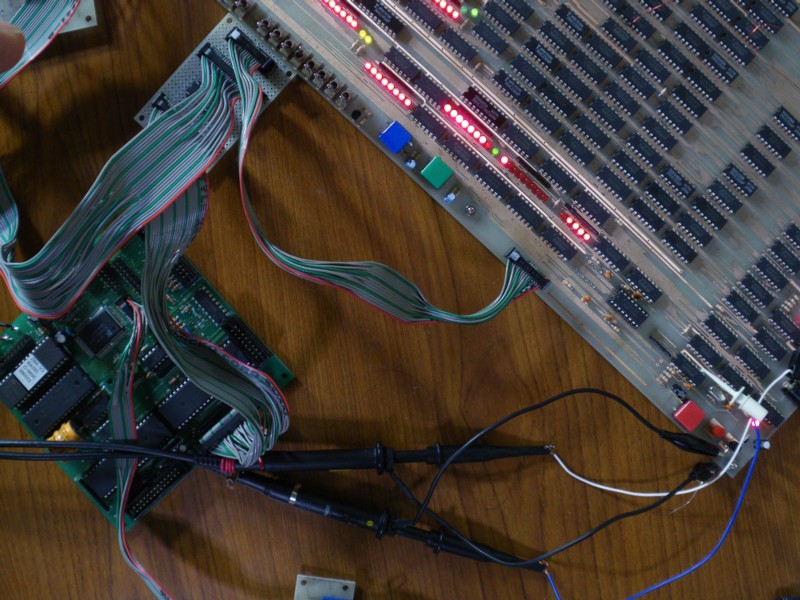

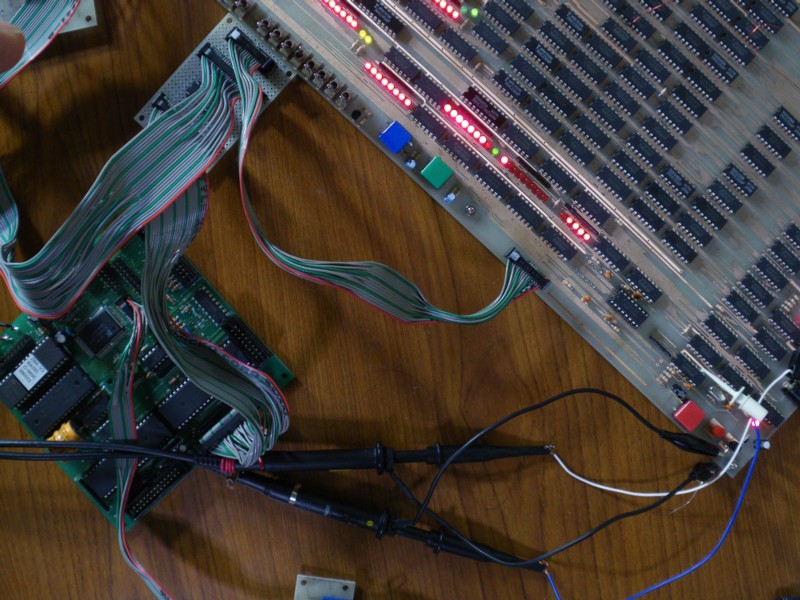

仠僥僗僩傪峴偆偨傔偵俛俙俽俬俠儃乕僪偲愙懕偟偰偄傞條巕偱偡

嵍懁偵偁傞偺偑俛俙俽俬俠儃乕僪倅俛俀俆俲偱偡丅

幨恀偱偼僼儔僢僩働乕僽儖偵塀傟偰偟傑偭偰尒偊傑偣傫偑丄彫偝偄僕儍僲栚婎斅偵俈係俫俠侾俀俇傪忔偣偰丄倅俛俀俆俲丄僕儍僲栚婎斅丄乽偮偔傞俠俹倀乿偺娫傪僼儔僢僩働乕僽儖偱愙懕偟偰偄傑偡丅

仠妱崬傒偺僥僗僩僾儘僌儔儉偱偡

2009/6/8 20:47 INTTEST.TXT

END=0060

;;; MYCPU80 INT TEST(RST1-RST6) 09/06/08

;;;

ORG $0000

0000 C34000 JMP START

;RST1

ORG $0008

0008 F5 PUSH PSW

0009 04 INR B

000A F1 POP PSW

000B FB EI

000C C9 RET

;RST2

ORG $0010

0010 F5 PUSH PSW

0011 0C INR C

0012 F1 POP PSW

0013 FB EI

0014 C9 RET

;RST3

ORG $0018

0018 F5 PUSH PSW

0019 14 INR D

001A F1 POP PSW

001B FB EI

001C C9 RET

;RST4

ORG $0020

0020 F5 PUSH PSW

0021 1C INR E

0022 F1 POP PSW

0023 FB EI

0024 C9 RET

;RST5

ORG $0028

0028 F5 PUSH PSW

0029 24 INR H

002A F1 POP PSW

002B FB EI

002C C9 RET

;RST6

ORG $0030

0030 F5 PUSH PSW

0031 2C INR L

0032 F1 POP PSW

0033 FB EI

0034 C9 RET

;

ORG $0040

0040 310080 START:LXI SP,$8000

0043 AF XRA A

0044 47 MOV B,A

0045 4F MOV C,A

0046 57 MOV D,A

0047 5F MOV E,A

0048 67 MOV H,A

0049 6F MOV L,A

004A FB EI

004B 3C LOOP1:INR A

004C F24B00 JP LOOP1

004F 3E07 MVI A,07

0051 D398 OUT 98

0053 3E80 MVI A,80

0055 3C LOOP2:INR A

0056 FA5500 JM LOOP2

0059 3E17 MVI A,17

005B D398 OUT 98

005D AF XRA A

005E C34B00 JMP LOOP1

;

LOOP1 =004B LOOP2 =0055 START =0040

傾僪儗僗侽侽侽侽偺俼俽俿侽偼儕僙僢僩偲摨偠偱丄崱夞偺僥僗僩偵偼岦偒傑偣傫偐傜丄彍奜偟傑偡丅

傑偨侽侽俁俉偺俼俽俿俈傕丄俬俶俿怣崋傪擖椡偡傞偩偗偱嵪傒傑偡偐傜丄偙傟傕崱夞偺僥僗僩偐傜偼彍奜偟傑偡丅

崱夞偼俼俽俿侽偲俼俽俿俈傪彍偄偨丄俼俽俿侾乣俼俽俿俇傪僥僗僩偡傞偙偲偵偟傑偟偨丅

侽侽侽侽斣抧偐傜僗僞乕僩偡傞儊僀儞僾儘僌儔儉偼俙儗僕僗僞傪僀儞僋儕儊儞僩乮亄侾乯偟側偑傜丄侾俀俉夞僇僂儞僩傾僢僾偡傞偛偲偵丄俬乛俷弌椡乮傾僪儗僗俋俉偺價僢僩係乯偐傜侾偲侽傪岎屳偵弌椡偟傑偡丅

傾僪儗僗侽侽侽俉乣侽侽俁侽偐傜巒傑傞俼俽俿侾乣俼俽俿俇僾儘僌儔儉偼丄崱夞偼僥僗僩偱偡偐傜丄娙扨側僾儘僌儔儉偵側偭偰偄傑偡丅

晛捠偼俉僶僀僩傗偦偙傜偱偼偍偝傑傝傑偣傫偐傜丄偦偙偐傜俰俵俹偟偰丄偦偺愭偵妱傝崬傒偺僾儘僌儔儉傪彂偒傑偡丅

崱夞偼儗僕僗僞傪亄侾偡傞偩偗偱偡偐傜丄俉僶僀僩偵偍偝傑偭偰偟傑偄傑偡丅

俹倀俽俫丂俹俽倂丄俹俷俹丂俹俽倂偼丄妱崬傒僾儘僌儔儉偺拞偺俬俶俼柦椷偺幚峴偵傛偭偰丄僼儔僌偑曄壔偟偰偟傑偆偺傪杊偖偨傔偵巊傢傟傑偡丅

奺儗僕僗僞偺抣傕妱崬傒僾儘僌儔儉偺幚峴偵傛偭偰曄壔偟傑偡偑丄儊僀儞僾儘僌儔儉偱偼俙儗僕僗僞埲奜偼巊偭偰偄傑偣傫偐傜丄奺儗僕僗僞傪戅旔偝偣傞昁梫偼偁傝傑偣傫丅

仠妱崬傒怣崋傪敪惗偝偣傞俛俙俽俬俠僾儘僌儔儉偱偡

偙傟偼乽偮偔傞俠俹倀乿偺僾儘僌儔儉偱偼偁傝傑偣傫丅

忋偱愢柧偟傑偟偨傛偆偵丄妱崬傒僥僗僩偺偨傔偵棙梡偟偨丄摉幮偺俛俙俽俬俠惂屼儃乕僪倅俛俀俆俲偺僾儘僌儔儉偱偡丅

10 'MYCPU80 INT TEST 09/06/08

20 OUT $83,$80

30 OUT $80,$FF

40 FOR A%=1 TO 6

50 OT%=$08+A%

60 FOR A=0 TO 1000:NEXT A

70 OUT $80,OT%

80 OUT $80,A%

90 OUT $80,OT%

100 NEXT A%

110 GOTO 40

俛俙俽俬俠傪巊偆偲丄娙扨偵弌椡怣崋傪嶌傞偙偲偑偱偒傑偡丅

偨偩丄俛俙俽俬俠偼儅僔儞岅偺僾儘僌儔儉偵斾傋偰幚峴懍搙偑抶偄偺偑寚揰偱偡丅

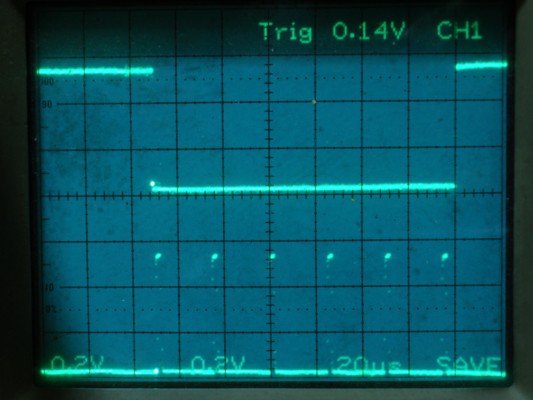

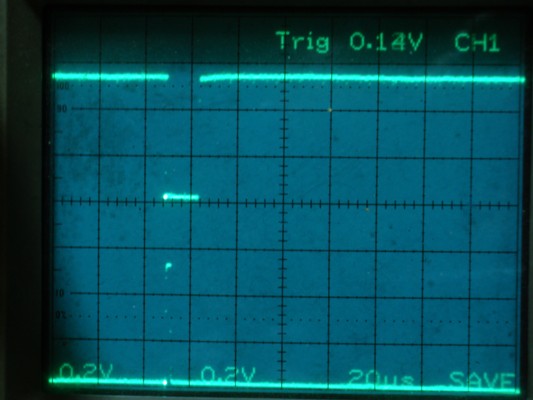

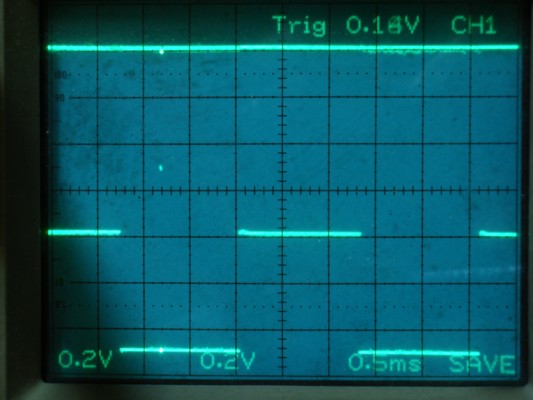

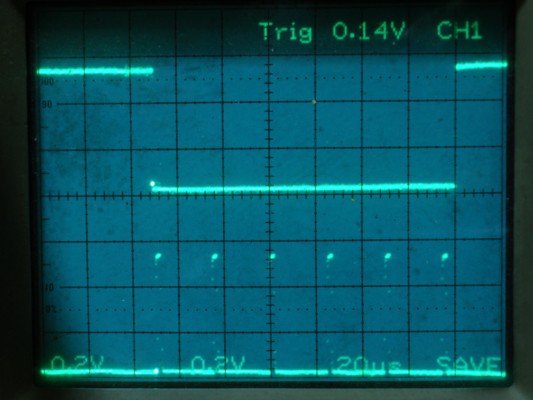

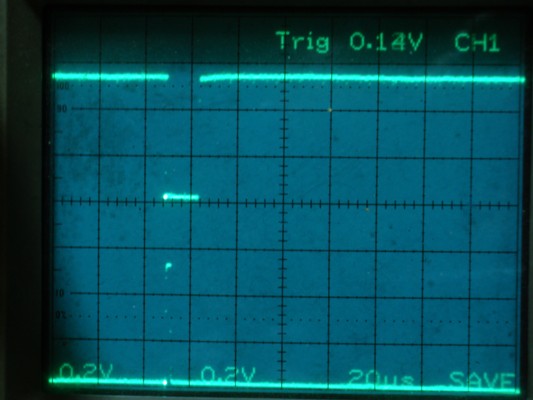

仠俬俶俿怣崋偲俬俶俿俼俢怣崋偱偡

忋乮俠俫侾乯偑俬俶俿怣崋偱丄壓乮俠俫俀乯偼俬俶俿怣崋傪庴偗晅偗偨偲偒偵乽偮偔傞俠俹倀乿懁偐傜弌椡偝傟傞俬俶俿俼俢怣崋偱偡丅

俬俶俿怣崋偺暆偑挿偄偨傔偵丄妱崬傒偑暋悢夞庴偗晅偗傜傟偰偟傑偄傑偡丅

側偍偙傟偼乽妱崬傒張棟拞乿偵廳偹偰妱崬傒偑庴偗晅偗傜傟偰偄傞偺偱偼側偔偰丄乽妱崬傒偑廔椆偟偨捈屻乿偵師偺妱崬傒偑庴偗晅偗傜傟偰偄傞偺偱丄堎忢側摦嶌偱偼偁傝傑偣傫丅

偱傕丄崱夞偺僥僗僩偺杮棃偺偹傜偄偲偟偰偼丄1夞偺俬俶俿怣崋偱侾夞偺妱崬傒偑庴偗晅偗傜傟傞丄偲偄偆偙偲偵偁傝傑偡偐傜丄偙傟偼丄偪傚偭偲丄側傫偲偐偟偨偄偲偙傠偱偡丅

仠俬俶俿怣崋偺偲偙傠偩偗丄儅僔儞岅僒僽儖乕僠儞傪巊偄傑偟偨

10 'MYCPU80 INT TEST 09/06/08

20 OUT $83,$80

30 OUT $80,$FF

40 FOR A%=1 TO 6

60 FOR A=0 TO 200:NEXT A

70 USR($4010)

100 NEXT A%

110 GOTO 40

4010 3A40F4 LD A,($F440)

4013 D380 OUT (80),A

4015 0610 LD B,10

4017 05 DEC B

4018 C21740 JP NZ,$4017

401B F608 OR 08

401D D380 OUT (80),A

401F C9 RET

忋偼俛俙俽俬俠僾儘僌儔儉偱丄壓偼俛俙俽俬俠僾儘僌儔儉偱俠俙俴俴偟偰偄傞儅僔儞岅僾儘僌儔儉偱偡丅

偙偪傜偼倅俉侽俠俹倀側偺偱丄僓僀儘僌僯乕儌僯僢僋傪巊偭偰偄傑偡丅

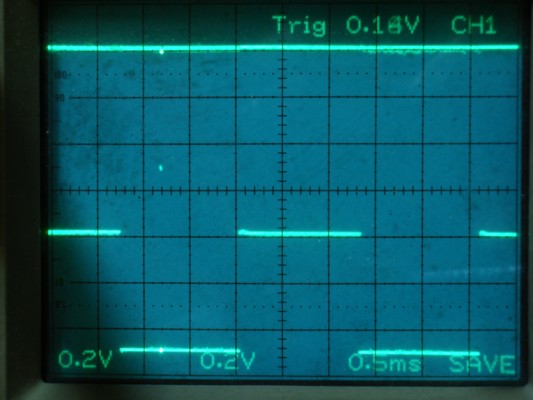

俬俶俿怣崋偺暆偑抁偔側偭偨偨傔丄侾夞偺俬俶俿怣崋偱侾夞偩偗偺妱崬傒張棟偑峴傢傟傞傛偆偵側傝傑偟偨丅

仠僥僗僩拞偺奺儗僕僗僞偺俴俤俢昞帵偱偡

塃抂偺俙儗僕僗僞偩偗偼崅懍偱僀儞僋儕儊儞僩偟偰偄傑偡偐傜丄慡揰摂偟偰偄傞傛偆偵尒偊傑偡丅

偦偺懠偺丄俢丄俤丄俛丄俠丄俫丄俴偺奺儗僕僗僞偼俬俶俿怣崋偑擖椡偝傟傞偨傃偵丄俼俽俿侾乣俼俽俿俇偺偄偢傟偐偑幚峴偝傟丄偦偺偲偒偵奩摉偡傞儗僕僗僞偑亄侾偝傟傑偡丅

仠俬俶俿怣崋偺怣崋暆偵偮偄偰

忋偺僥僗僩偱尒偨傛偆偵俬俶俿怣崋偺暆偑梋傝挿偄偲丄暋悢夞丄妱崬傒偑敪惗偟偰偟傑偄傑偡丅

媡偵梋傝抁偄偲丄柍帇偝傟偰偟傑偭偰丄妱崬傒偑庴偗晅偗傜傟傑偣傫丅

偳偺埵偺暆偑偁傞偲傛偄偺偱偟傚偆偐丠

偦偺嵟戝暆偼丄妱崬傒傪棙梡偡傞僔僗僥儉偵傛偭偰堎側偭偰偒傑偡丅

嵟彫暆偺傎偆偼丄彮側偔偲傕嵟挿偺柦椷偺幚峴帪娫埲忋偱偁傞昁梫偑偁傝傑偡丅

乽偮偔傞俠俹倀乿偱偼丄嵟挿偺柦椷偼丄俽俫俴俢柦椷丄俴俫俴俢柦椷乮乵戞侾侽係夞乶乯偺俀侽僋儘僢僋偱偡丅侾僋儘僢僋偼侽丏俆兪倱倕們偱偡偐傜丄偦偺俀侽攞偼侾侽兪倱倕們偵側傝傑偡丅

偟偨偑偭偰丄嵟掅偱傕侾侽兪倱倕們埲忋偺娫偼俬俶俿怣崋傪傾僋僥傿僽偵偟偰偍偔昁梫偑偁傝傑偡丅

傑偁俀侽乣俁侽兪倱倕們偖傜偄偺怣崋暆偑懨摉側偲偙傠側偺偱偼側偄偱偟傚偆偐丅

仠儊僀儞儖乕僠儞偺張棟拞偵妱崬傒偑擖偭偰偄傞條巕偱偡

乮偙偺崁偼侽俋丏俇丏侾侽偵捛壛偟傑偟偨乯

偣偭偐偔儊僀儞儖乕僠儞偱俬乛俷夞楬偐傜僷儖僗傪弌椡偡傞傛偆偵僾儘僌儔儉偟偨偺偱偡偐傜丄偦偺條巕傕偍尒偣偡傞偙偲偵抳偟傑偟偨丅

忋乮俠俫侾乯偑俬俶俿怣崋偱偡丅嵍偺曽偵億僣儞偲偐偡偐偵尒偊偰偄傑偡丅

僷儖僗暆偑俀侽兪倱倕們傎偳偱偡偐傜丄偙偺儗儞僕偱偼偙偺掱搙偵偟偐尒偊傑偣傫丅

壓乮俠俫俀乯偼俬乛俷乮傾僪儗僗俋俉偺價僢僩係乯偐傜偺弌椡僷儖僗偱偡丅

崱夞偺妱崬傒張棟僾儘僌儔儉偼儗僕僗僞傪僀儞僋儕儊儞僩偟偰儕僞乕儞偡傞偩偗偺丄旕忢偵抁偄儖乕僠儞偱偡偐傜丄儊僀儞僾儘僌儔儉偺幚峴偵偼傎偲傫偳塭嬁傪梌偊傑偣傫丅

俀侽侽俋丏俇丏俋倳倫倢倧倎倓

俀侽侽俋丏俇丏侾侽捛婰

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞