前回の回路図を見て、

本当にこれでいいのか?

この回路図はひょっとするとデタラメではないのか?

などと、あらぬ疑いを抱いてしまわれた方がいらっしゃるといけませんから、蛇足とは思いつつ、念には念を入れて、もう少し、補足説明をいたします。

OPコード(命令コード)レジスタ74HC373の接続端子名がばらばらではないか?

データバス回路の74HC245の端子名は逆順ではないの?

確かに、その通りです。

74HC373の端子接続は、OP0−D0、OP1−D1、…のようには全然なっていません。デタラメです。

74HC245の接続も、外部データバスのD0がA8に、D1がA7に、というように全く逆の並びに接続されています。

こんなデタラメなつなぎ方でいいのか?

余りよろしくはないのですけれど、こんな接続でかまいません。

なにも好き好んでわざとひとを惑わす配線をしているのではありません。

ICの配置の関係で、こういうような配線になってしまうことがあります。

74HC373、74HC245、74HC244など8ビットのデータを扱うICにはD0〜D7を意味する端子名がついています。しかしそれは入力と出力とを結びつけるための番号でしかありませんから、どの端子にどのデータラインをつないでもまったく支障はありません。

しかし、入力端子とそれに対応する出力端子は、同じラインナンバーにつながなければいけません。わかりますね?

iB0のラインを74HC373のD4につないでも全く支障はありませんが、その代わり、対応する出力端子Q4にはOP0をつながなければいけません。

じつは74HC373がこんなデタラメな端子接続になってしまったのには、わけがあります。

実際の配線図で説明いたします。

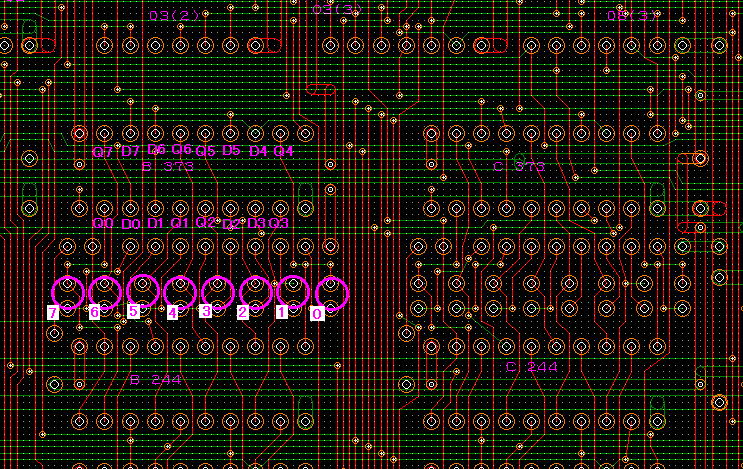

「つくるCPU」組立キットの試作基板の配線図の一部です。

レジスタBとレジスタCの部分です。

レジスタBとレジスタCはほぼ同じレイアウトで同じ配線になっています。

上側の20pinのICが74HC373(8ビットレジスタ)で下の20pinのICが74HC244(8ビットバスバッファ)です。

74HC373と74HC244の間にあるのは、レジスタの中身データを表示するLEDです。8個あります。

わかりやすくするために、BレジスタのLEDにピンクで○をつけて、ビット0からビット7までを番号で示しました。

またBレジスタの74HC373には、端子名を書き入れました。

74HC373は図のように入力端子が2個ずつ並んで配置されています。

74HC373のデータ出力Q0〜Q7は、それぞれLEDにつないだあと、74HC244に接続します。

図のようにLEDは左から7、6、5…のように配置してあります(8ビットのデータはこのように、ビット0を右側にして表現することが一般的です)。

このLEDの並び順と74HC373の端子の並び順は逆になっています。むりにあわせようとすると、横方向に余計な配線が増えてしまいます。

74HC373とLEDをそこそこ無理無く配線するようにしたところ、回路図のような配線になってしまいました。

●s0〜s3、d0〜d3(レジスタアドレス)

前回の回路図でアドレスバス回路の右側にあった、s0〜s3、d0〜d3は、レジスタを選択するためのアドレス信号線です。

8080にはたくさんのレジスタが使われています。

MOV命令やINR、DCRやその他のいろいろな命令でレジスタを指定するのに、OPコードの一部に3ビットのレジスタアドレスを埋め込んで、命令コードを解読すると同時に、レジスタも特定できるような工夫がされています。

たとえばMOV命令のOPコード(命令コード)は、

01dddsss

です。dddはデータを受け取る側のレジスタアドレスで、000〜111の8通りがあります。

sssはデータを送る側のレジスタのアドレスで同じように000〜111の8通りがあります。

dddとsssはデータの受け手と送り手を示すために、OPコードの中でこのように別々に配置されていますが、dddとsssが別々のルールで別のレジスタを指定しているわけではありません。

たとえば、000はBレジスタを示し、001はCレジスタを示します。

sssに000を指定してもdddに000を指定しても、それはデータの送り手であるか、受け手であるかが異なるだけで、同じBレジスタを示していることに変わりはありません。

01001000

という命令コードは、Bレジスタ(000)からCレジスタ(001)へデータを送る(move)命令であることを意味しています。

このように、レジスタを示すのに3ビットの信号、s0〜s2、d0〜d2が使われますが、「つくるCPU」組立キットの回路では、これにさらに1ビットs3、d3を追加して、その他の特殊なレジスタも指定する工夫をしました。

参考までに、s0〜s3またはd0〜d3によってアクセスされるレジスタの一覧表を下に示します。

「レジスタコード表」