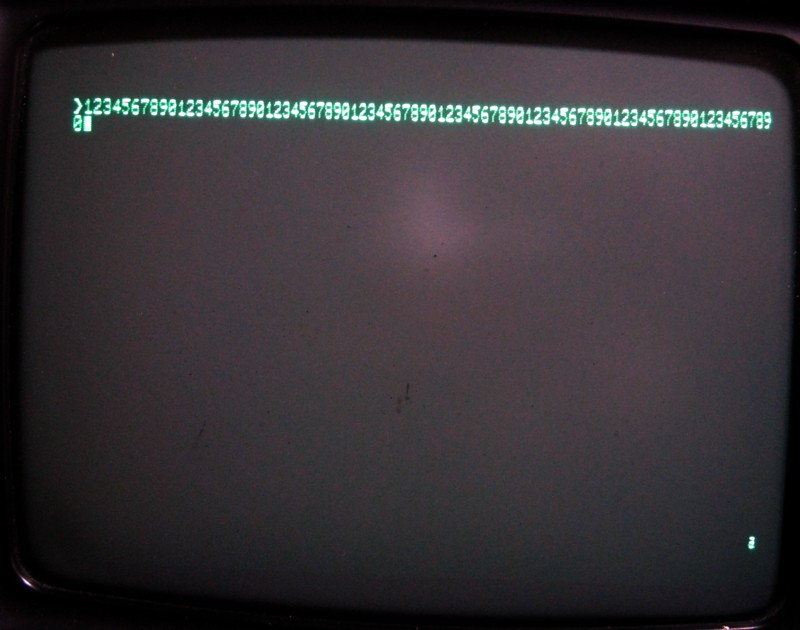

●”0111000”の写真です

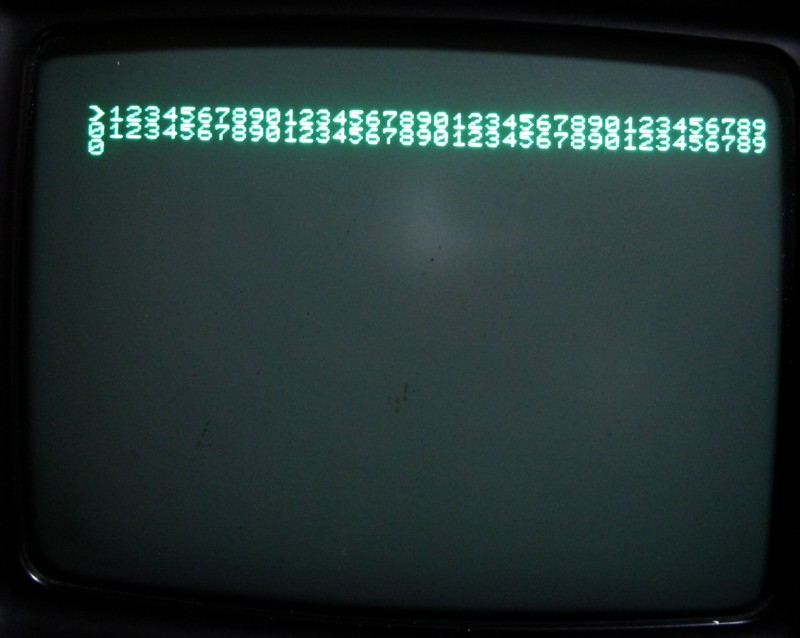

前回の終わりにお見せした写真は、−−cntr2 の40字表示のところ(elsif SW80_40=’0’ and cntr2=”0110111” then のところ)でのcntr2の波形です。

それだけでは、プログラムの記述が”0110111”でよいのか、”0111000”にすべきではないのか、というあたりの判別ができないことに気がつきましたので、elsif SW80_40=’0’ and cntr2=”0111000” then にして、cntr2の出力をオシロで観測してみました。

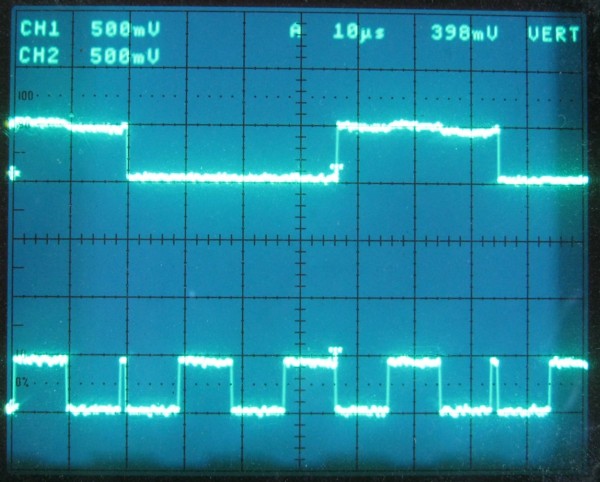

下はその写真です。

上(CH1)がcntr2(5)で下(CH2)がcntr2(3)です。

cntr2のビット5〜ビット3が”000”から”110”までカウントアップして、”111”になってから”000”になる様子が確認できます。

[第61回]に書きましたように、”111”であることが確認できるのは”111”になってから1クロック後です。

そのためプログラムのelsifの記述を”0111000”にすると、そのことが確認できるのは実際には”0111001”のときなので、上の写真のように1クロック遅れてcntr2がクリアされます。

写真ではcntr2(3)に幅の狭いパルスが見えます。

その後でcntr2(5)がLになっています。

CNTR2(5)〜(3)が”111”になったあと1クロック後にcntr2がクリアされたことが推測できます。

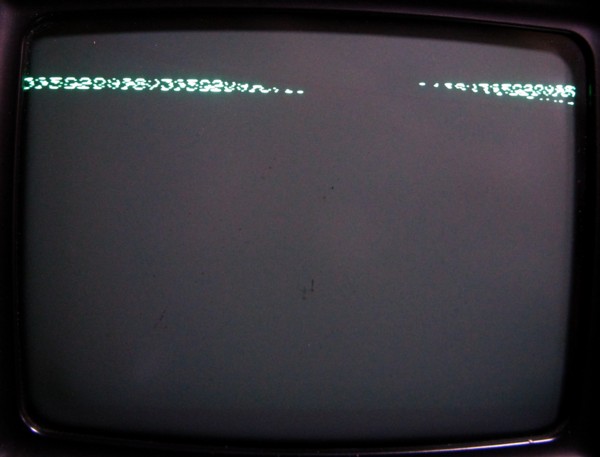

たった1文字分の遅れなのですが、それ以後の回路の動作に影響してしまうため、まともな表示にはなりません(下の写真)。

以上のことから、プログラムの記述は”0111000”ではなくて、それよりも1クロック前の”0110111”にしなければならないことが確認できました。

ぴったり理屈通りですので、納得です。

●そのほかの修正箇所(2)

前回に続いて直していただいたそのほかの修正箇所です。

−−ramadrs のところなのですが、ここは何回も書いていますように、考え方がちょっと複雑で、そのためVHDLプログラムの記述もちょっと複雑な書き方になっています。

ですからここに手を入れるのはちょっと難しいなあと思っていました。

下は修正前のプログラムです。