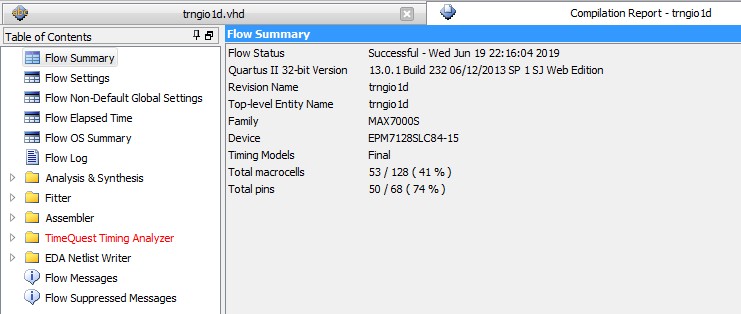

--cpld training i/o interface 82c55

--19/5/25 5/26 6/14 6/15 6/16 6/18 6/19

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library ARITHMETIC;

use ARITHMETIC.std_logic_arith.all;

entity trngio1d is

PORT (

LEDOUT:out std_logic_vector(3 downto 0);

ADRSIN:in std_logic_vector(7 downto 0);

DINOUT:inout std_logic_vector(7 downto 0);

PA:inout std_logic_vector(7 downto 0);

PB:inout std_logic_vector(7 downto 0);

PCL:inout std_logic_vector(3 downto 0);

PCH:inout std_logic_vector(3 downto 0);

IOR:in std_logic;

IOW:in std_logic);

end trngio1d;

architecture rtl of trngio1d is

signal ainout:std_logic;

signal binout:std_logic;

signal clinout:std_logic;

signal chinout:std_logic;

signal paout:std_logic_vector(7 downto 0);

signal pbout:std_logic_vector(7 downto 0);

signal pclout:std_logic_vector(3 downto 0);

signal pchout:std_logic_vector(3 downto 0);

--

begin

LEDOUT<="0000";

--82c55 address F0,F1,F2,F3

-- in out set

process(IOW)

begin

if IOW='0' then

if ADRSIN="11110011" and DINOUT(7 downto 5)="100" and DINOUT(2)='0' then

clinout<=DINOUT(0);-- '0' out,'1' in

binout<=DINOUT(1);

chinout<=DINOUT(3);

ainout<=DINOUT(4);

end if;

end if;

end process;

--

--out data PORTA,PORTB

process(IOW)

begin

if IOW='0' then

if ADRSIN="11110000" and ainout='0' then

paout<=DINOUT;

elsif ADRSIN="11110001" and binout='0' then

pbout<=DINOUT;

end if;

end if;

end process;

--

--portA out

process(ainout,paout)

begin

if ainout='0' then

PA<=paout;

else

PA<="ZZZZZZZZ";

end if;

end process;

--portB out

process(binout,pbout)

begin

if binout='0' then

PB<=pbout;

else

PB<="ZZZZZZZZ";

end if;

end process;

--

-- out data PORTC

process(IOW)

begin

if IOW='0' then

if ADRSIN="11110010" then

if chinout='0' then

pchout<=DINOUT(7 downto 4);

end if;

if clinout='0' then

pclout<=DINOUT(3 downto 0);

end if;

-- bit out

elsif ADRSIN="11110011" and DINOUT(7)='0' then

if clinout='0' then

if DINOUT(3 downto 1)="000" then

pclout(0)<=DINOUT(0);

elsif DINOUT(3 downto 1)="001" then

pclout(1)<=DINOUT(0);

elsif DINOUT(3 downto 1)="010" then

pclout(2)<=DINOUT(0);

elsif DINOUT(3 downto 1)="011" then

pclout(3)<=DINOUT(0);

end if;

end if;

if chinout='0' then

if DINOUT(3 downto 1)="100" then

pchout(0)<=DINOUT(0);

elsif DINOUT(3 downto 1)="101" then

pchout(1)<=DINOUT(0);

elsif DINOUT(3 downto 1)="110" then

pchout(2)<=DINOUT(0);

elsif DINOUT(3 downto 1)="111" then

pchout(3)<=DINOUT(0);

end if;

end if;

end if;

end if;

end process;

--

--portCL out

process(clinout,pclout)

begin

if clinout='0' then

PCL<=pclout;

else

PCL<="ZZZZ";

end if;

end process;

--portCH out

process(chinout,pchout)

begin

if chinout='0' then

PCH<=pchout;

else

PCH<="ZZZZ";

end if;

end process;

--

--in data from port

process(IOR)

begin

if IOR='0' then

if ADRSIN="11110000" then

if ainout='1' then

DINOUT<=PA;

else

DINOUT<=paout;

end if;

elsif ADRSIN="11110001" then

if binout='1' then

DINOUT<=PB;

else

DINOUT<=pbout;

end if;

elsif ADRSIN="11110010" then

if chinout='1' then

DINOUT(7 downto 4)<=PCH;

else

DINOUT(7 downto 4)<=pchout;

end if;

if clinout='1' then

DINOUT(3 downto 0)<=PCL;

else

DINOUT(3 downto 0)<=pclout;

end if;

else

DINOUT<="ZZZZZZZZ";

end if;

else

DINOUT<="ZZZZZZZZ";

end if;

end process;

--

end rtl;

|