俠俹乛俵偑俿俲亅俉侽屳姺偺儚儞儃乕僪儅僀僐儞偺忋偱暅妶偟傑偡

俶俢俉侽倅嘨偲俵倄俠俹倀俉侽偺忋偱俠俹乛俵偑憱傝傑偡両

乵戞俀俉俇夞乶

仠儘僕傾僫偱偲傜偊偨傾僪儗僗僙僢僩偺岆摦嶌攇宍

慜夞愢柧傪偄偨偟傑偟偨丄倅俉侽偱捛壛偝傟偨柦椷偑尨場偱敪惗偟偨丄俤亅俉侽乮壖徧乯儈僯僐儞偺傾僪儗僗僙僢僩乮俼俤俙俢憖嶌乯偱幚嵺偵岆摦嶌偟偰偄傞條巕傪儘僕傾僫偱娤應偄偨偟傑偟偨丅

崱夞偼偦偺婰榐攇宍傪偍尒偣偟傑偡丅

側偍偙偙偱巊偄傑偟偨儘僕傾僫偵偮偒傑偟偰偼乽俿俿俴偩偗偱俠俹倀傪偮偔傠偆乵戞俁俈係夞乶乿偱偛徯夘偄偨偟傑偟偨丅

挻儘乕僐僗僩偱偡偖傟傕偺偺儘僕傾僫乮僇儊儗僆儞倀俽俛亄儘僕傾僫僉僢僩乯偱偡丅

儘僕傾僫偺僾儘乕僽傪愙懕偟偰娤應傪偍偙側偭偨怣崋偼乵戞俀俈俇夞乶偲摨偠偱偡丅

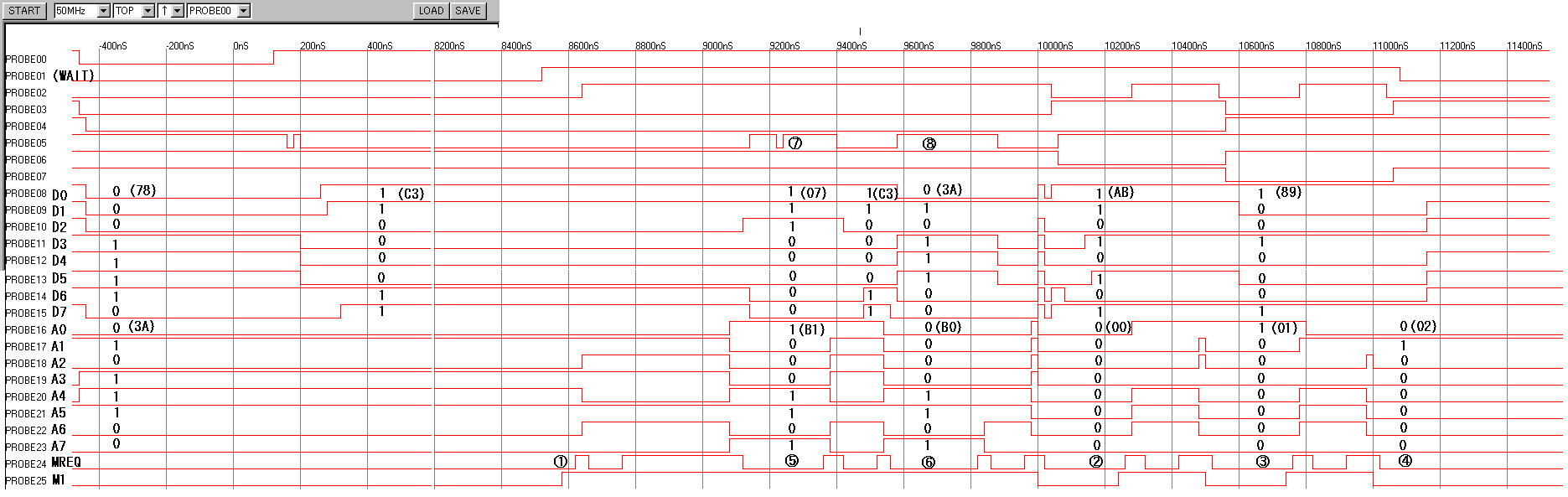

壓恾偼偦偺偲偒偵偍尒偣偟偨丄僾儘乕僽偺愙懕億僀儞僩傪僾儘僢僩偟偨夞楬恾偱偡丅

偙偪傜偑岆摦嶌偟偰偄傞條巕傪偲傜偊偨攇宍偺婰榐偱偡丅

乵戞俀俈俇夞乶偱偍尒偣偟偨惓忢摦嶌偟偰偄傞偲偒偺攇宍偲斾傋偰傒偰偔偩偝偄丅

椉幰偺堘偄偑傛傝偼偭偒傝暘偐傞傛偆偵丄乵戞俀俈俇夞乶偺愢柧傪壓晘偒偵偟偰愢柧傪偡傞偙偲偵偄偨偟傑偡丅

傾僪儗僗僙僢僩亄儊儌儕儕乕僪偺憖嶌偼俼俤俙俢僗僀僢僠傪俷俶偵偡傞偙偲偱峴傢傟傑偡丅

俼俤俙俢僗僀僢僠偼拞揰暅婣幃乮倣倧倣倕値倲倎倢倷丅墴偟偰偄傞娫偩偗愙揰偑暵偠丄棧偡偲尦偵栠傞乯偺僗僀僢僠偱偡丅

偦偺僗僀僢僠怣崋偵傛偭偰俈係俫俠侾俀俁偐傜弌椡偝傟偨儚儞僔儑僢僩僷儖僗偵傛偭偰夞楬摦嶌偑僗僞乕僩偟傑偡丅

俈係俫俠侾俀俁偺俻弌椡偵儘僕傾僫偺僾儘乕僽侽侽傪愙懕偟丄偦偺棫偪忋偑傝傪應掕奐巒僩儕僈偲偟傑偟偨丅

俼俤俙俢僗僀僢僠傪俷俶偵偡傞慜偵丄俽俿俷俹僗僀僢僠傪俷俶偵偟偰俠俹倀傪俵侾偺僞僀儈儞僌乮柦椷俷俹僐乕僪撉傒崬傒乯偱僂僃僀僩偝偣偰偁傝傑偡丅

偦偺偲偒偺傾僪儗僗昞帵偼亊亊俁俙俫偱丄僨乕僞僶僗偵偼儊儌儕偺偦偺傾僪儗僗偺抣俈俉俫偑弌椡偝傟偰偄傑偡丅

偙偙偵偼傾僪儗僗偺忋埵俉價僢僩偼乮僾儘乕僽傪愙懕偟偰偄傑偣傫偺偱乯昞帵偝傟偰偄傑偣傫偑丄侽俈俁俙俫偱偁傞偙偲偑傢偐偭偰偄傑偡丅

崱傑偱偺偲偙傠偱偼僼儘儞僩僷僱儖偺憖嶌偵偮偄偰偟偐愢柧偟偰偒傑偣傫偱偟偨偑丄俤亅俉侽乮壖徧乯儈僯僐儞偼傕偭偲傕偭偲戝偒側婡擻傪傕偭偰偄偰丄摉婰帠偵愭峴偟偰偦偺婡擻偵偮偄偰偺奺庬摦嶌僥僗僩傕峴偭偰偍傝傑偡丅

幚偼尰嵼僨僶僢僌拞偺俤亅俉侽乮壖徧乯儈僯僐儞偺俼俙俵偵偼俶俢俉侽倅嘨乮俶俢俉侽倅俁丏俆乯偺俼俷俵偺拞恎偑偡偱偵堏怉嵪傒偵側偭偰偄傑偡丅

偱偡偺偱僷儚乕俷俶偟傑偡偲丄偦偺堏怉偟傑偟偨俶俢俉侽倅儌僯僞偑摦嶌偟偰丄倀俽俛愙懕懸偪偵側傝傑偡丅

偦偙偱偼埲壓偺僾儘僌儔儉偑幚峴偝傟傑偡丅