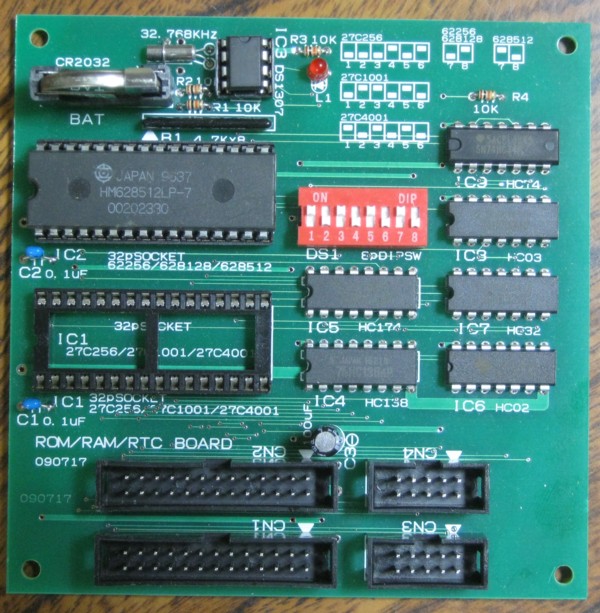

俼俷俵乛俼俙俵乛俼俿俠儃乕僪偺惢嶌

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

倂倝値倓倧倵倱僷僜僐儞偵倀俽俛愙懕偟偰巊偆尰峴曽幃偼偦傟側傝偵曋棙偱偼偁傝傑偡偑丄偲偒偲偟偰倂倝値倓倧倵倱

偺偟偑傜傒偐傜奐曻偝傟偰丄彫偝偄側偑傜傕撈棫偟偨堦屄偺僷僜僐儞偲偟偰婡擻偟偨偄偲巚偆偙偲傕偁傝傑偡丅

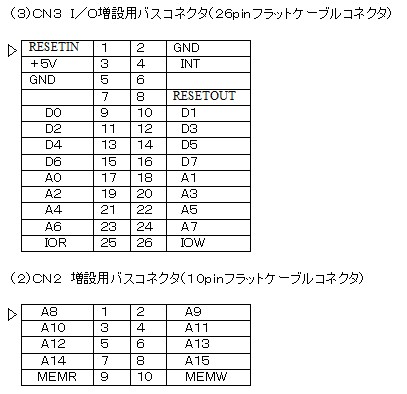

撈棫戝嶌愴偺嶌愴偦偺侾偼俠俼俿僀儞僞乕僼僃乕僗儃乕僪偺惢嶌偱偡丅

嶌愴偦偺俀偼僉乕儃乕僪僀儞僞乕僼僃乕僗偱偡丅

嶌愴偦偺俁偼丄俽俢僇乕僪僀儞僞乕僼僃乕僗偱偡丅

嶌愴偦偺係偼丄俼俷俵乛俼俙俵乛俼俿俠儃乕僪偱偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞俁俀夞乶

仠傑偨偟偰傕捝崷偺儈僗

乵戞俀俉夞乶偺嵟屻偺偲偙傠偱乽棊偲偟寠偑偁傝傑偟偨乿偲彂偒傑偟偨丅

乽棊偲偟寠乿側偳偲偄偄傑偡偲丄壗偩偐帺暘偼埆偔側偄偺偵扤偐偵偼傔傜傟偨丄偲偄偆傛偆側報徾偑偁傝傑偡偑丄慡慠偦傫側偙偲偼側偔偰丄偙傟偼傕偆帺暘偺晄拲堄偱帺暘偐傜棊偪偨偩偗偱偁傝傑偡丅

偳偆傕偙偺偲偙傠傛偔側偄偱偡偹偊丅

偮偄愭擔偺偙偲側偺偱偡偑丅

俼俙俵偺僥僗僩傕弴挷偵廔傝傑偟偰丄懕偄偰俼俷俵偺僥僗僩偵擖傞偲偄偆偲偒偵側偭偰丄俼俷俵丂倂俼俬俿俤俼傪愙懕偟偰偪傚偄偲偟偨僾儘僌儔儉傪彂偙偆偲偟傑偟偨傜丄側傫偩偐條巕偑偍偐偟偄偺偱偡丅

慜擔傑偱偼傑偲傕偵嶌嬈偱偒偰偄偨偺偵丄撍慠俼俷俵乛俼俙俵乛俼俿俠儃乕僪偵幚憰偟偰偄傞俼俙俵偺拞恎偑彂偒姺傢偭偰偟傑偄傑偡丅

幚偼丄偦傟傑偱偼俶俢俉侽倅嘨偵侾侽倫倝値僐僱僋僞婎斅傪奼挘偟偨傕偺傪巊偭偰丄偦偙偵俼俷俵乛俼俙俵乛俼俿俠儃乕僪傪愙懕偟偰嶌嬈傪偟偰偒偨偺偱偡偑丄偦偺偲偒偼偦傫側偙偲側偳偍偒傑偣傫偱偟偨丅

崱夞偼偨傑偨傑俶俢俉侽倅俁丏俆傪愙懕偟偰偺嶌嬈偱偡丅

側傫傜偐偺尨場偱俼俙俵偑攋懝偟偨偺偐丄偲傕巚偭偰擮偺偨傔偵俼俙俵傪岎姺偟偰傒傑偟偨偑丄徢忬偼曄傢傝傑偣傫偱偟偨丅

偳偙偑偳偺傛偆偵曄傢偭偰偟傑偆偺偐丄撍慠僨乕僞偑壔偗偰偟傑偆売強傪妋擣偟偰傒偰丄偦偙偵婯懃惈偑偁傞偙偲偑傢偐偭偰偒傑偟偨丅

偦偙偱傗偭偲丄俼俷俵乛俼俙俵乛俼俿俠儃乕僪偺夞楬偺儈僗偵婥偑晅偒傑偟偨丅

側傫偲傕傢傟側偑傜忣偗側偄捝崷偺儈僗偱偁傝傑偟偨丅

壓偼俼俷俵乛俼俙俵乛俼俿俠儃乕僪偺儊儌儕晹暘偺夞楬恾偱偡丅

恾偺拞偵乽俵俤俵俼俢乿乽俵俤俵倂俼乿偲偄偆怣崋偑偁傝傑偡丅

偙傟偑栤戣偩偭偨偺偱偟偨丅

偙偺怣崋偼俠俹倀儃乕僪偲愙懕偡傞偨傔偺侾侽倫倝値僐僱僋僞偺倫倝値俋丄倫倝値侾侽偵捈愙偮側偑偭偰偄傑偡丅

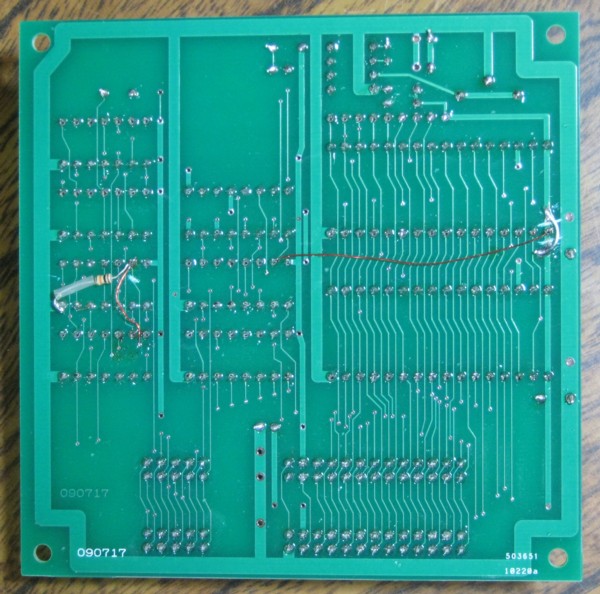

壓偼俶俢俉侽俉侽偺僐僱僋僞抂巕恾偱偡丅

俶俢俉侽倅嘨偵偼侾侽倫倝値僐僱僋僞偼偁傝傑偣傫偺偱丄屻偐傜僐僱僋僞婎斅傪憹愝偡傞傛偆偵峫偊傑偟偨丅

俶俢俉侽倅嘨梡偺僐僱僋僞憹愝婎斅偺侾侽倫倝値僐僱僋僞傕僐僱僋僞抂巕偼忋偺俶俢俉侽俉侽梡偲摨偠偱偡丅

偲偙傠偑丅

俶俢俉侽倅俁丏俆偩偗偼偦偙偺偲偙傠偑堘偭偰偄傞偲偄偆偙偲傪偆偭偐傝幐擮偟偰偟傑偭偰偍傝傑偟偨丅

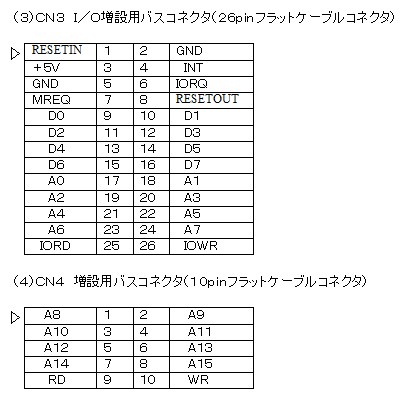

壓偼俶俢俉侽倅俁丏俆偺僐僱僋僞抂巕恾偱偡丅

俶俢俉侽倅俁丏俆偺応崌偵偼侾侽倫倝値僐僱僋僞偺倫倝値俋丄倫倝値侾侽偵偼俼俢丄倂俼偑攝抲偝傟偰偄傑偡丅

偙傟偼摉弶奜晹夞楬偺傎偆偱俵俼俤俻偲俼俢丄倂俼傪偁傢偣偰俵俤俵俼俢丄俵俤俵倂俼傪嶌傟偽傛偄丄偲峫偊偨偐傜偱偡丅

偦偺屻偵俶俢俉侽俉侽傪奐敪偡傞帪揰偱丄俉侽俉侽偱偼俠俹倀廃曈俴俽俬偵傛偭偰嵟弶偐傜俵俤俵俼丄俵俤俵倂偑弌椡偝傟傞偙偲偑傢偐偭偨偨傔偵丄侾侽倫倝値僐僱僋僞偵偼偦傟傪攝抲偟偨偺偱偟偨乮偦傟偲偼媡偵俵俼俤俻偼偁傝傑偣傫乯丅

俶俢俉侽倅嘨偺憹愝僐僱僋僞婎斅傕偦傟傪庴偗偰丄憹愝僐僱僋僞婎斅撪偱俵俤俵俼俢丄俵俤俵倂俼傪嶌偭偰偦傟傪攝抲偟傑偟偨丅

俠俼俿俬俥傪奐敪偡傞夁掱偱偼俶俢俉侽倅俁丏俆偲偦偺傎偐偺儃乕僪偲偺堘偄偵偮偄偰偼偪傖傫偲擣幆偟偰偄偨偺偱偡偗傟偳丅

偄偮偺傑偵偐丄俶俢俉侽倅俁丏俆偵偼俵俤俵俼俢丄俵俤俵倂俼偑弌偰偄側偄丄偲偄偆偙偲傪偡偭偐傝朰傟偰偟傑偄傑偟偨丅

偱丅

俶俢俉侽倅俁丏俆偵俼俷俵乛俼俙俵乛俼俿俠儃乕僪傪偮側偓傑偡偲丅

傆偮偆偺偲偒偼傛偄偺偱偡偑丄俼俷俵丂倂俼俬俿俤俼側偳俉俀俠俆俆傪惂屼偡傞偨傔偵俬乛俷偵懳偡傞俷倀俿丄俬俶柦椷傪幚峴偡傞偲丄俷倀俿柦椷偵傛偭偰乮俼俷俵乛俼俙俵乛俼俿俠儃乕僪偺乯俵俤俵倂俼偑傾僋僥傿僽偵側偭偰偟傑偄傑偡丅

偙偙偼壓偺夞楬偵偡傋偒偩偭偨偺偱偟偨丅

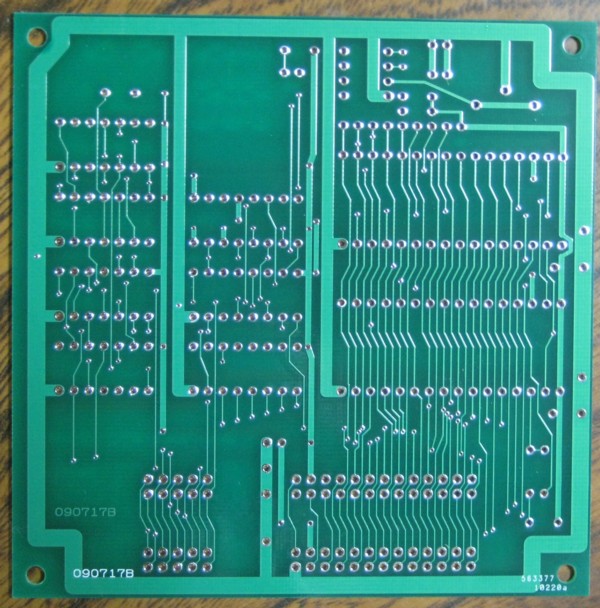

偦偺晹暘傪廋惓偟偨俼俷俵乛俼俙俵乛俼俿俠儃乕僪偺僐儞僩儘乕儖乛俼俿俠晹暘偺夞楬恾偱偡丅

俵俼俤俻偲俼俢丄倂俼偐傜俵俤俵俼俢丄俵俤俵倂俼傪嶌偭偰偄傑偡丅

俵俼俤俻偵僾儖僟僂儞掞峈偑偮偄偰偄傞偺偼丄偙偆偡傞偙偲偱俶俢俉侽俉侽偺傛偆偵俵俼俤俻偑側偔偰丄戙傢傝偵俵俤俵俼丄俵俤俵倂偑偁傞応崌偱傕俵俤俵俼俢丄俵俤俵倂俼偑惓偟偔弌椡偝傟傞傛偆偵偡傞偨傔偱偡丅

偣偭偐偔傔偱偨偔婎斅姰惉丄偺偼偢偱偟偨偺偵丅

捝崷偺儈僗偺偨傔偵傑偨傑偨嶌傝捈偟偱偡丅

嵍懁偑崱夞偺廋惓晹暘偱偡丅

塃懁偼愭偵攝慄儈僗傪尒偮偗偰廋惓嵪傒偺晹暘偱偡丅

忋偺塃懁偺晹暘傪廋惓偟偰弌棃忋偑偭偰偒偰偄偨婎斅偱偡丅

弌棃忋偑偭偰偒偨偽偐傝偺婎斅偱偡偺偵丄傑偨傑偨婎斅偺嶌傝捈偟偱偡丅

傎傫偲偆偵丄傗傟傗傟偱偡丅

傑丄偟偐偟丄傕偺偼峫偊傛偆偱丄偙偺偙偲偵婥偑晅偐偢偵惢昳偲偟偰弌偟偰偟傑偭偨傜丄偦傟偙偦乽傗傟傗傟乿偖傜偄偱偼嵪傑側偄偲偙傠偱偟偨丅

偦偆巚偊偽丄偙偙偱嬸抯側偳尵偭偰偼偄偗傑偣偸丅

擔乆惀姶幱偱偁傝傑偡丅

俼俷俵乛俼俙俵乛俼俿俠儃乕僪偺惢嶌乵戞俁俀夞乶

俀侽侾俈丏俋丏俀俀倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞