仠俠俹俴俢儘僕傾僫乮俇乯

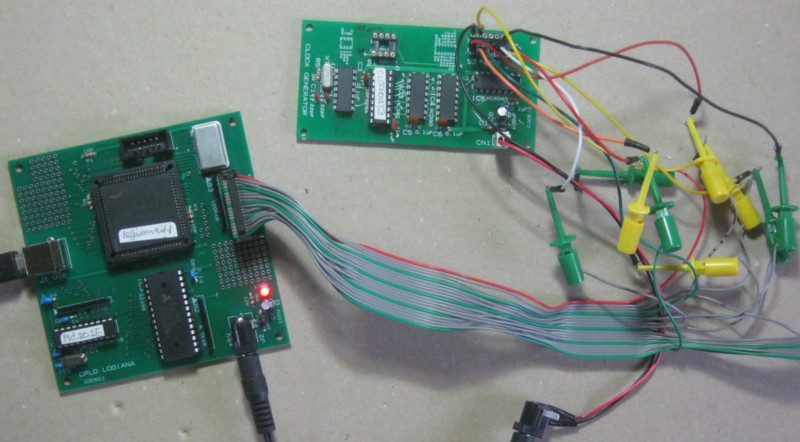

CPLD儘僕傾僫傪巊偭偰偄傞偲偙傠偼崱傑偱壗夞偐幨恀傪偍尒偣偟偰偄傑偡丅

崱傑偱偼俠俹倀儃乕僪側偳偺僋儘僢僋傪應掕偡傞偲偙傠側偳偱巊偄傑偟偨丅

崱夞偼俠俹俴俢儘僕傾僫偺婎杮揑側摦嶌傪妋擣偡傞偨傔偺摦嶌僥僗僩偱偡丅

僋儘僢僋傪應掕偡傞僞乕僎僢僩偲偟偰僋儘僢僋敪惗夞楬婎斅傪愙懕偟傑偟偨丅

僋儘僢僋敪惗夞楬婎斅偺弌椡廃攇悢偼崅偄傎偆偐傜係俵俫倸丄俀俵俫倸丄侾俵俫倸丄俆侽侽俲俫倸丄俀俆侽俲俫倸丄侾俀俆俲俫倸丄俇俀丏俆俲俫倸丄俁侾丏俀俆俲俫倸丄乧偱偡丅

傑偩壓偺廃攇悢傑偱弌椡怣崋偼偁傝傑偡偑俠俹俴俢儘僕傾僫偼俉僠儍儞僱儖側偺偱埲忋偺俉弌椡傪愙懕偟傑偡丅

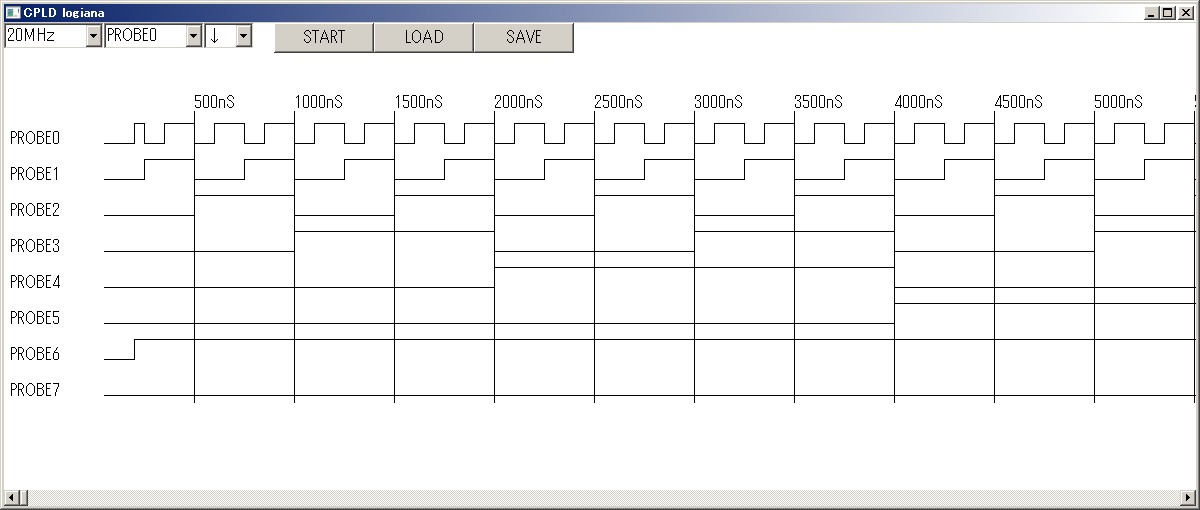

壓偼俠俹俴俢儘僕傾僫偲僋儘僢僋敪惗夞楬婎斅傪偦偺傛偆偵愙懕偟偰倂倝値倓倧倵倱僷僜僐儞偲倀俽俛愙懕偟偰僾儘僌儔儉傪幚峴偟偨寢壥昞帵偝傟偨夋柺偱偡丅

僒儞僾儕儞僌廃攇悢偼俀侽俵俫倸偱偡丅

俹俼俷俛俤侽偑係俵俫倸偱俹俼俷俛俤俈偑俁侾丏俀俆俲俫倸偱偡丅

係俵俫倸偺侾廃婜偼俀俆侽値倱偱偡丅

俀侽俵俫倸偱偼俆侽値倱偵侾夞僒儞僾儕儞僌偟傑偡丅

係俵俫倸偺応崌俴婜娫偲俫婜娫偑偦傟偧傟侾俀俆値倱側偺偱俆侽値倱偵侾夞僒儞僾儕儞僌偡傞偲俴婜娫偲俫婜娫偺偳偪傜偐偑抁偄攇宍偲偟偰昞帵偝傟偰偟傑偄傑偡丅

俀俵俫倸埲崀偺廃攇悢偱偼俆侽値倱偱妱傝愗傟傞偺偱偦偺傛偆側攇宍偵偼側傜偢偵僨儏乕僥傿斾俆侽亾偺偒傟偄側攇宍偵側傝傑偡丅

偲偙傠偱俹俼俷俛俤俁乮俆侽侽俲俫倸乯傑偱偼侾廃婜暘偺攇宍偑妋擣偱偒傑偡偑俹俼俷俛俤係偐傜壓偺攇宍偼晹暘偟偐昞帵偝傟傑偣傫偐傜侾廃婜慡懱偺攇宍傪尒傞偙偲偑偱偒傑偣傫丅

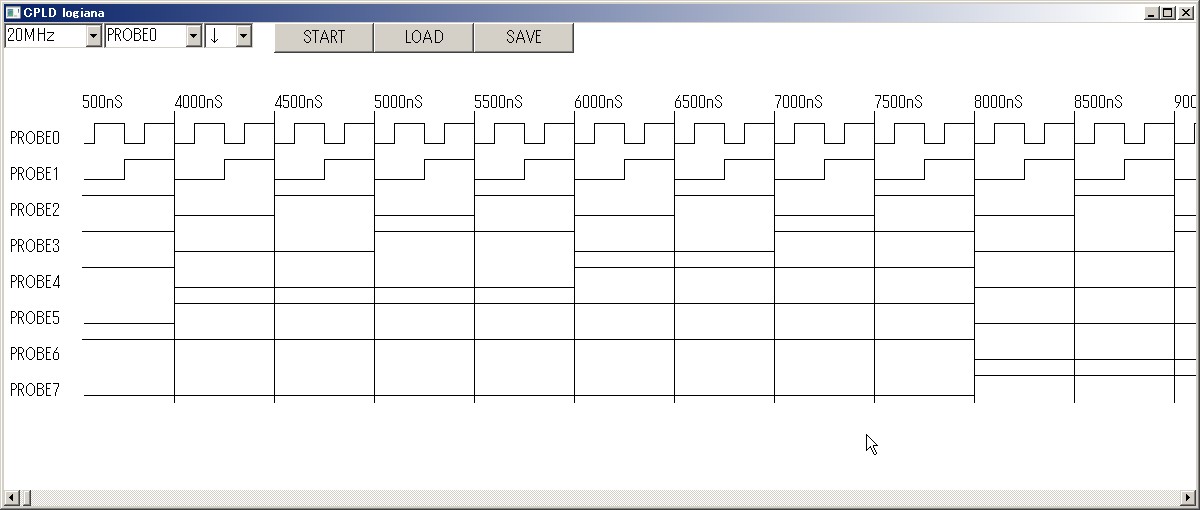

掅偄廃攇悢偺攇宍傪妋擣偡傞偵偼僒儞僾儕儞僌廃攇悢傪傕偭偲掅偄廃攇悢偵偡傟偽傛偄偺偱偡偑丄偦偆偟側偔偰傕偙偺傑傑偱妋擣偡傞偙偲偑偱偒傑偡丅

夋柺偺壓晹偺僗儔僀僪僶乕傪僗儔僀僪偝偣傞偙偲偱掅偄廃攇悢偺攇宍傕偦偺侾廃婜傪妋擣偡傞偙偲偑偱偒傑偡丅

僗儔僀僪僶乕傪彮偟偩偗塃偵僗儔僀僪偝偣傑偟偨丅

偝偒傎偳偺夋憸偱偼侾廃婜偺慡懱偑尒偊側偐偭偨俹俼俷俛俤係偺侾廃婜偑妋擣偱偒傑偟偨丅

偦偺傎偐偺廃攇悢偺攇宍偵偮偄偰傕摨偠傛偆偵僗儔僀僪僶乕傪僗儔僀僪偝偣傞偙偲偱攇宍偺慡懱傪妋擣偡傞偙偲偑偱偒傑偡丅

傑偩愢柧偺搑拞側偺偱偡偑杮擔偼帪娫偑側偔側偭偰偟傑偄傑偟偨丅

懕偒偼師夞偵彂偔偙偲偵偄偨偟傑偡丅

杮擔偼戝夾擔偱偡丅

偲偆偲偆傑偨堦擭偑廔偭偰偟傑偄傑偟偨丅

傗傠偆偲巚偭偰偄偨偙偲偺敿暘傕偱偒側偄傑傑偵夁偓偰偟傑偭偨堦擭偱偟偨丅

棃擭偙偦偼傕偆彮偟側傫偲偐偱偒傞堦擭偵偟偨偄偲巚偄傑偡丅

偙偺堦擭愘暥偵偍晅偒崌偄偄偨偩偒桳擄偆偛偞偄傑偟偨丅

棃擭傕傛傠偟偔偍婅偄偄偨偟傑偡丅

奆條傛偄偍擭傪偍寎偊偔偩偝偄丅

俠俹俴俢擖栧両乵戞侾侾俇夞乶

俀侽俀侾丏侾俀丏俁侾倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞