乵怴楢嵹乶俠俹俴俢擖栧両

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

偄偮偐巊偆偙偲偵側傞偩傠偆偲巚偭偰偼偄偨偺偱偡偑丅

壗傪崱崰偵側偭偰丄偲偄偆傛偆側傕偺偱偡偑丅

傛偆傗偔杮婥偱丄俠俹俴俢偲巐偮偵庢傝慻傒傑偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞侾侾俉夞乶

仠俠俹俴俢儘僕傾僫乮俉乯俙俽俇俠俇俀俀俆俇

俠俹俴俢儘僕傾僫偼僒儞僾儕儞僌僋儘僢僋偵傛偭偰僾儘乕僽擖椡傪儔僢僠偟偰偦傟傪偦偺傑傑俼俙俵偵僨乕僞偲偟偰彂偒崬傒傑偡丅

俇俀俀俆俇俼俙俵偺梕検偼俉價僢僩亊俁俀俈俇俉偱偡偐傜俉僠儍儞僱儖偺僾儘乕僾擖椡怣崋傪偦偺傑傑俉價僢僩偺僨乕僞偲偟偰俇俀俀俆俇偵彂偒崬傓偙偲偱俁俀俈俇俉夞暘偺擖椡儔僢僠僨乕僞傪婰榐偡傞偙偲偑偱偒傑偡丅

俼俙俵偺梕検偼屌掕側偺偱僒儞僾儕儞僌僋儘僢僋偑曄傢偭偰傕婰榐偱偒傞僨乕僞検偼堦掕偱曄傢傝傑偣傫丅

僋儘僢僋偑懍偗傟偽侾夞偺僒儞僾儕儞僌僨乕僞傪俼俙俵偵彂偒崬傓懍搙傕懍偔側傝傑偡丅

偙偙偱栤戣偵側傞偺偼嵟崅懍偺僒儞僾儕儞僌僋儘僢僋俀侽俵俫倸偺応崌偺僨乕僞彂偒崬傒懍搙偱偡丅

嵟弶偺帋嶌斉偼俼俙俵偲偟偰俬俽俇侾俠俆侾俀俉乮俆侾俀俲俛乯傪幚憰偟傑偟偨丅

俬俽俇侾俠俆侾俀俉傪慖戰偟偨偺偼尰嵼偱傕晛捠偵擖庤壜擻偱偐側傝偺儊儌儕梕検偱偁傞偙偲偑偦偺棟桼偱偟偨丅

俶俢俉侽俲俴乛俉俇梡偵巊偭偰偄傞俬俽俇侾俠俆侾俀俉偼傾僋僙僗僞僀儉偑俀俆値倱側偺偱僒儞僾儕儞僌僋儘僢僋偑俀侽俵俫倸偱傕梋桾偱娫偵崌偄傑偡丅

偟偐偟帋嶌傪廳偹偰偄偔偆偪偵偦傟傎偳偺梕検偼側偔偰傕傛偄偺偱偼側偄偐偲峫偊傞傛偆偵側傝傑偟偨丅

寢嬊俶俢俉侽倅俁丏俆傗俶俢俉侽俉侽側偳偱巊偭偰偄傞俇俀俀俆俇俼俙俵偵棊偪拝偒傑偟偨丅

偦偺偁偨傝偺偙偲偵偮偄偰偼慜夞偱傕愢柧傪偟傑偟偨丅

俆侾俀俲俛偺俼俙俵偐傜俁俀俲俛偺俼俙俵傊偺曄峏偼梕検偺傒傪峫偊偰偟偨偙偲偱丄偦偺帪揰偱偼俼俙俵偺傾僋僙僗僞僀儉偵偮偄偰偼峫偊偰偄傑偣傫偱偟偨丅

幚嵺俇俀俀俆俇傪幚憰偡傞傛偆偵愝寁曄峏偟偨帋嶌斉偑偱偒偰偒偨偲偒偵偦傟埲慜偐傜偺棳傟偱晛捠偵俀侽俵俫倸偺僒儞僾儕儞僌僋儘僢僋偱僥僗僩偟偨偺偱偡偑栤戣側偔摦嶌偟偨偺偱偦傟偱偄偄偲巚偭偰偟傑偄傑偟偨丅

媣偟怳傝偵俠俹俴俢儘僕傾僫偵偮偄偰彂偄偰偄偔側偐偱丄杮摉偵俀侽俵俫倸偱戝忎晇偐丄偲偄偆偙偲偑傆偲婥偵側傝傑偟偨丅

偦偙偱俇俀俀俆俇偺傾僋僙僗僞僀儉偵偮偄偰妋擣偟偰傒傑偟偨丅

崱夞俠俹俴俢儘僕傾僫偵巊偆偙偲偵偟偨俼俙俵偼俙俽俇俠俇俀俀俆俇偱偡丅

偁傜偨傔偰僨乕僞僔乕僩偱妋擣偟偰傒傑偟偨傜傾僋僙僗僞僀儉偼俆俆値倱偱偟偨丅

乵弌揟乶丂俙倢倢倝倎値們倕丂俵倕倣倧倰倷丆俬値們丏丂俙俽俇俠俇俀俀俆俇丂俢倎倲倎丂俽倛倕倕倲

愄巊偭偰偄偨擔棫偺俫俵俇俀俀俆俇側偳偵斾傋偨傜偐側傝崅懍偱偡丅

偟偐偟偦傟偱傕俆俆値倱偱偼僒儞僾儕儞僌僋儘僢僋俀侽俵俫倸偵偼巊偊側偄偺偱偼丠

俀侽俵俫倸偺侾廃婜偼俆侽値倱偱偡丅

堄幆偟偰偄側偐偭偨偗傟偳偙傟偼偪傚偭偲傑偢偄偺偱偼丅

栤戣偼僒儞僾儕儞僌僨乕僞傪俼俙俵偵彂偒崬傓偲偒偺懍搙偱偡丅

婰榐偟偨僨乕僞傪俼俙俵偐傜撉傒弌偡偲偒偼偦傟傛傝偼偆傫偲抶偄懍搙偱撉傒弌偟傑偡偐傜栤戣偼偁傝傑偣傫丅

俼俙俵偵僨乕僞傪彂偒崬傓偲偒偺懍搙偱堦斣栤戣偵側傞偺偼僒僀僋儖僞僀儉偲倂俼僷儖僗偺暆偱偡丅

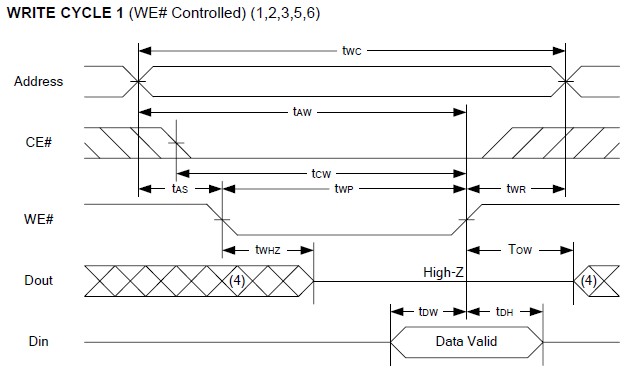

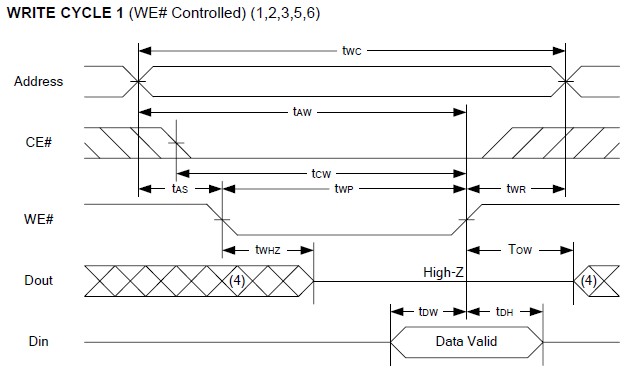

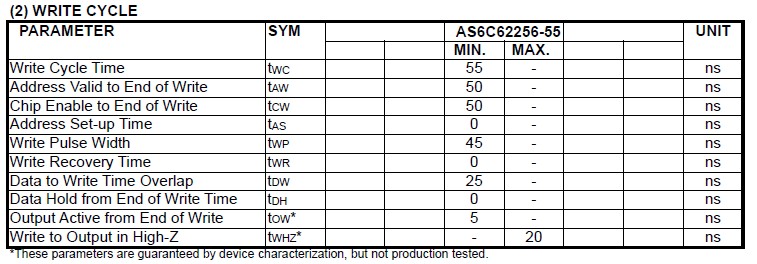

偙偙偱俙俽俇俠俇俀俀俆俇偺僨乕僞僔乕僩偺抣偲斾妑偡傞偨傔丄僒儞僾儕儞僌僋儘僢僋偵摨婜偟偰俠俹俴俢偐傜弌椡偝傟傞俵俤俵倂俼僷儖僗偵偮偄偰愢柧傪偟偰偍偒傑偡丅

俠俹俴俢儘僕傾僫偺倁俫俢俴僾儘僌儔儉偱俵俤俵倂俼偵偮偄偰婰弎偟偰偄傞偺偼壓偺晹暘偱偡丅

--MEMWR

--

MWR<=cntrL(2) or r_w or cntrH(15);--MWR_=cntrL(2)='0' and r_w='0'

--

|

們値倲倰俴乮俀乯偑偦偺傑傑俵俤俵倂俼怣崋偲偟偰弌椡偝傟傑偡乮倰丵倵偲們値倲倰俫乮侾俆乯偼應掕婜娫拞偱偁傞偙偲傪帵偡撪晹怣崋偱偡乯丅

偦偺們値倲倰俴偼俁價僢僩偺僇僂儞僞偱偡丅

壓偑們値倲倰俴偵偮偄偰婰弎偟偰偄傞僾儘僌儔儉晹暘偱偡丅

process(clkwk2,res_clr)

begin

if res_clr='0' then

cntrL<="000";

elsif clkwk2'event and clkwk2='0' then

if cntrL="100" then

cntrL<="000";

else

cntrL<=cntrL+"001";

end if;

end if;

end process;

|

們値倲倰俴偼們倢倠倵倠俀偺壓偑傝僄僢僕偵傛偭偰僇僂儞僩傾僢僾偟傑偡丅

偦偟偰偦偺偲偒偵們値倲倰俴偺抣偑乭侾侽侽乭偩偭偨側傜偽偦偙偱們値倲倰俴傪僋儕傾偟偰乭侽侽侽乭偵僙僢僩偟傑偡丅

壓偼偦傟傪恾偱帵偟偨傕偺偱偡丅

們倢倠倵倠俀偵偼偦偺偲偒慖戰偟偰偄傞僒儞僾儕儞僌僋儘僢僋偵懳墳偡傞廃攇悢偺僋儘僢僋偑擖傝傑偡偑偙偙偱偼僒儞僾儕儞僌僋儘僢僋偑俀侽俵俫倸偺偲偒偵偮偄偰彂偄偰偄傑偡偺偱丄偦偺偲偒偺們倢倠倵倠俀偼侾侽侽俵俫倸偱偡乮僾儘僌儔儉偺暿偺偲偙傠偱婰弎偟偰偄傑偡乯丅

們値倲倰俴偼們倢倠倵倠俀偺壓偑傝僄僢僕偱僋儘僢僋傾僢僾偟傑偡丅

尩枾偵偄偆偲們値倲倰俴偼們倢倠倵倠俀偺壓偑傝僄僢僕偲摨帪偱偼側偔偰偦偺捈屻偺僞僀儈儞僌偱僋儘僢僋傾僢僾偟傑偡偐傜丄們値倲倰俴偑僋儕傾偝傟傞偺偼們値倲倰俴偑乭侾侽侽乭偵側偭偨弖娫偱偼側偔偰偦傟傛傝傕們倢倠倵倠俀偺侾僋儘僢僋暘抶傟偨偲偒偵側傝傑偡丅

偦偺們値倲倰俴乮俀乯偑偦偺傑傑俵俤俵倂俼怣崋偲偟偰俠俹俴俢偐傜弌椡偝傟傑偡丅

偦偺僷儖僗暆偼俴婜娫偑係侽値倱偱俫婜娫偑侾侽値倱偵側傝傑偡丅

側偍傑偨暿偺僾儘僌儔儉晹暘偱們値倲倰俴乮俀乯偺忋偑傝僄僢僕偵摨婜偟偰俼俙俵偺儊儌儕傾僪儗僗偑僇僂儞僩傾僢僾偝傟傑偡丅

恾偺堦斣壓偵俠俹俴俢偐傜俼俙俵偵弌椡偝傟傞儊儌儕傾僪儗僗偺俙侽偺攇宍傪帵偟傑偟偨丅

傑偨恾偱偼徣棯偟傑偟偨偑丄偙傟偲摨偠僞僀儈儞僌偱僾儘乕僽擖椡傪儔僢僠偟偰偦傟傪偦偺傑傑僨乕僞偲偟偰俼俙俵偵弌椡偟傑偡丅

壓偼俙俽俇俠俇俀俀俆俇偺倂俼俬俿俤怣崋偺僞僀儈儞僌恾偱偡丅

乵弌揟乶丂俙倢倢倝倎値們倕丂俵倕倣倧倰倷丆俬値們丏丂俙俽俇俠俇俀俀俆俇丂俢倎倲倎丂俽倛倕倕倲

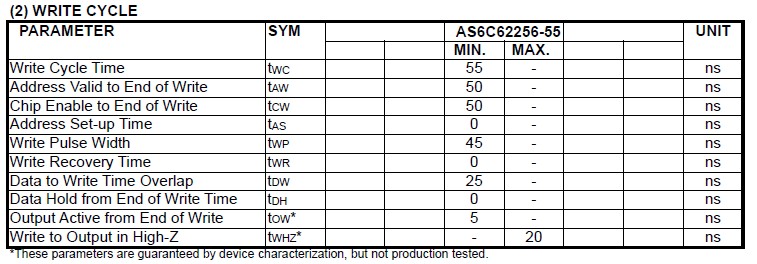

恾拞偺僷儔儊乕僞偵偮偄偰偼壓偺昞偵傑偲傔傜傟偰偄傑偡丅

乵弌揟乶丂俙倢倢倝倎値們倕丂俵倕倣倧倰倷丆俬値們丏丂俙俽俇俠俇俀俀俆俇丂俢倎倲倎丂俽倛倕倕倲

俿倂俠偼僒僀僋儖僞僀儉偱偡丅

俠俹俴俢儘僕傾僫偱偼僒儞僾儕儞僌僞僀儉俀侽俵俫倸偺偲偒偺僒僀僋儖僞僀儉偼俆侽値倱偱偡偐傜婯掕抣傛傝傕俆値倱抁偄抣偵側傝傑偡丅

俿倂俹偑倂俼俬俿俤怣崋暆偱偡丅

儘僕傾僫偱偼係侽値倱偱偡偐傜偙傟傕婯掕抣偵俆値倱懌傝傑偣傫丅

偍偦傜偔儊乕僇乕偼儚乕僗僩働乕僗傪憐掕偟偰忋婰偺傛偆側婯掕抣傪愝掕偟偰偄傞偼偢偲億僕僥傿僽偵峫偊傟偽俆値倱偖傜偄偼側傫偲偐僋儕傾偟偰偔傟傞偺偱偼偲婜懸偟偨偄偲偙傠偱偡丅

帠幚丄忋偵彂偒傑偟偨傛偆偵崱偺偲偙傠俀侽俵俫倸偱傕摿偵彂偒崬傒僄儔乕偼偍偒偰偄側偄傛偆偱偡丅

偦傟偲偙偺俼俙俵偼俀丏俈倁乣俆丏俆倁偺峀偄揹埑斖埻偱摦嶌偟傑偡乮崱夞偺嵟弶偵偍尒偣偟偨僨乕僞僔乕僩偺拞偵偦偺婰嵹偑偁傝傑偡乯丅

偦偙偵偼揹棳抣偲偟偰倁們們亖俁倁偺偲偒偺抣傪帵偟偰偄傑偡丅

偦偺偙偲偐傜椶悇偡傟偽倂俼俬俿俤僒僀僋儖偺婯掕抣傕倁們們亖俁倁偺偲偒偺抣偱偼側偄偐偲峫偊偰傕娫堘偄偱偼側偄傛偆偵巚偊傑偡丅

堦斒偵俠俹倀偱傕儊儌儕偱傕倁們們傪崅偔偡傟偽傛傝崅懍摦嶌偑壜擻偵側傞偲峫偊傜傟傑偡丅

偦偺傛偆偵峫偊傟偽倁們們亖俁倁偱偼俆俆値倱丄係俆値倱偑嵟彫抣偩偭偨偲偟偰傕倁們們亖俆倁側傜偽偦傟傛傝偼傕偆彮偟梋桾偑弌偰偒偰傕傛偄偼偢偲巚偄傑偡丅

偟偐偟偦傟偼偁偔傑偱婓朷揑偵峫偊偨偙偲側偺偱丄摉俠俹俴俢儘僕傾僫偵偮偄偰偼僒儞僾儕儞僌僋儘僢僋俀侽俵俫倸偼偲傝偁偊偢乽偍傑偗乿偱偁傞偲峫偊偰偔偩偝偄丅

俠俹俴俢擖栧両乵戞侾侾俉夞乶

俀侽俀俀丏侾丏俈倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞