[新連載]CPLD入門!

〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

いつか使うことになるだろうと思ってはいたのですが。

何を今頃になって、というようなものですが。

ようやく本気で、CPLDと四つに取り組みます。

〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

[第139回]

●CPLDロジアナ(28)サンプリングクロックの下限を広げました

今納期が迫った仕事に追われています。

落ち着いて書いているだけの時間がなかなか取れません。

本日はほんの少しだけ書いて終ります。

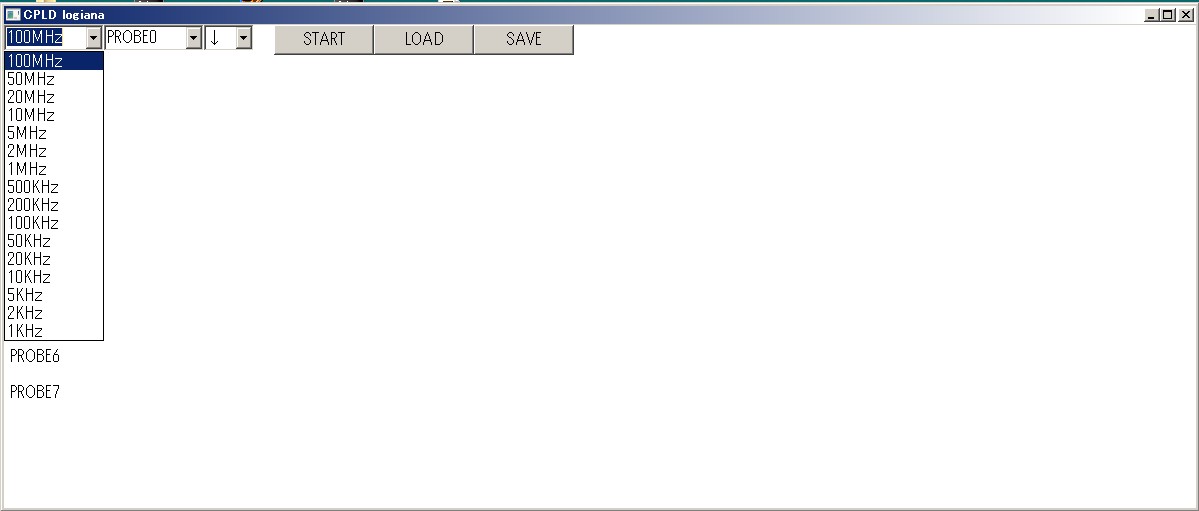

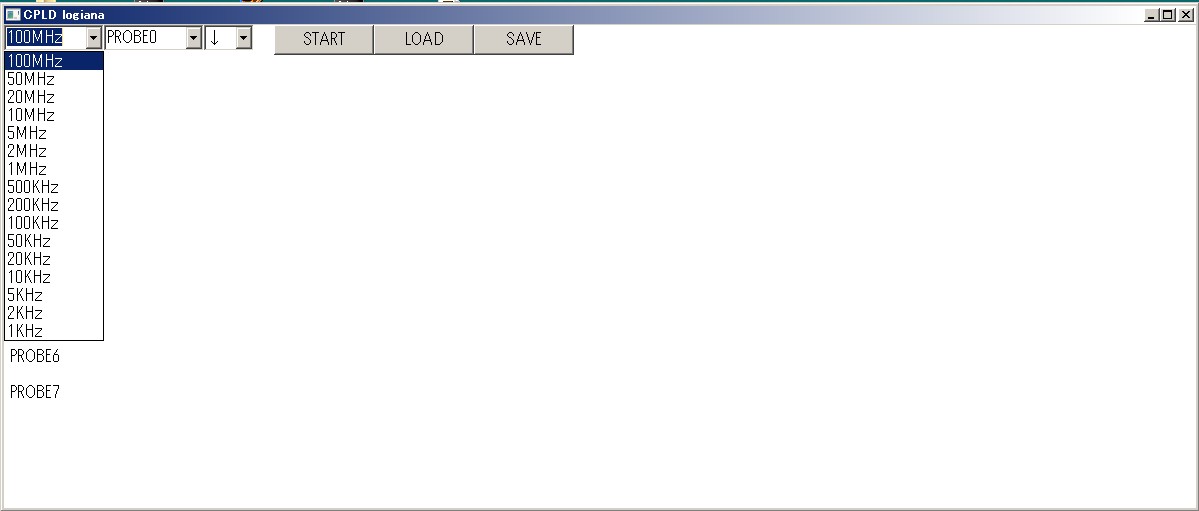

CPLDロジアナのサンプリングクロックは100MHz〜500KHzの8通りのクロックですと説明してきました。

下限クロックは500KHzです。

それより低いクロックを必要とすることはあまり無いのでは、と適当に判断したためです。

使えるクロックの幅を広げるとCPLDのマクロセルが不足してしまうのでは、とも考えてキリのよいところで8通りにしました。

CPLDロジアナに使っているのはEPM7128でマクロセルは128個です。

ところが[第133回]に書きましたように、実際にプログラムを書いてみると意外に少なくて済んでしまいました。

そういうことならもう少し範囲を広げてもよかったか、と思いました。

たまたまちょっと測ってみたいものがでてきて、それを測るにはもっと低いサンプリングクロックが必要ということがわかりました。

何を測りたいと思ったのかということについては、本日は時間がありませんので次回あたりに書くことにします。

とにかく。

そのように考えてサンプリングクロックを倍に増やしました。

100MHzから1KHzまでをカバーできます。

これなら十分と言えますでしょう。

当然のこととしてVHDLプログラムも大幅に追加することになりました。

下が今回の変更によって追加したプログラム部分です。

--

--make clk200kwk for 200kHz

--clk200kwk(3)=1mhz

--

process(clk2m)

begin

if clk2m'event and clk2m='0' then

if clk200kwk="1001" then

clk200kwk<="0000";

else

clk200kwk<=clk200kwk+"0001";

end if;

end if;

end process;

--

--make clk200kwk2

--clk200kwk2(0)=500khz clk200kwk2(1)=250khz

--

clk200k<=clk200kwk(3);--1mhz

--

process(clk200k)

begin

if clk200k'event and clk200k='0' then

clk200kwk2<=clk200kwk2+"01";--100k,50k

end if;

end process;

--

--make clk20kwk for 20kHz

--clk20kwk(3)=100khz

--

process(clk200k)

begin

if clk200k'event and clk200k='0' then

if clk20kwk="1001" then

clk20kwk<="0000";

else

clk20kwk<=clk20kwk+"0001";

end if;

end if;

end process;

--

--make clk20kwk2

--clk20kwk2(0)=50khz clk20kwk2(1)=25khz

--

clk20k<=clk20kwk(3);--100khz

--

process(clk20k)

begin

if clk20k'event and clk20k='0' then

clk20kwk2<=clk20kwk2+"01";--10k,5k

end if;

end process;

--

--make clk2kwk for 2kHz

--clk2kwk(3)=10khz

--

process(clk20k)

begin

if clk20k'event and clk20k='0' then

if clk2kwk="1001" then

clk2kwk<="0000";

else

clk2kwk<=clk2kwk+"0001";

end if;

end if;

end process;

--

--make clk2kwk2

--clk2kwk2(0)=5khz

--

clk2k<=clk2kwk(3);--10khz

--

process(clk2k)

begin

if clk2k'event and clk2k='0' then

clk2kwk2<=clk2kwk2+'1';--1k

end if;

end process;

--

-- select clock

--

clkwk2<=CLK when clkslct<="0010" else --20MHz

clkwk(0) when clkslct="0011" else --10MHz

clkwk(1) when clkslct="0100" else --5MHz

clk2m when clkslct="0101" else --2MHz

clk2mwk2(0) when clkslct="0110" else --1MHz

clk2mwk2(1) when clkslct="0111" else --500KHz

clk200k when clkslct="1000" else --200kHz

clk200kwk2(0) when clkslct="1001" else --100kHz

clk200kwk2(1) when clkslct="1010" else --50KHz

clk20k when clkslct="1011" else --20kHz

clk20kwk2(0) when clkslct="1100" else --10kHz

clk20kwk2(1) when clkslct="1101" else --5KHz

clk2k when clkslct="1110" else --2kHz

clk2kwk2 when clkslct="1111" else --1kHz

'1';

--

|

[訂正]22.3.10

上記プログラムに1箇所ミスがありました。

下から27行目が

clk2K<=clk20kwk(3);--10khz

になっていました。

上記リストは訂正済みです。

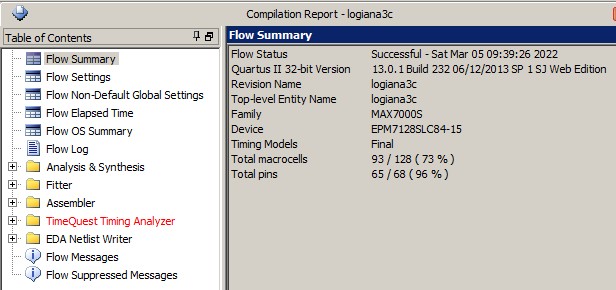

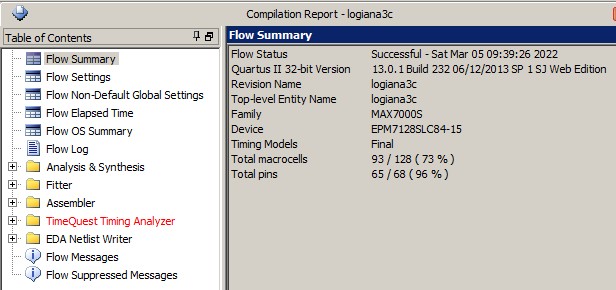

下は上の部分を追加した新しいVHDLプログラムをコンパイルした結果です。

[第133回]では128個のマクロセルのうち75個しか使っていません(59%)でしたがさすがに今回は使用数が増えて93個(73%)になりました。

CPLD入門![第139回]

2022.3.6upload

前へ

次へ

ホームページトップへ戻る