乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

偄偮偐巊偆偙偲偵側傞偩傠偆偲巚偭偰偼偄偨偺偱偡偑丅

壗傪崱崰偵側偭偰丄偲偄偆傛偆側傕偺偱偡偑丅

傛偆傗偔杮婥偱丄俠俹俴俢偲巐偮偵庢傝慻傒傑偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞俀俋夞乶

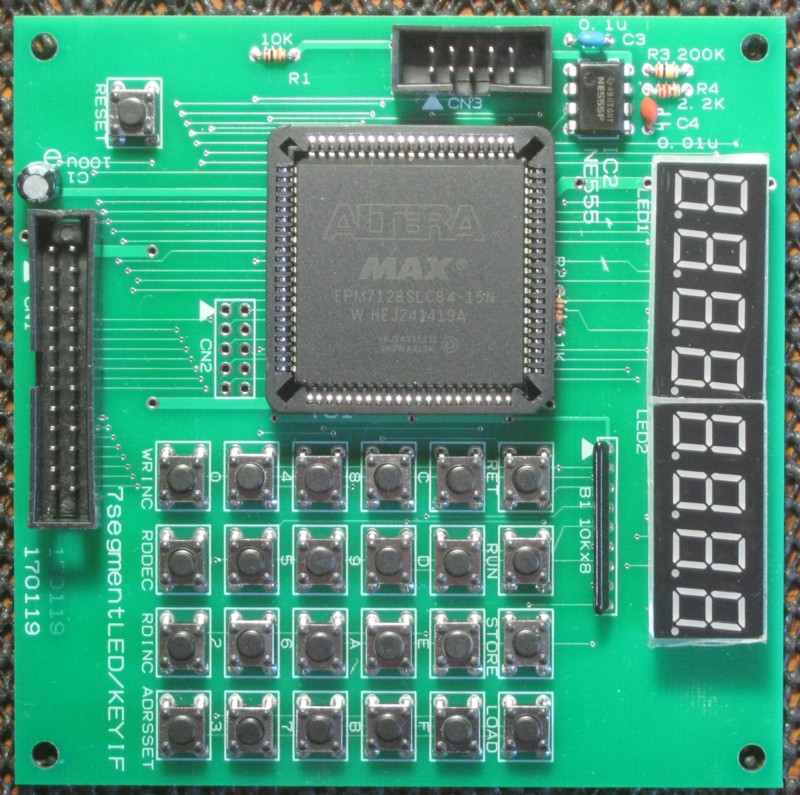

仠俈僙僌儊儞僩俴俤俢亄俆亊俆僉乕儃乕僪夞楬乮俀乯

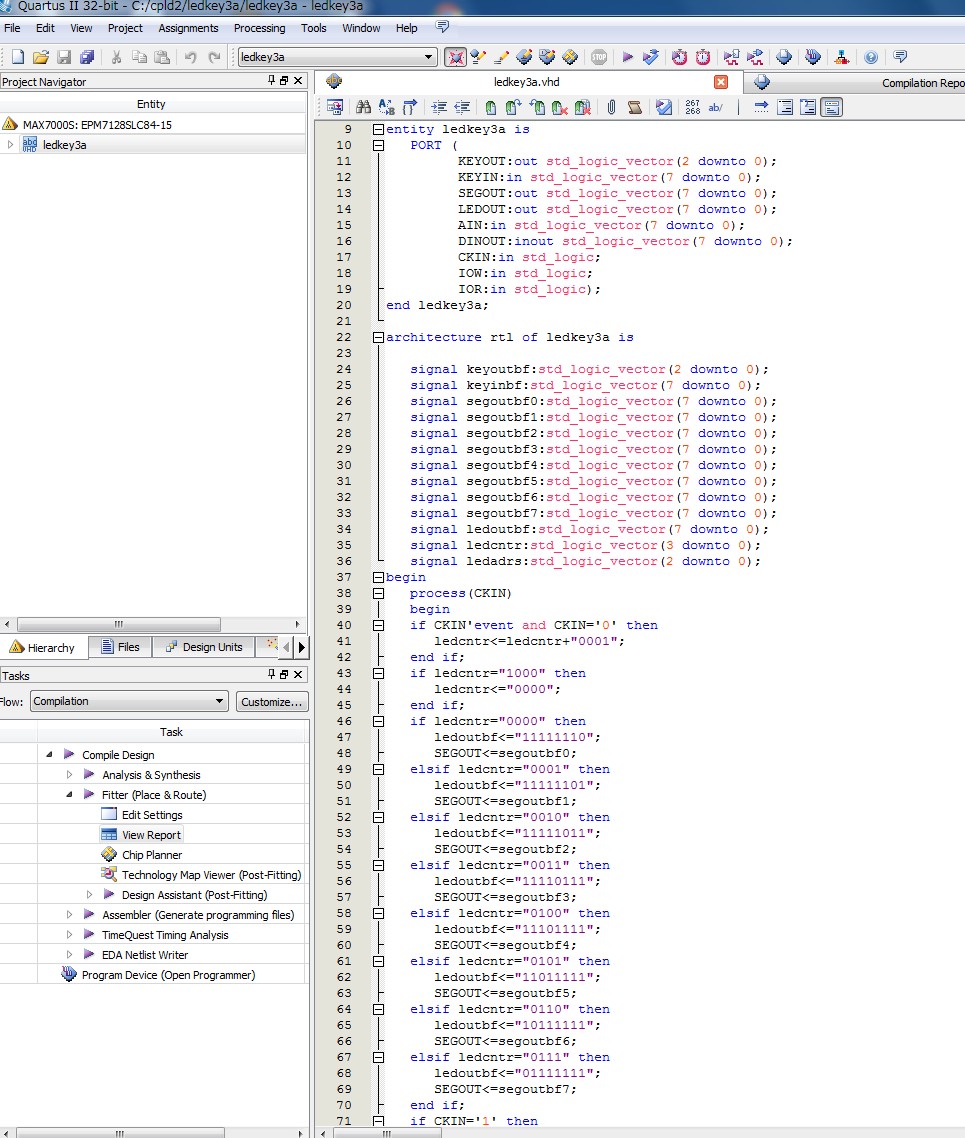

慜夞偺夞楬傪傕偲偵偟偰丄偲傝偁偊偢嶌偭偰偟傑偭偨帋嶌婎斅偱偡丅

偱偒傞偩偗儘乕僐僗僩偵側傞傛偆偵偲偄偆僐儞僙僾僩偐傜丄俈僙僌儊儞僩俴俤俢偼彫宆偺係寘昞帵僞僀僾傪巊偄丄僉乕傕彫宆偺僞僋僩僗僀僢僠傪巊偄傑偟偨丅

僉乕偼戝宆偱僉乕僩僢僾偵傾僋儕儖僉儍僢僾偑偮偄偰偄偰僔乕儖偑擖傟傜傟傞傕偺偑巊偄堈偄偺偱偡偑丄僐僗僩偑慡慠堘偄傑偡丅

俶俢俉侽倅俁丏俆偵巊偭偰偄傞僉乕偼崅偄偺偱偡丅

偦偆偄偆僉乕偵斾傋傞偲巊偄偵偔偄偺偼帠幚偱偡偑丄偙偺僉乕偲俴俤俢傪巊偭偰僨乕僞側偳傪擖椡偟偨傝丄儅僔儞岅儌僯僞婡擻傪巊偆偲偄偆傛偆側巊偄曽偼偦傟傎偳昿斏偱偼側偄偲巚偄傑偡偐傜丄偙偙偼僐僗僩傪桪愭偵峫偊傑偟偨丅

倁俫俢俴僾儘僌儔儉偼僾儕儞僩婎斅偑弌棃忋偑偭偰偔傞傛傝傕慜偵嶌偭偰偟傑偄傑偟偨丅

峴斣崋俀俇乣俁俁偱俉寘暘偺俴俤俢僙僌儊儞僩僶僢僼傽傪掕媊偟偰偄傑偡丅

俶俢俉侽倅俁丏俆偱偼俼俙俵忋偵抲偄偰偄傞俉僶僀僩偺僶僢僼傽偱偡丅

峴斣崋係侽乣俇俋偱偼俆俆俆偐傜偺僷儖僗傪擖椡偡傞偛偲偵寘僇僂儞僞傪僀儞僋儕儊儞僩偟偰丄偦偺抣傪傕偲偵偟偰俉寘偺俴俤俢傪僟僀僫儈僢僋僪儔僀僽昞帵偡傞偨傔偺怣崋弌椡傪峴側偭偰偄傑偡丅

偙傟偩偗偱傕彮側偔偲傕俉亊侾俇亄係亖侾侽侽屄偺儔僢僠乮俥俥丄僼儕僢僾僼儘僢僾乯傪徚旓偟偰偟傑偆偼偢側偺偱丄偙偺帪揰偱偙傟偼偐側傝偒傃偟偄偙偲偵側傝偦偆偲偄偆梊憐偼摉慠偟偰偄傑偟偨丅

偱傕傑偁偙偙傑偱偒偨偐傜偵偼丄傗偭偰傒傞偟偐偁傝傑偣傫丅

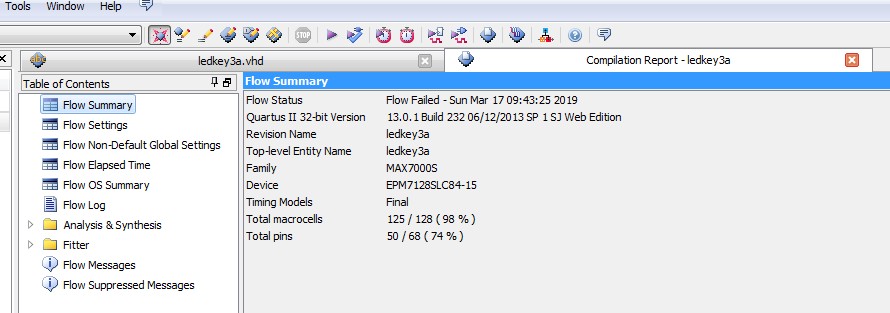

傑傑傛偲巚偭偰僐儞僷僀儖偟偰傒傑偟偨丅

寢壥偼偓傝偓傝僙乕僼偱偁傝傑偟偨丅

俵倎們倰倧俠倕倢倢偺巊梡棪偼俋俉亾偱偡丅

傕偭偲傕偙傟偩偗偱廔傢傝偱偼偁傝傑偣傫丅

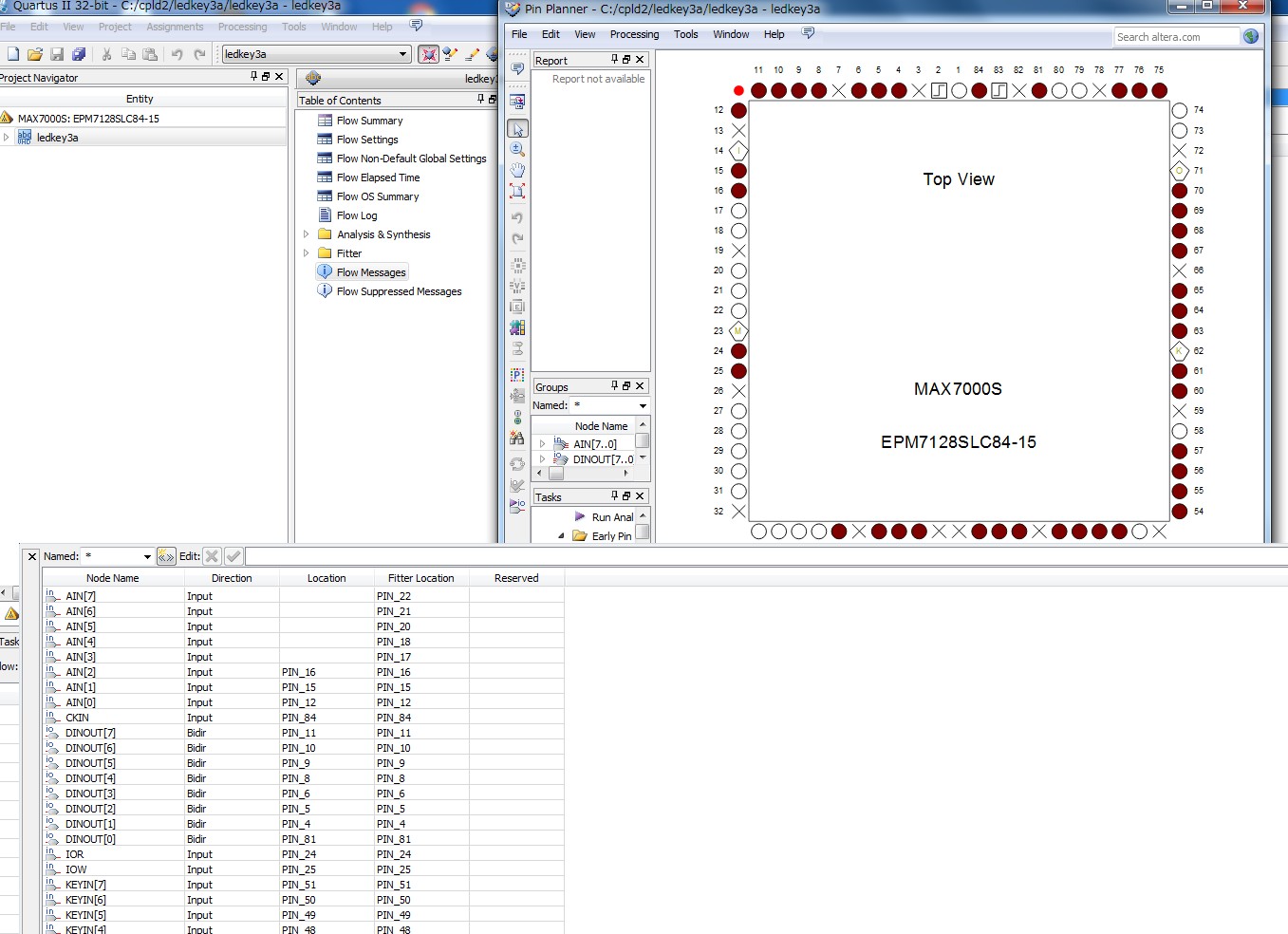

幚嵺偵奜晹擖弌椡怣崋傪俤俹俵俈侾俀俉俽俴俠俉係偺擖弌椡抂巕偵妱傝摉偰傞昁梫偑偁傝傑偡丅

俻倳倎倰倲倳倱嘦偱偼俹倝値丂俹倢倎値値倕倰偲偄偆僣乕儖傪巊偄傑偡丅

偲傝偁偊偢偞偭偲妱傝摉偰傑偟偨丅

僺儞傪妱傝摉偰偨傜傕偆堦搙僐儞僷僀儖偟傑偡丅

偱丅

傕偆堦搙僐儞僷僀儖偟傑偟偨傜丅

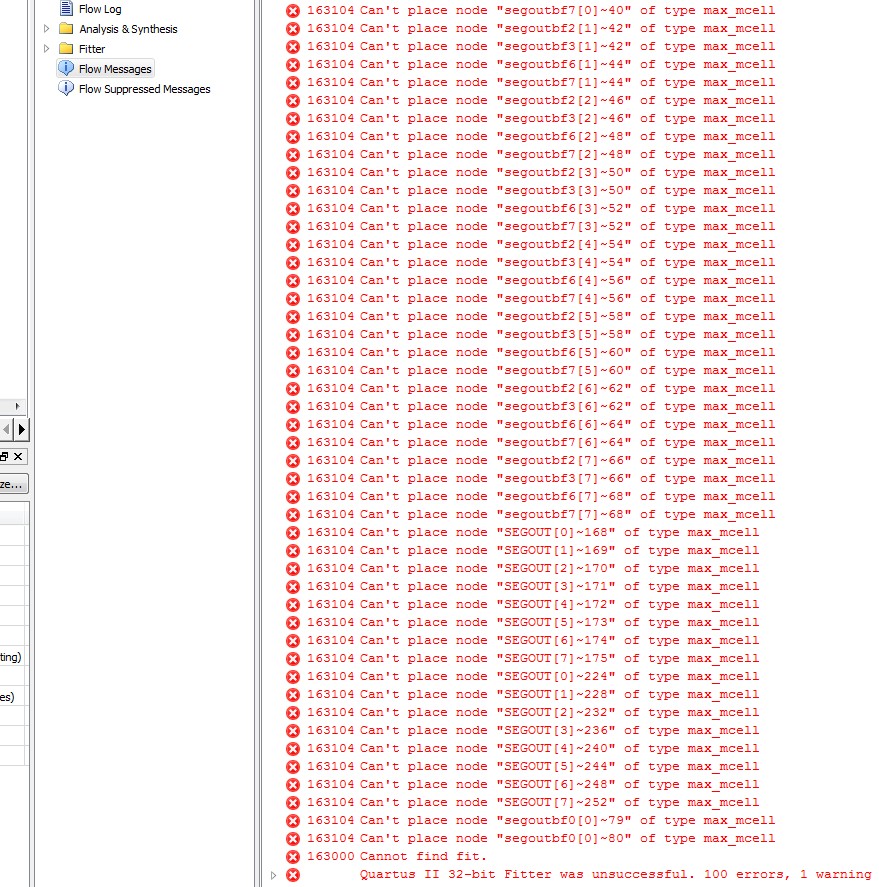

側傫偠傖丄偙傝傖偁両両

傃偭偔傝嬄揤偲偼偙偺偙偲偱偡丅

僺儞傪妱傝摉偰傞慜偵偼僄儔乕側偔僐儞僷僀儖偑姰椆偟偨偺偵丄僺儞傪妱傝摉偰偰偐傜嵞僐儞僷僀儖偟偨偲偙傠丄側傫偲丄傇傢偀偭偲偛棗偺捠傝堄枴晄柧偺僄儔乕儊僢僙乕僕偑嶳傎偳弌偰偟傑偄傑偟偨丅

俠俹俴俢擖栧両乵戞俀俋夞乶

俀侽侾俋丏係丏俀倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞