乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

偄偮偐巊偆偙偲偵側傞偩傠偆偲巚偭偰偼偄偨偺偱偡偑丅

壗傪崱崰偵側偭偰丄偲偄偆傛偆側傕偺偱偡偑丅

傛偆傗偔杮婥偱丄俠俹俴俢偲巐偮偵庢傝慻傒傑偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞俈夞乶

仠俵俙倃俈侽侽侽偺僨乕僞僔乕僩

慜夞偼俤俹俵俈侽俁俀俽俴俠係係偺幚暔偺幨恀傪偍尒偣偟傑偟偨丅

崱夞偼僨乕僞僔乕僩傪娙扨偵偛徯夘偟傑偡丅

慜夞彂偒傑偟偨傛偆偵俤俹俵俈侽俁俀俽俴俠係係偼俙俴俿俤俼俙偺俵俙倃俈侽侽侽僔儕乕僘偺嵟壓埵僨僶僀僗偱偡丅

乵弌揟乶俙俴俿俤俼俙丂俵俙倃俈侽侽侽丂俢倎倲倎丂俽倛倕倕倲

巆擮側偑傜俵俙倃俈侽侽侽僔儕乕僘偼尰嵼偱偼惗嶻廔椆偵側偭偰偟傑偄傑偟偨丅

偙偺僨乕僞僔乕僩偼侾侽擭埲忋慜偺擔晅偵側偭偰偄傑偡丅

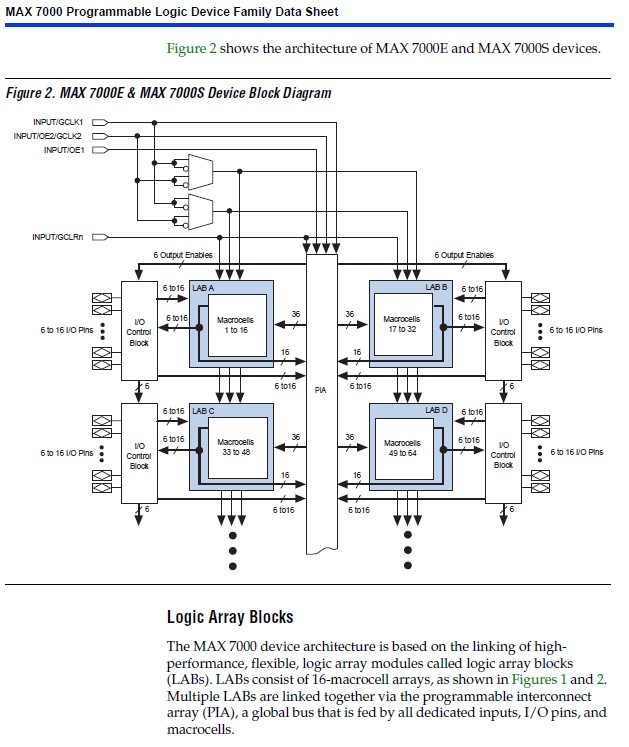

忋婰俥倕倎倲倳倰倕倱偱拲栚偟偨偄偺偼乽俆丏侽倁乿偲偄偆偙偲偲乽俰俿俙俧乿婡擻晅偒偱偁傞偲偄偆偲偙傠偱偡丅

偙偪傜偼俵俙倃俈侽侽侽俽僔儕乕僘偺奣梫偱偡丅

乵弌揟乶俙俴俿俤俼俙丂俵俙倃俈侽侽侽丂俢倎倲倎丂俽倛倕倕倲

偙偺俢倎倲倎丂俽倛倕倕倲偱偼俵俙倃俈侽侽侽丄俵俙倃俈侽侽侽俤丄俵俙倃俈侽侽侽俽偲偄偆暋悢偺僔儕乕僘柤偑巊傢傟偰偄傑偡丅

偳偆傗傜嵟弶偵俵俙倃俈侽侽侽偑偮偔傜傟丄偦偺屻偵夵椙宆偲偟偰俵俙倃俈侽侽侽俤偲俵俙倃俈侽侽侽俽偑偮偔傜傟偨傛偆偵悇應偱偒傑偡丅

幚偼偙偺偁偨傝偵偮偄偰傛偔妋偐傔側偄偱偄偄壛尭偵棟夝偟偰偟傑偭偨偨傔偵丄屻偵側偭偰庤捝偄幐攕傪偟偰偟傑偆偙偲偵側傝傑偡丅

偦傟偵偮偄偰偼屻偵側偭偰偐傜偺偍榖偲偄偨偟傑偡丅

俠俹俴俢偺撪晹峔憿偵偮偄偰偐側傝儁乕僕傪偝偄偰愢柧偟偰偁傝傑偡丅

乵弌揟乶俙俴俿俤俼俙丂俵俙倃俈侽侽侽丂俢倎倲倎丂俽倛倕倕倲

杮摉偼偙偺偁偨傝偺偙偲偵偮偄偰傕傛偔棟夝偟偰偍偔偙偲偱丄僾儘僌儔儉偺彂偒曽傗僎乕僩偺妱傝摉偰側偳偺岠棪偑曄傢偭偰偔傞偺偱偟傚偆偗傟偳丄偼偭偒傝偄偭偰丄傛偔傢偐傜傫丅

傑丅

摉柺偺偲偙傠偼偞偭偲栚傪捠偟偰僗儖乕偟偰偟傑偭偰傕傛偄偐側偁丄偲巚偄傑偡丅

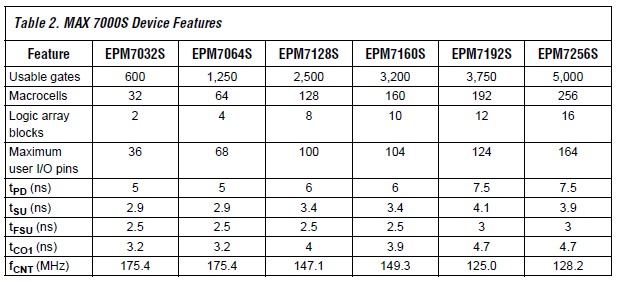

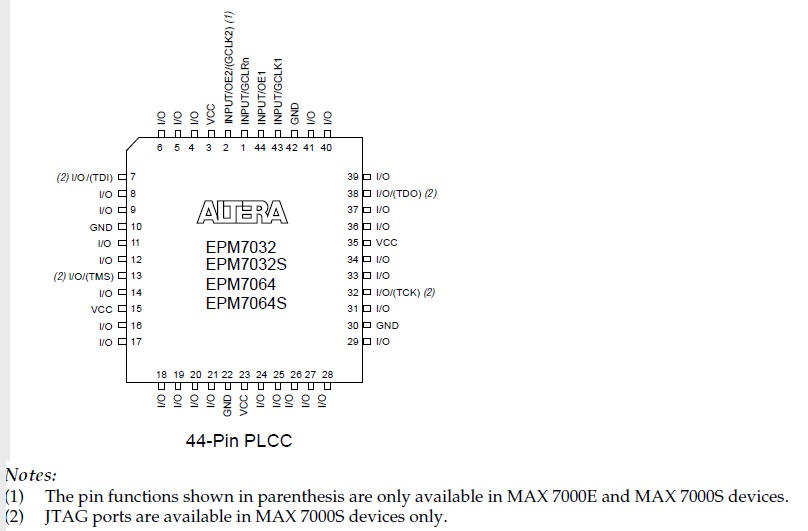

俤俹俵俈侽俁俀俽俴俠係係偺俹倝値攝楍偱偡丅

乵弌揟乶俙俴俿俤俼俙丂俵俙倃俈侽侽侽丂俢倎倲倎丂俽倛倕倕倲

俤俹俵俈侽俁俀俽俴俠係係傪偠偐偵婎斅偵揬傝晅偗偰偟傑偆応崌偵偼偙偺抂巕恾偩偗偱傛偄偺偱偡偑丄俹俴俠俠僜働僢僩傪巊偆応崌偵偼丄僜働僢僩偺俹倝値攝楍偲偁傢偣偰攝抲傪妋擣偡傞昁梫偑偁傝傑偡丅

忋偺攝抲恾偺傛偆偵係係倫倝値俹俴俠俠偺抂巕偼俬俠杮懱偺巐曽偵奺侾侾杮偺抂巕偑侾楍偵暲傫偱偄傑偡丅

偲偙傠偑俹俴俠俠僜働僢僩偼偦偺抂巕傪俀丏俆係倣倣僺僢僠偺抂巕偵曄姺偟偰偄傞偨傔丄婎斅偵幚憰偡傞偨傔偺抂巕偑巐曽偵偦傟偧傟俀楍偵暲傫偱攝抲偝傟偰偄傑偡丅

偦偺偁偨傝偵偮偄偰偼師夞偵愢柧偄偨偟傑偡丅

俠俹俴俢擖栧両乵戞俈夞乶

俀侽侾俋丏俀丏侾俉倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞