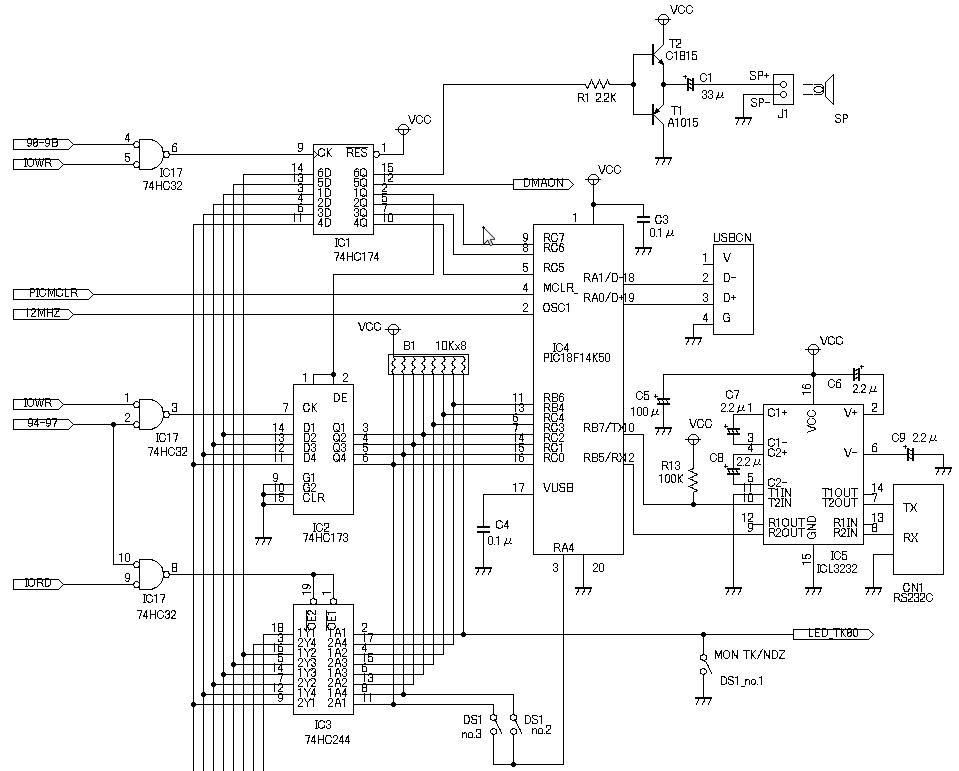

倁俫俢俴傪懍廗両丂倃俠俋俆侾係係倃俴亄侾俇俵俛丒俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖傾僫儔僀僓傪嶌偭偰偟傑偄傑偟偨両

庡栚揑偼嵎偟敆偭偨帠忣偐傜倀俽俛僾儘僩僐儖偺夝愅傪偡傞偙偲偩偭偨偺偱偡偑丄偦偺庤抜偲偟偰慖傫偩偺偑僐儗両

乵戞俇夞乶

仠僇儊儗僆儞倀俽俛亄儘僕傾僫傪夵憿

偙偙悢擔俫俹偺峏怴偑偱偒傑偣傫偱偟偨丅

偊偊丅

椺偵傛偭偰揇徖偵偼傑偭偰傕偑偄偰偍傝傑偟偨丅

杮摉偼慜夞偺懕偒傪彂偐側偗傟偽偄偗側偄偺偱偡偑丄偪傚偭偲梊掕曄峏偱偡丅

俠俹俴俢亄俽俬俵俵偺偍榖偐傜撍慠偵堘偆偲偙傠偵旘傫偱偟傑偄傑偡丅

偁丅

俠俹俴俢偼崱夞傕庡栶傪偮偲傔傑偡丅

偱偡偑俽俬俵俵偱偼偁傝傑偣傫丅

偦偙偺偲偙傠偑僥乕儅偐傜奜傟偰偟傑偄傑偡丅

榖偑旘傫偱偟傑偄傑偡偑丄偟偽偟偍晅偒崌偄傪偍婅偄偄偨偟傑偡丅

摉婰帠偲偟傑偟偰偼傑偩弿偵廇偄偨偽偐傝側偺偱偡偑丄幚嵺偵偼僴乕僪傕僜僼僩傕傎傏幚梡儗儀儖偵傑偱偱偒偰偍傝傑偟偰丄偙偺偲偙傠幚嵺偵倀俽俛摦嶌夝愅偺嶌嬈偵偐偐偭偰偍傝傑偡丅

偦偺惉壥偲偄偄傑偡偐丄愭擔偪傚偭偲婥偵側傞摦嶌偵婥偑晅偒傑偟偰丄偦偙偺偁偨傝傪怺偔孈傝壓偘偰捛媮偟偰傒傛偆偲偄偆偙偲偵側傝傑偟偨丅

尰嵼僥乕儅偲偟偰恑峴拞偺俠俹俴俢亄俽俬俵俵傪巊偭偨夝愅僣乕儖偼丄倀俽俛怣崋傪墶偐傜撉傒庢偭偰丄偦傟傪夝愅偟傛偆偲偄偆傕偺側偺偱偡偑丄偦偺嶌嬈傪偟偰偄傑偟偨傜丄儂僗僩偐傜偺倀俽俛僐儅儞僪偵懳偡傞俹俬俠偺墳摎庤懕偒偵偪傚偭偲婥偵側傞偲偙傠偑傒偮偐傝傑偟偨丅

偦偆偄偆偙偲偵側傝傑偡偲丄奜晹偐傜怣崋傪娤嶡偡傞偺偱偼側偔偰丄俹俬俠撪晹偺摦嶌傪捛愓偡傞偙偲偑昁梫偵側偭偰偒傑偡丅

偟偐偟侾俀俵俫倸偱憲傜傟偰偔傞倀俽俛僐儅儞僪偵墳摎偟側偑傜丄摨帪偵偦偺棳傟傪奜晹偐傜儌僯僞偱偒傞傛偆偵偡傞偺偵偼偪傚偄偲岺晇偑昁梫偱偡丅

壗偐偆傑偄曽朄偼側偄傕偺偐偲俶俢俉侽倅嘨偺夞楬恾傪側偑傔偰偄傑偟偨傜丄側傫偲偐偱偒偦偆側曽朄傪巚偄偮偒傑偟偨丅

俹俬俠侾俉俥侾係俲俆侽偲倅俉侽偑僨乕僞傗僐儅儞僪僷儔儊乕僞傪傗傝偲傝偡傞偨傔偵丄俼俛俇丄俼俛係丄俼俠係乣俼俠侽偺俈價僢僩傪巊偭偰偄傑偡丅

偙傟傪偆傑偔棙梡偟偰丄偙偙偐傜奜偵僨乕僞傪弌椡偡傞傛偆偵偱偒偦偆偱偡丅

倀俽俛働乕僽儖傪愙懕偡傞偲丄偡偖偵俹俬俠侾俉俥侾係俲俆侽偼儂僗僩偲偺娫偱岎怣傪奐巒偟傑偡偑丄倂倝値倓倧倵倱懁偱倅俛俁丏俤倃俤傪幚峴奐巒偡傞傑偱偼丄俹俬俠侾俉俥侾係俲俆侽偲倅俉侽俠俹倀偲偺娫偱偺僨乕僞岎怣偼峴傢傟傑偣傫丅

偱偡偐傜偙偺俈價僢僩偼偦傟傑偱偺娫偼嬻偄偰偄傑偡丅

偟偐偟偳偆偣側傜偽丄側傫偲偐俉價僢僩偵偟偨偄偲偙傠偱偡丅

傛偔傛偔尒偰偄傑偟偨傜俼俛俈傪俀俁俀俠偺憲怣乮俿倃乯偵巊偭偰偄傞偙偲偵婥偑晅偒傑偟偨丅

偙偺俼俛俈傪價僢僩俈偵妱傝摉偰傟偽俉價僢僩偵側傝傑偡丅

偟偐偟偦傟偩偗偱偼傑偩懌傝傑偣傫丅

僷儔儗儖億乕僩偐傜僨乕僞傪弌椡偡傞偲偒偲摨偠傛偆偵俽俿俼俷俛俤僷儖僗偺弌椡傕昁梫偱偡丅

俢俬俹僗僀僢僠偺噦俀丄噦俁傪俷俥俥偵偟偰偍偗偽俼俙係偑巊偊偦偆偱偡丅

偍偍丅

栶幰偑偦傠偄傑偟偨丅

栤戣偼偦傟傪偳偆傗偭偰庴偗庢傞偐偲偄偆偙偲偱偡丅

俹俬俠侾俉俥侾係俲俆侽偵偼侾俀俵俫倸偺僋儘僢僋傪梌偊偰偄傑偡偑丄俹俬俠侾俉俥侾係俲俆侽偼偦傟傪撪晹偱係攞偵偟偰丄係俉俵俫倸偺俠俹倀僋儘僢僋偱摦偄偰偄傑偡丅

偦偺摦嶌傪奜晹偱儌僯僞偡傞偨傔偵丄偙偪傜偑昁梫偲巚偆忣曬傪昁梫側億僀儞僩偱弌椡偟偰傕丄偦傟傪庴偗庢傞偨傔偵偼偦傟憡墳偺夞楬偑昁梫偵側傝傑偡丅

巆擮側偑傜倅俉侽偱偼偲偰傕娫偵崌偄傑偣傫丅

偦偙偱僇儊儗僆儞倀俽俛亄儘僕傾僫傪巊偆偙偲傪峫偊傑偟偨丅

偙傟側傜嵟崅侾侽侽俵俫倸傑偱懳墳偱偒傑偡偐傜廫暘栶偵棫偪傑偡偱偟傚偆丅

偨偩崱夞偼攇宍偺娤應側偳偱偼側偔偰丄俹俬俠侾俉俥侾係俲俆侽偑俽俿俼俷俛俤僷儖僗偲偲傕偵弌椡偡傞俉價僢僩偺僨乕僞傪夝愅偡傞偺偑栚揑偱偡丅

攇宍傪撉傓偙偲偱偦傟傪夝愅偡傞偙偲傕偱偒側偄傢偗偱偼偁傝傑偣傫偑丄偦傟偼側偐側偐偵柺搢側嶌嬈偱偡偟丄壗偲傕傕偳偐偟偄姶偑偁傝傑偡丅

傕偭偲捈愙揑偵僨乕僞偺宍偱庢傞偙偲偑偱偒傟偽傛偄偺偱偡偑乧丅

偍偍丅

偱偒傞偠傖偁傝傑偣傫偐丅

僇儊儗僆儞倀俽俛亄儘僕傾僫偼俠俹俴俢儃乕僪偵僨乕僞儘僈乕偲偟偰儊儌儕儃乕僪傪慻傒崌傢偣偨傕偺偱偡丅

偦傟側傜偦偺慻傒崌傢偣傪偦偺傑傑巊偭偰丄俠俹俴俢傪彂偒姺偊偰丄俹俬俠偐傜偺僨乕僞傪儊儌儕偵拁偊偰偟傑偊偽傛偄偠傖偁傝傑偣傫偐丅

偮傑傝丄俠俹俴俢亄俽俬俵俵偺僶乕僕儑儞堘偄偺傛偆側傕偺偱偡丅

側偤俽俬俵俵傪巊傢側偄偐偲偄偄傑偡偲丄崱夞偺栚揑偲偟偰偼偦傫側偵戝梕検偺儊儌儕偼昁梫側偄偐傜偱偡丅

偦傟偵僇儊儗僆儞倀俽俛亄儘僕傾僫偼偦偺栚揑偱巊偆偨傔偵怣崋擖椡梡偺僾儘乕僽傕戲嶳嶌偭偰丄庢傝晅偗偰偦偺傑傑巊偊傞傛偆偵側偭偰偄傑偡偐傜丄俠俹俴俢偝偊彂偒姺偊傟偽偡偖偵巊偊偦偆偱偡丅

偁偭偲丄傕偲偼僨乕僞傪倀俽俛偱憲傞傛偆偵側偭偰偄傑偡偑丄偦偙偺偲偙傠偼俠俹俴俢亄俽俬俵俵偲摨偠傛偆偵丄僷儔儗儖億乕僩傪巊偆傛偆偵夞楬傪晅偗懌偟傑偡丅

偲偄偆偙偲偱嶌嬈偵偲傝偐偐偭偨偺偱偡偑丄偙傟偑巚偄偺傎偐偰偙偢偭偰偟傑偄丄偍傑偗偵俹俬俠侾俉俥侾係俲俆侽偺偲傫偱傕側偄棊偲偟寠偵偼傑偭偰偟傑偭偨偨傔偵丄傗偭偲僨乕僞偑庢傟傞傛偆偵側傞傑偱丄悢擔偐偐偭偰偟傑偄傑偟偨丅

偲偵偐偔偙偙偺偲偙傠偼娞怱偺倀俽俛偺僾儘僩僐儖夝愅偵擖傞慜偵偦偺僣乕儖嶌傝偵杤摢偟偰偟傑偭偰偍傝傑偟偨丅

偱傕偍偐偘偱側傫偲偐巊偊偦偆側僣乕儖偑偱偒偨傛偆偵巚偄傑偡丅

偊偊丅

倁俫俢俴傕偐側傝巊偊傞傛偆偵側傝傑偟偨偱偡傛丅

偦傟偱偼朻摢偵彂偒傑偟偨傛偆偵丄偟偽傜偔偼梊掕傪曄峏偟傑偟偰丄僇儊儗僆儞倀俽俛亄儘僕傾僫夵憿曇偲偄偆偙偲偱偄偒偨偄偲巚偄傑偡丅

偱偡偑丄杮擔偼偪傚偭偲傕偆帪娫偑側偔側偭偰偟傑偄傑偟偨偺偱丄嬶懱揑側偁傟偙傟偵偮偒傑偟偰偼師夞偐傜偲偄偆偙偲偵偄偨偟傑偡丅

俠俹俴俢亄俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖偺夝愅傪両乵戞俇夞乶

俀侽侾係丏侾丏俀俈倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞