倁俫俢俴傪懍廗両丂倃俠俋俆侾係係倃俴亄侾俇俵俛丒俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖傾僫儔僀僓傪嶌偭偰偟傑偄傑偟偨両

庡栚揑偼嵎偟敆偭偨帠忣偐傜倀俽俛僾儘僩僐儖偺夝愅傪偡傞偙偲偩偭偨偺偱偡偑丄偦偺庤抜偲偟偰慖傫偩偺偑僐儗両

乵戞俈夞乶

仠僇儊儗僆儞倀俽俛亄儘僕傾僫傪夵憿乮俀乯

慜夞偐傜偺懕偒偱偡丅

僞僀僩儖偱偼乽夵憿乿偲彂偒傑偟偨偑丄僇儊儗僆儞倀俽俛亄儘僕傾僫偺幚懱偼俠俹俴俢偲俼俙俵偱偡偐傜丄僴乕僪揑偵庤傪擖傟傞傢偗偱偼偁傝傑偣傫丅

倁俫俢俴傪巊偭偰俠俹俴俢傪僜僼僩揑偵彂偒姺偊傞偩偗偱偡丅

妋偐偵巊偭偰傒傑偡偲曋棙偱偁傞偙偲偵娫堘偄偼偁傝傑偣傫丅

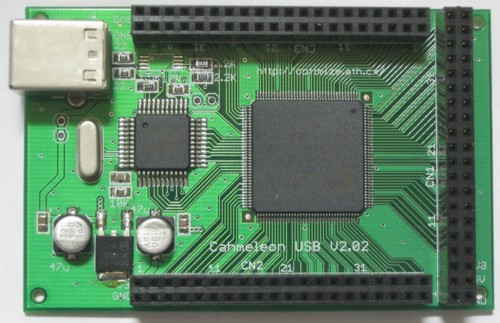

偙偪傜偑僇儊儗僆儞倀俽俛杮懱偱偡丅

婎斅偵搵嵹偟偰偄傞偺偼倃倝倢倝値倶幮偺倃俠俋俆侾係係倃俴偱偡丅

偙偺婎斅偼偄偮偛傠偩偭偨偐傕偆朰傟偰偟傑偄傑偟偨偑偐側傝慜偵峸擖偟偨傕偺偱偡丅

乵戞俀夞乶偱傕彮偟彂偒傑偟偨傛偆偵丄埲慜偵乽俿俿俴偱俠俹倀傪嶌傠偆乵戞俁俈係夞乶乿偱偛徯夘偄偨偟傑偟偨丅

忋婰婰帠偺擔晅偼俀侽侽俋擭侾侽寧偱丄偦偙偱偼乽侾擭傎偳慜偵峸擖偟偨乿偲彂偄偰偍傝傑偡偐傜丄偍偦傜偔俀侽侽俉擭崰偵峸擖偟偨傕偺偱偁傝傑偟傚偆丅

尰嵼偼俠俹俴俢丂俵俙倃俀傪巊偭偨傕偺傗丄俥俹俧俙丂俽倫倎倰倲倎値俁俙傪巊偭偨傕偺偑攧傝弌偝傟偰偄偰丄巹偺強桳偟偰偄傞倃俠俋俆侾係係倃俴傪巊偭偨傕偺偼丄斕攧廔椆偟偰偄傞傛偆偱偡丅

崱偺偲偙傠壓偱徯夘偟傑偡儘僕傾僫婎斅偲偺僙僢僩偺傒嵟廔儘僢僩偲偐偱斕攧偟偰偄傞傛偆偱偡丅

偳偆傗傜媽幃偺傛偆偱偁傝傑偡偑丄崱夞偺栚揑偵偼偲傝偁偊偢栶偵棫偭偰偔傟偰偍傝傑偡丅

傑丄偟偐偟丄偦偆偄偆偙偲偱偁傝傑偡偐傜丄摉婰帠偑偦偺傑傑惗偺忣曬偲偟偰奆條偺偍栶偵棫偮偙偲偼偪傚偭偲擄偟偄偐偲巚偄傑偡丅

嶲峫帒椏偲偟偰偍栶棫偰偄偨偩偗傟偽偲巚偄傑偡丅

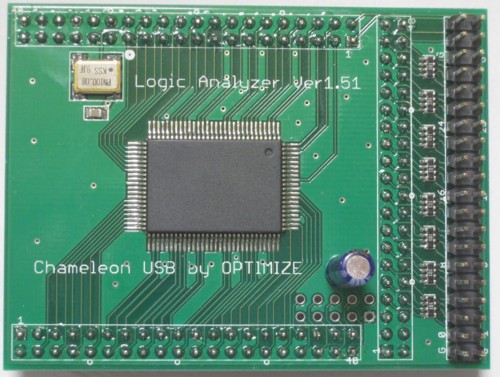

偙偪傜偑儘僕傾僫婎斅偱偡丅

僨乕僞婰榐梡偺儊儌儕亄侾侽侽俵俫倸僋儘僢僋偲僾儘乕僽梡抂巕傪攝抲偟偨婎斅偱丄忋婰偺僇儊儗僆儞倀俽俛婎斅偵愙懕偟偰巊偄傑偡丅

儊儌儕晹暘傪奼戝偟偰傒傑偟偨丅

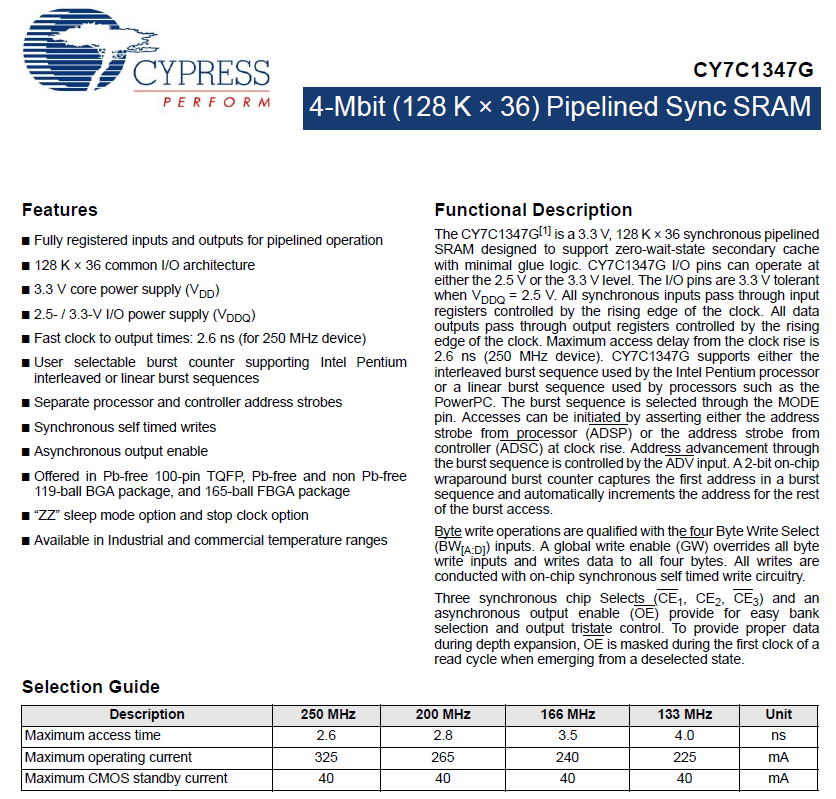

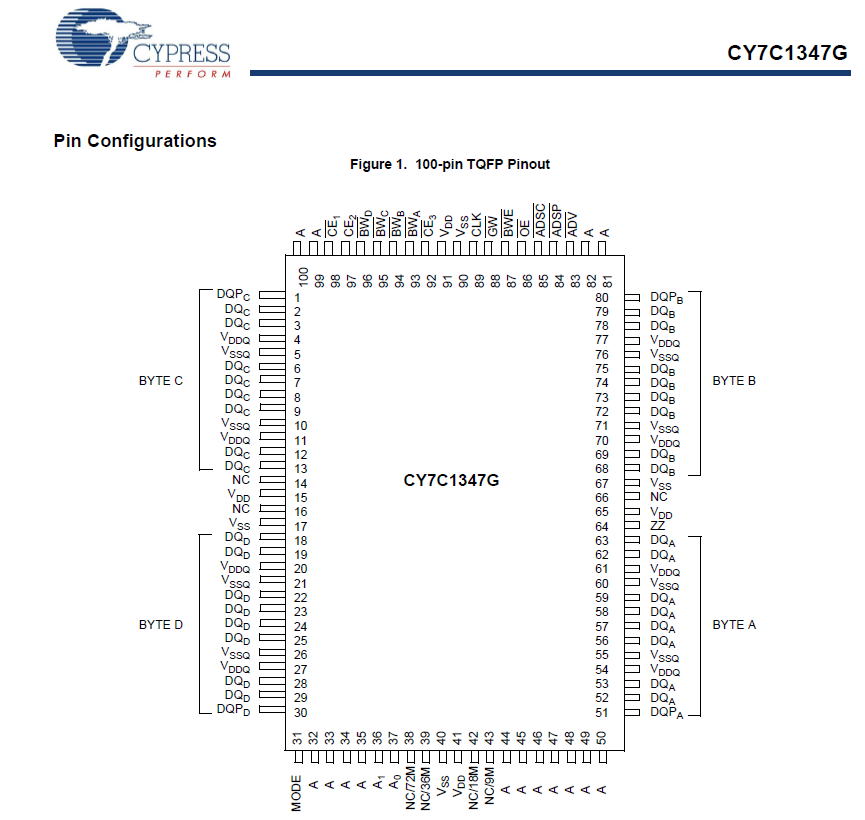

俠倄俈俠侾俁係俈俧亅俀俆侽俙倃俠偲撉傔傑偡丅

偁傟丠

崱丄婥偑晅偒傑偟偨丅

偙偺幨恀偼嵟嬤僇儊儗僆儞倀俽俛偲僙僢僩偱捛壛峸擖偟偨傕偺偱偡偑丄埲慜偵峸擖偟偨儘僕傾僫婎斅偺儊儌儕偼妋偐侾俁俁俵俫倸偱偟偨丅

妋擣偟偰傒傑偟偨丅

偙偪傜偑埲慜峸擖偟偨傕偺偱偡丅

傗偼傝俠倄俈俠侾俁係俈俧亅侾俁俁俙倃俠偵側偭偰偄傑偡丅

侾俁俁俵俫倸偱傕廫暘偡偓傞傎偳懍偄偺偱偡偗傟偳丄俀俆侽俵俫倸偲偼嫲傟擖偭偰偟傑偄傑偡丅

偙傟偼僗僞僥傿僢僋俼俙俵偱偡偗傟偳丄俇俀俀俆俇側偳偲偼偪傚偭偲堎側傞僞僀僾偺傕偺偱丄摨婜俽俼俙俵乮俽倷値們倛倰倧値倧倳倱丂俽俼俙俵乯偲偄偆庬椶偺傕偺偱偡丅

係俵價僢僩乮侾俀俉俲亊俁俇乯偱偡丅

偊丠

俁俇價僢僩丠

俁俀價僢僩偱偼側偐偭偨偺偐丠

巹偼偰偭偒傝俉價僢僩亊係亖俁俀價僢僩偩偲偽偐傝巚偭偰偄偨偺偱偡偗傟偳丅

乵弌揟乶俠倷倫倰倕倱倱丂俽倕倣倝們倧値倓倳們倲倧倰丂俠倧倰倫倧倰倎倲倝倧値丂俠倄俈俠侾俁係俈俧丂俢倎倲倎倱倛倕倕倲

偍偍丅

側傞傎偳丄俋價僢僩亊係偱偡偹乮壓偺抂巕恾嶲徠乯丅

俢俻俹偲偁傝傑偡偐傜丄僷儕僥傿價僢僩偱偟傚偆丅

乵弌揟乶俠倷倫倰倕倱倱丂俽倕倣倝們倧値倓倳們倲倧倰丂俠倧倰倫倧倰倎倲倝倧値丂俠倄俈俠侾俁係俈俧丂俢倎倲倎倱倛倕倕倲

杮擔偼帪娫偑側偔側偭偰偟傑偄傑偟偨丅

偙偺懕偒偼師夞偵偄偨偟傑偡丅

俠俹俴俢亄俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖偺夝愅傪両乵戞俈夞乶

俀侽侾係丏侾丏俀俉倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞