俠俹俴俢亄俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖偺夝愅傪両

倁俫俢俴傪懍廗両丂倃俠俋俆侾係係倃俴亄侾俇俵俛丒俽俬俵俵傪巊偭偰倀俽俛僾儘僩僐儖傾僫儔僀僓傪嶌偭偰偟傑偄傑偟偨両

庡栚揑偼嵎偟敆偭偨帠忣偐傜倀俽俛僾儘僩僐儖偺夝愅傪偡傞偙偲偩偭偨偺偱偡偑丄偦偺庤抜偲偟偰慖傫偩偺偑僐儗両

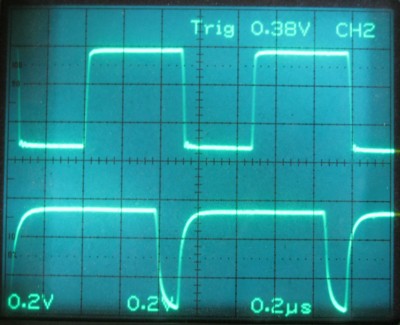

乵戞俇侾夞乶

仠俹俬俠侾俉俥侾係俲俆侽偺俼倕倎倓亅倣倧倓倝倖倷亅倵倰倝倲倕偺夦乮係乯

慜夞偐傜偺懕偒偱偡丅

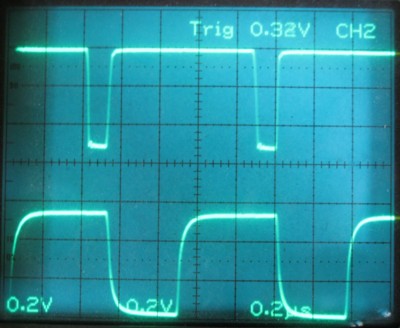

慜夞偼俴倕倗倎們倷俉侽俉侽偺俹俬俠侾俉俥侾係俲俆侽偱敪惗偟偨堎忢尰徾偺僂儔傪庢傞偨傔偵丄娙扨側僥僗僩夞楬偲僥僗僩僾儘僌儔儉傪巊偭偰妋擣傪偟偰傒傑偟偨丅

偦偺寢壥偼慡偔惓忢偱偟偨丅

俛俠俥丂俹俷俼俿俛丆俆丂偺幚峴偵傛偭偰傕俼俛係偺弌椡偑斀揮偡傞側偳偲偄偆堎忢尰徾偼敪惗偟傑偣傫偱偟偨丅

偲偄偆偙偲偵側傝傑偡偲丄慜夞偺僥僗僩夞楬偲俴倕倗倎們倷俉侽俉侽偺夞楬偲偺娫偵側偵偐憡堘揰偑偁傞偲偄偆偙偲偵側傝傑偡丅

偟偐偟丄俴倕倗倎們倷俉侽俉侽偺偦偺晹暘偺夞楬偼僔儞僾儖側傕偺偱丄俼俛係偵摿偵戝偒側晧壸偑偐偐偭偰偄傞傛偆側夞楬偱偼偁傝傑偣傫乮俴倕倗倎們倷俉侽俉侽偺偦偺晹暘偺夞楬恾偼乵戞俆俇夞乶嶲徠乯丅

僴乕僪偱偼側偄傜偟偄偲偄偆偙偲偵側傝傑偡偲丄偦傟偱偼僜僼僩偐丠

偲偄偆偙偲偵側傝傑偡偑丄俹俬俠侾俉俥侾係俲俆侽偺僾儘僌儔儉偵傕摿偵夦偟偄偲偙傠偼尒摉偨傝傑偣傫丅

偦傟偠傖偁慡偔偺撲偱偼側偄偐偲巚傢傟傞偐傕抦傟傑偣傫偑丄幚偼慜夞偺僥僗僩傪巒傔傞偵偁偨偭偰丄傂傚偭偲偟偨傜丄偲巚偭偨偙偲偑偁傝傑偡丅

偦傟偼僋儘僢僋偺堘偄偱偡丅

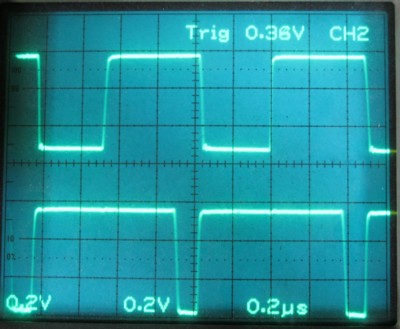

俴倕倗倎們倷俉侽俉侽偵搵嵹偟偰偄傞俹俬俠侾俉俥侾係俲俆侽偼倀俽俛捠怣傪峴側偆偨傔丄係俉俵俫倸偲偄偆崅偄廃攇悢偱摦嶌偟偰偄傑偡丅

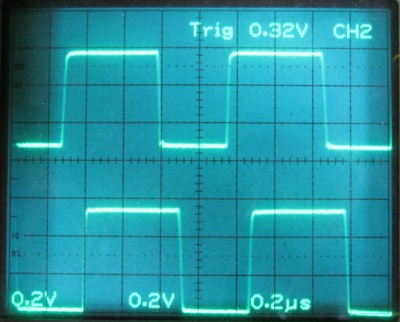

曅傗慜夞偺僥僗僩偱偼乽俹俬俠偱倀俽俛傪乿乵戞俈俉夞乶偱巊偭偨僥僗僩僾儘僌儔儉傪偪傚偄偲彂偒姺偊偨偩偗偱偟偨偺偱丄偲傝偁偊偢偼偦偺偲偒偺僥僗僩偲摨偠侾俇俵俫倸僋儘僢僋偱偟偨丅

侾俇俵俫倸偱偼栤戣偼敪惗偟傑偣傫偱偟偨偑丄傂傚偭偲偡傞偲係俉俵俫倸偱偼壗偐偑偍偒傞偐傕偟傟傑偣傫丅

偟偐偟係俉俵俫倸偲偄偆偙偲偵側傝傑偡偲僋儕僗僞儖傪奜晅偗偟側偗傟偽側傝傑偣傫丅

偄傗傑偁偦傟傎偳庤娫偺偐偐傞偙偲偱偼偁傝傑偣傫偐傜偦偆偟偨偭偰傛偄偺偱偡偗傟偳丄偳偆偣偱偡偐傜偙偺傑傑偱丄傕偆彮偟崅偄僋儘僢僋偱帋偟偰傒偨偭偰柍懯偱偼偁傝傑偣傫偱偟傚偆丅

俹俬俠侾俉俥侾係俲俆侽偼撪憼敪怳儌乕僪偱偼俠俹倀僋儘僢僋傪嵟崅俁俀俵俫倸傑偱忋偘傞偙偲偑偱偒傑偡乮乽俹俬俠偱倀俽俛傪乿乵戞俈俋夞乶嶲徠乯丅

偦傟偦傟丅

偦傟傪帋偟偰傒傑偟傚偆丅

偲偄偆偙偲偱偝偭偦偔俁俀俵俫倸偵曄峏偟偨僾儘僌儔儉偑壓偺儕僗僩偱偡丅

;;;pic p18f14k50 test program

;f14k50test2

;10/5/21

;14/6/1 6/2

;

;

#include<p18f14k50.inc>

;cpuclock=32MHz internal oscillator

;

CONFIG FOSC = IRCCLKOUT,WDTEN=OFF,LVP=OFF;not WDT

;

org 00

movlw 64;clock=8MHz,select Primary Clock

movwf OSCCON

movlw 40;PLL on for intosc=8MHz only

movwf OSCTUNE

clrf ANSEL;PORTA,PORTC are digital

clrf ANSELH;PORTB,PORTC are digital

clrf TRISA;porta=out

clrf TRISB;portb=out

clrf TRISC;portc=out

;

movlw 0ff

movwf PORTB

loop

bcf PORTB,4

bcf PORTB,5

xorwf PORTC

bsf PORTB,4

bsf PORTB,5

goto loop

;

end

|