俠俼俿僀儞僞乕僼僃乕僗儃乕僪偺惢嶌

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

倂倝値倓倧倵倱僷僜僐儞偵倀俽俛愙懕偟偰巊偆尰峴曽幃偼偦傟側傝偵曋棙偱偼偁傝傑偡偑丄偲偒偲偟偰倂倝値倓倧倵倱

偺偟偑傜傒偐傜奐曻偝傟偰丄彫偝偄側偑傜傕撈棫偟偨堦屄偺僷僜僐儞偲偟偰婡擻偟偨偄偲巚偆偙偲傕偁傝傑偡丅

愄偼偦傟偑晛捠偺偙偲偩偭偨偺偱偡偑丄埨壙側俠俼俿僨傿僗僾儗僀偑惗嶻拞巭偲側偭偰媣偟偄崱擔偱偼偦傟

偼姁傢偸偙偲偲掹傔偰偄偨偺偱偡偑乧丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞俀俆夞乶

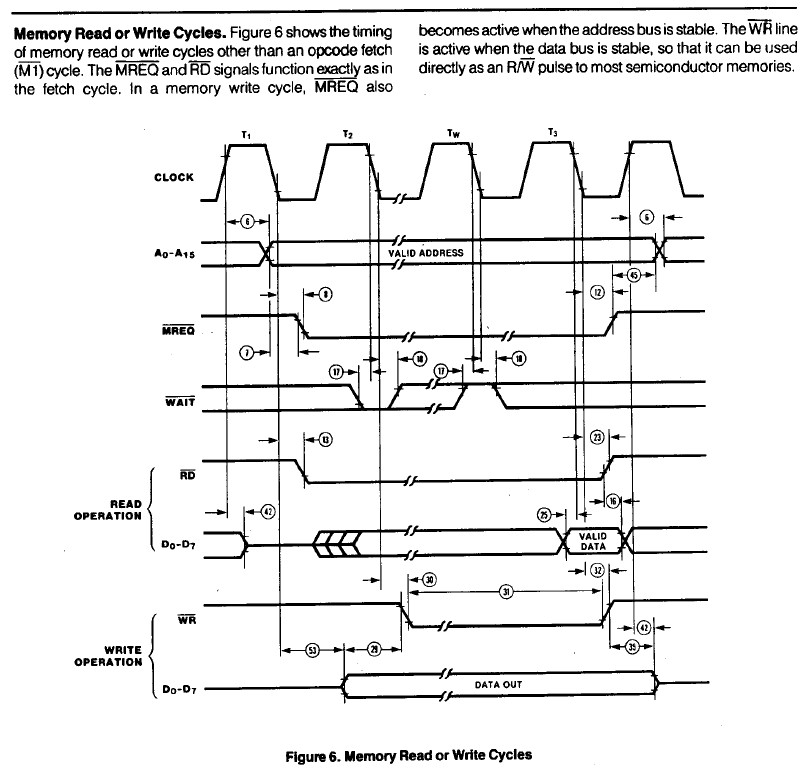

仠俵俼俤俻偲倂俼偺僞僀儈儞僌両

慜夞偼俶俢俉侽俉侽偺偨傔偵俵俤俵倂傪傕偲偵抶墑夞楬傪偮偔偭偰丄偦傟偱俈係俫俠俀係俆偲俈係俫俠侾俆俈傪僗僀僢僠偡傞傛偆偵偟偰丄偦偺攇宍傪僆僔儘偱妋擣偟傑偟偨丅

偦偟偰俶俢俉侽倅俁丏俆偵偮偄偰偼栤戣偁傝傑偣傫丄偲彂偒傑偟偨丅

偱傕傗偭傁傝擮偺偨傔偵俶俢俉侽倅俁丏俆偵偮偄偰傕僆僔儘偱妋擣偟偰傒傑偟偨傜丅

傑偝偐偺攇宍偱偁傝傑偟偨丅

俶俢俉侽倅俁丏俆傕婋側偄偠傖偁傝傑偣傫偐丅

應掕億僀儞僩偼慜夞偲摨偠丄忋懁乮俠俫侾乯偑價僨僆俼俙俵乮俇俀俠俀俆俇乯偺倫倝値俀俈乮倂俼乯偱壓懁乮俠俫俀乯偑俈係俫俠俀係俆偺倫倝値侾俋偱偡丅

崱夞偼俶俢俉侽倅俁丏俆偲愙懕偟偰偄傑偡偐傜壓懁乮俠俫俀乯偼俵俼俤俻偑傕偲偵側偭偰偄傑偡丅

俵俼俤俻偺棫偪忋偑傝偲倂俼偺棫偪忋偑傝偑傎偲傫偳摨偠偱偡丅

偙偙偱傗偭偲巚偄弌偟傑偟偨丅

倅俉侽偺俵俼俤俻偲倂俼偺娭學偵偮偄偰偱偡丅

妋偐俵俼俤俻偺棫偪忋偑傝偲倂俼偺棫偪忋偑傝偺僞僀儈儞僌偵偮偄偰偼偼偭偒傝偟偨悢抣偑帵偝傟偰偄側偐偭偨傛偆側乧丅

偆乕傫丅

傗偭傁傝偄偄壛尭側偙偲傪偟側偄偱丄壗偱傕僨乕僞僔乕僩偱偟偭偐傝妋擣偡傋偒偱偁傝傑偟偨丅

僀儞僞乕僱僢僩偐傜僟僂儞儘乕僪偟偨偐側傝愄偺僨乕僞僔乕僩偱偡丅

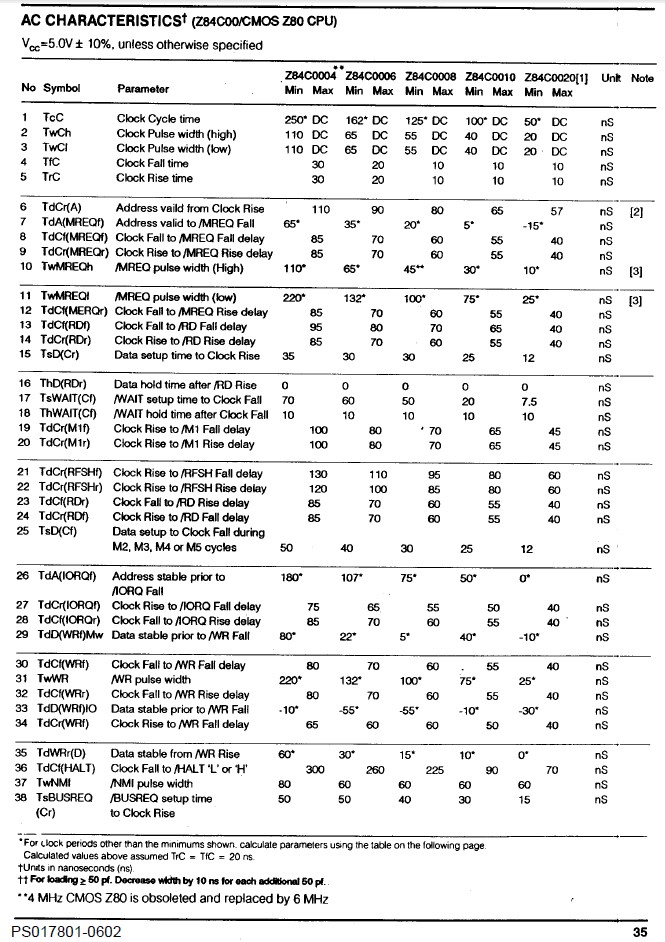

倅俉侽偺僞僀儈儞僌僨乕僞偱偡丅

乵弌揟乶倅倝倢倧倗丆俬値們丏丂倅俉係侽侽乛倅俉係俠侽侽丂俹倰倧倓倳們倲丂俽倫倕們倝倖倝們倎倲倝倧値

栤戣偼俵俼俤俻偺乮侾俀乯偲倂俼偺乮俁俀乯偱偡丅

偙偺俀偮傪壓偺昞偱妋擣偡傞偲丅

乵弌揟乶倅倝倢倧倗丆俬値們丏丂倅俉係侽侽乛倅俉係俠侽侽丂俹倰倧倓倳們倲丂俽倫倕們倝倖倝們倎倲倝倧値

偨偲偊偽倅俉係俠侽侽侽俇偺応崌丄侾俀丂俠倢倧們倠丂俥倎倢倢丂倲倧丂乛俵俼俤俻丂俼倝倱倕丂倓倕倢倎倷偑俵倎倶丂俈侽値倱偱丄俁俀丂俠倢倧們倠丂俥倎倢倢丂倲倧丂乛倂俼丂俼倝倱倕丂倓倕倢倎倷傕俵倎倶丂俈侽値倱偱丄僋儘僢僋偐傜偺抶墑偺嵟戝抣偼偳偪傜傕俈侽値倱側偺偱偡偑丄偦傟偠傖偁乛俵俼俤俻偲乛倂俼偺棫偪忋偑傝偺娭學偼丠偲偄偄傑偡偲丄偙偺悢抣偐傜偼壗傕傢偐傝傑偣傫丅

幚偵崲偭偨偙偲側偺偱偡偑丅

崱夞偺俠俼俿僀儞僞乕僼僃乕僗偺応崌丄倂俼偑俵俼俤俻傛傝傕憗偔棫偪忋偑偭偰偔傟傞偙偲偑朷傑偟偄偺偱偡偑丄忋偺僨乕僞偐傜偼媡傕桳傝偆傞偲傕峫偊傜傟傑偡丅

倂俼偺棫偪忋偑傝偑俵俼俤俻偺棫偪忋偑傝傛傝傕抶偄応崌偵偼丄崱夞偺夞楬偱偼乮俵俼俤俻偑愗姺偊怣崋偵側傞偨傔乯僨乕僞丄傾僪儗僗偑俷俥俥偵側傞偺偲丄倂俼偺棫偪忋偑傝偲偑摨帪偲偄偆偙偲偵側傝傑偡丅

偝偒傎偳偺幨恀偐傜尒傞偲丄傎偲傫偳摨帪偺傛偆偵尒偊傑偡丅

偦傟偭偰丄杮摉偵戝忎晇側偺丠

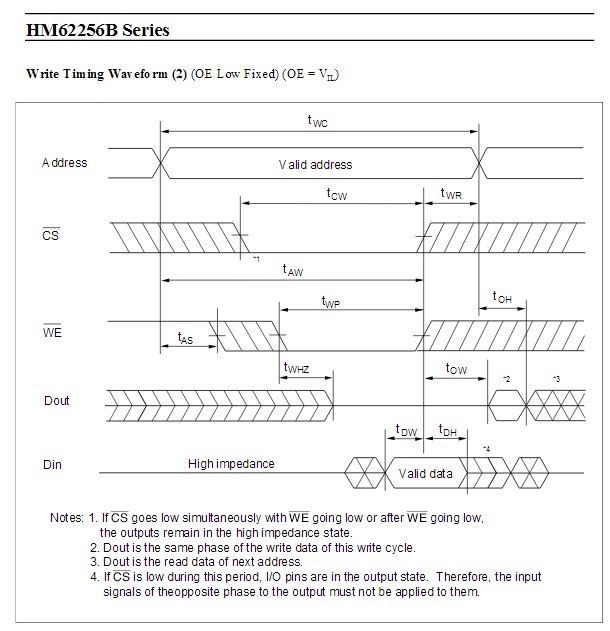

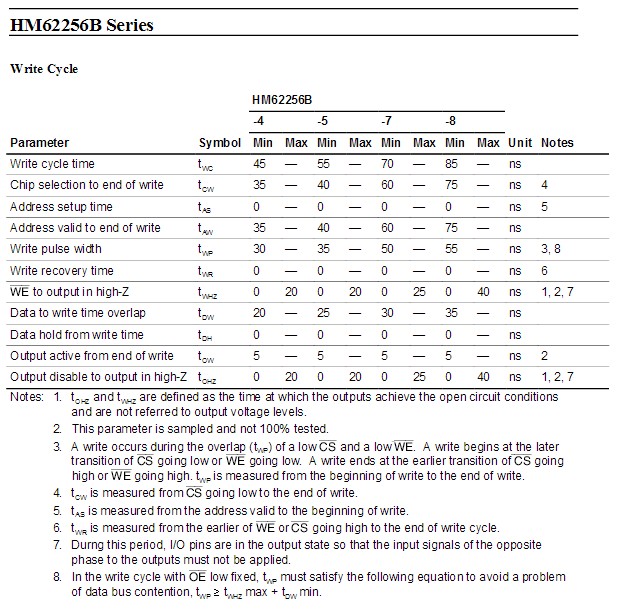

偲偄偆偙偲偱丄偙偙偱傗偭偲俇俀俀俆俇偺僨乕僞傪妋擣偟偰傒傞偙偲偵偄偨偟傑偟偨乮幚偵抶偄両乯丅

杮摉偵丄崱崰偵側偭偰丄偱偡丅

偙偪傜傕悘暘屆偄擭戙暔偺僨乕僞僔乕僩偱偡丅

乵弌揟乶俫俬俿俙俠俫俬丂俇俀俀俆俇俛丂俢倎倲倎丂俽倛倕倕倲

忋偺僠儍乕僩偺倲倂俼偲倲俢俫偺抣傪妋擣偟傑偡丅

乵弌揟乶俫俬俿俙俠俫俬丂俇俀俀俆俇俛丂俢倎倲倎丂俽倛倕倕倲

倲倂俼偲倲俢俫偺抣偼偳偪傜傕嵟彫抣偼侽値倱偱偟偨丅

偲偄偆偙偲偼丄傾僪儗僗丄僨乕僞偺俷俥俥偲倂俼偺棫偪忋偑傝偑摨帪偱傕傛偄偲偄偆偙偲偵側傝傑偡丅

偆乕傫丅

傗偭傁傝妋擣偟偰傒傞傋偒偱偁傝傑偟偨丅

偲偄偆偙偲偼丅

慜夞偑傫偽偭偰偮偔偭偨抶墑夞楬偼柍懯偲偄偆偙偲偵側傝傑偡丅

傗傟傗傟丅

寢嬊壓偺傛偆偵俵俼俤俻偲俵俤俵倂偺偳偪傜偐傪僗僀僢僠偱慖傇偲偄偆僔儞僾儖側夞楬偵棊偪拝偒傑偟偨丅

俠俼俿僀儞僞乕僼僃乕僗儃乕僪偺惢嶌乵戞俀俆夞乶

俀侽侾俇丏俋丏俁侽倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞