(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞俀侽俆夞乶

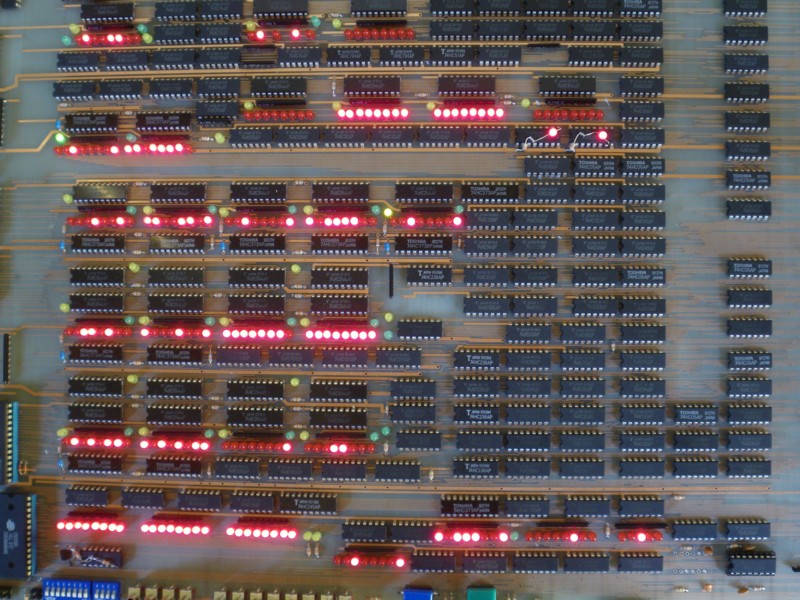

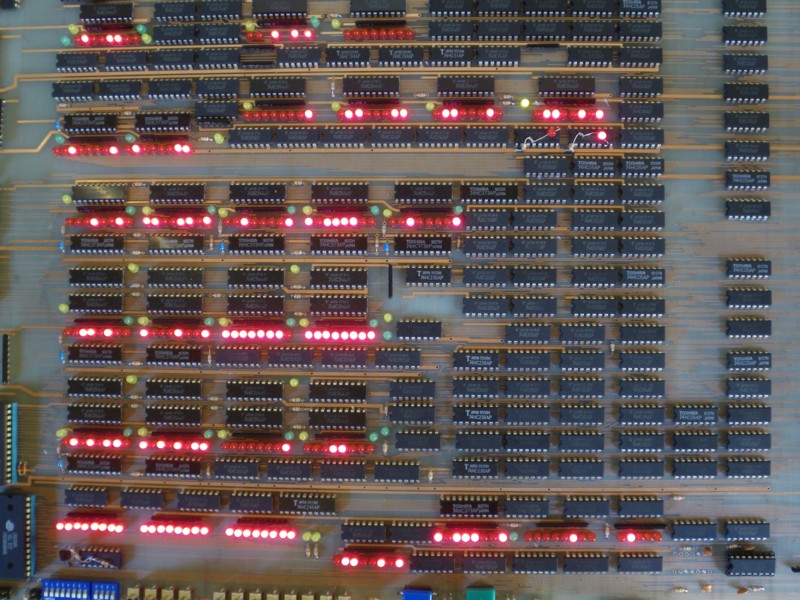

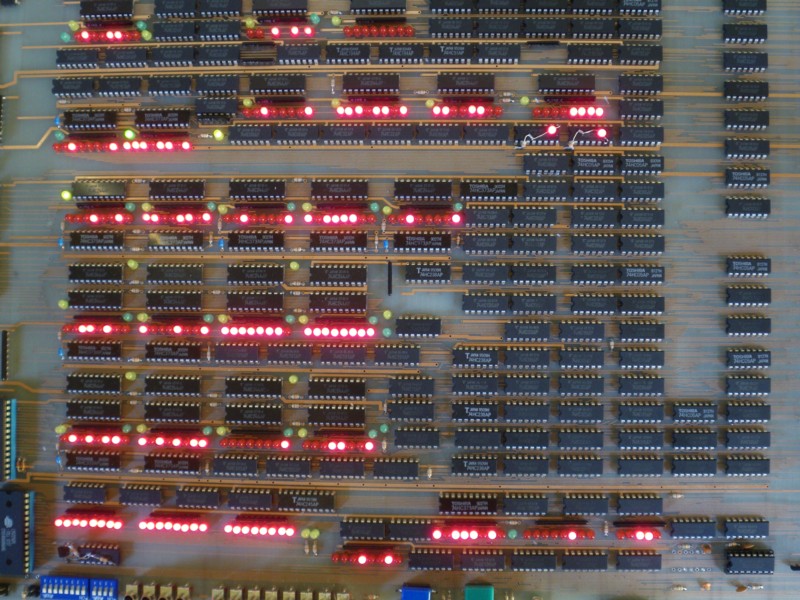

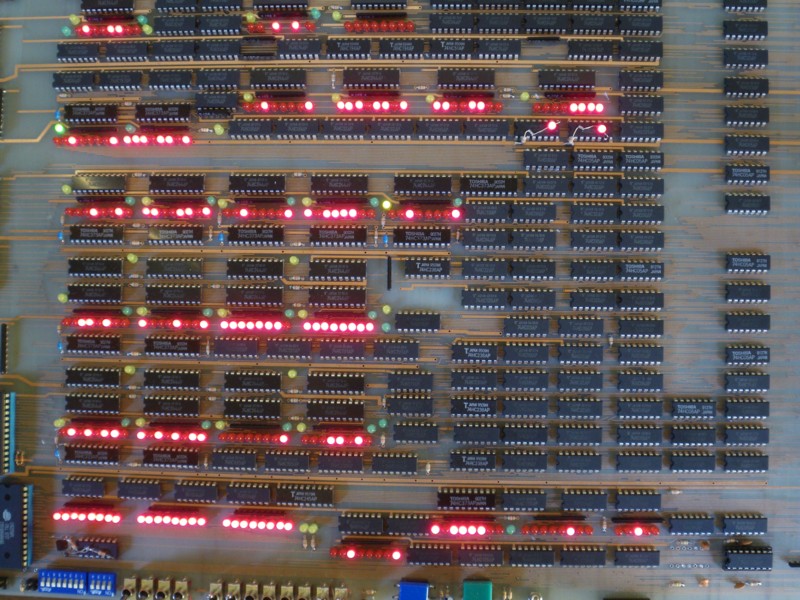

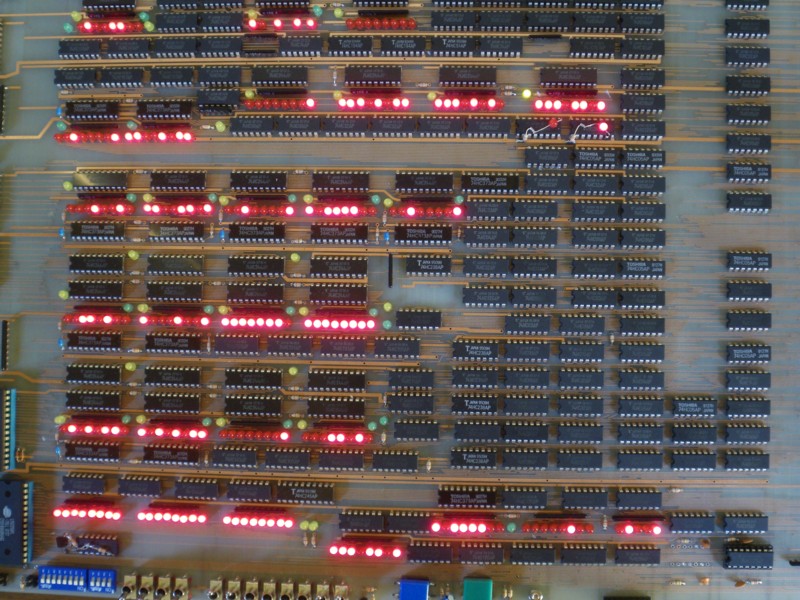

仠俠俵俹柦椷偺僋儘僢僋枅偺摦嶌偺幨恀偱偡乮慜夞偺懕偒偱偡乯

慜夞偺偍偝傜偄偱偡丅

儗僕僗僞偵偼師偺抣偑擖偭偰偄傑偡丅

俫儗僕僗僞丂俁係

俴儗僕僗僞丂俉俋

俢儗僕僗僞丂侾俀

俤儗僕僗僞丂俠俢

俛儗僕僗僞丂俀侾

俠儗僕僗僞丂俛俠

俙儗僕僗僞丂俀侾

僥僗僩僾儘僌儔儉偺俠俵俹柦椷偺晹暘偱偡丅

侾侾俇丂俛俉丂丂丂丂俠俵俹丂俛

侾侾俈丂俛俋丂丂丂丂俠俵俹丂俠

侾侾俉丂俛俙丂丂丂丂俠俵俹丂俢

侾侾俋丂俛俠丂丂丂丂俠俵俹丂俫

侾侾俙丂俈俇丂丂丂丂俫俴俿

慜夞偼嵟弶偺俠俵俹丂俛柦椷偺幨恀傪偍尒偣偟傑偟偨丅

崱夞偼偦偺師偺俠俵俹丂俠柦椷偐傜偱偡丅

仠俠俵俹丂俠柦椷偺摦嶌偺幨恀偱偡

俙儗僕僗僞偵偼俀侾偑擖偭偨傑傑偱偡丅

俠儗僕僗僞偵偼俛俠偑擖偭偰偄傑偡丅

俀侾偲俛俠偲偺斾妑偱偡丅晞崋柍偟悢偲偟偰峫偊傞偲丄摉慠俀侾傛傝傕俛俠偺曽偑戝偒偄偱偡偐傜丄俠乮僉儍儕乕乯僼儔僌偑僙僢僩偝傟傑偡丅

偦偺堦曽偱丄晞崋晅偺悢偲偟偰峫偊傟偽丄俛俠偼晧偺悢偱偡偐傜丄俛俠偺曽偑彫偝偄偙偲偵側傝傑偡丅

晞崋晅悢偺斾妑偺応崌偵偼丄俠乮僉儍儕乕乯僼儔僌偱偼側偔偰丄俽乮僒僀儞乯僼儔僌傪尒傑偡丅

晞崋晅悢偲偟偰偺丄俀侾亅俛俠偺寢壥偼惓偺抣偵側傝傑偡偐傜丄俽乮僒僀儞乯僼儔僌偑僋儕傾偝傟傑偡丅

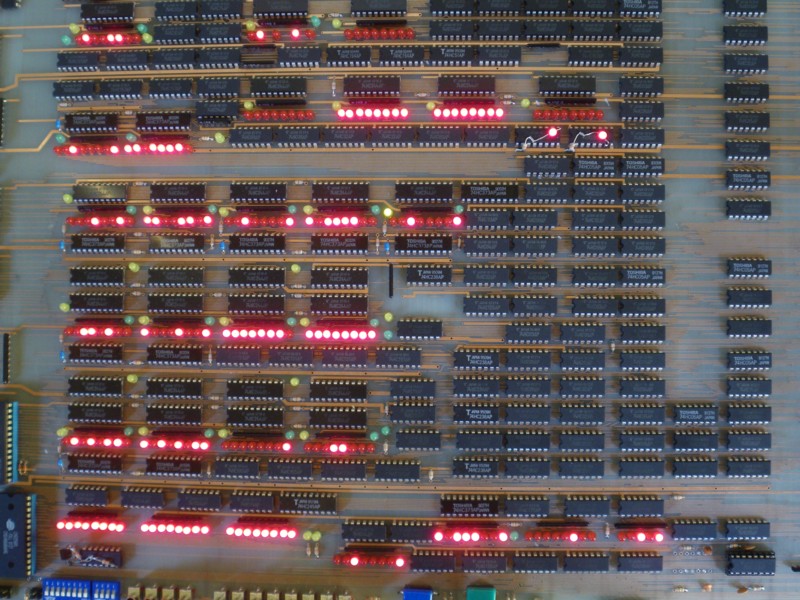

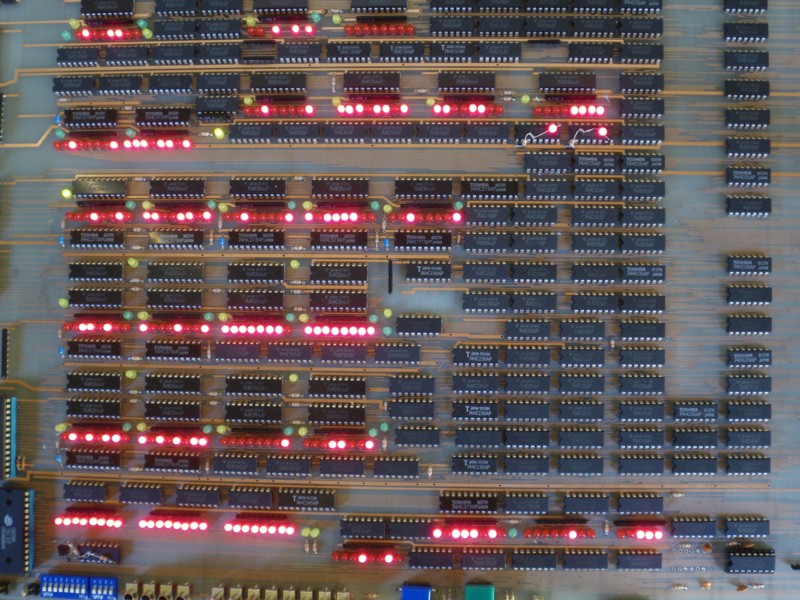

俠俵俹丂俠柦椷偺俿係偺幨恀偱偡丅

俙儗僕僗僞偺抣乮俀侾乯偑撪晹僨乕僞僶僗偵撉傒弌偝傟丄俙俴倀偺儗僕僗僞乭俙乭偵彂偒崬傑傟偰偄傑偡丅

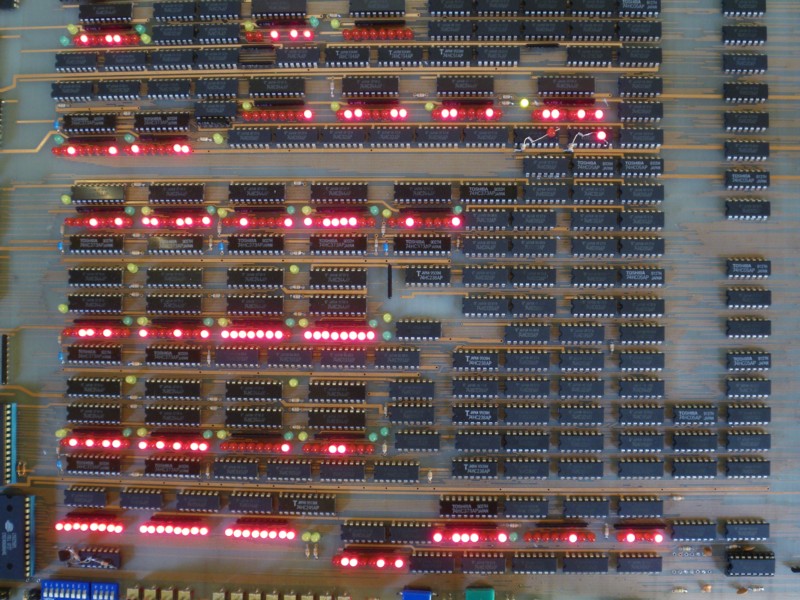

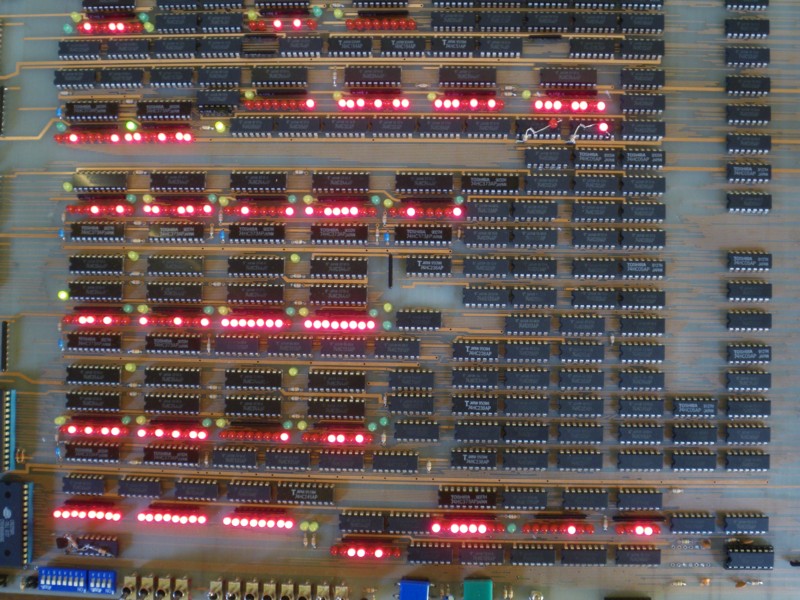

俠俵俹丂俠柦椷偺俿俆偺幨恀偱偡丅

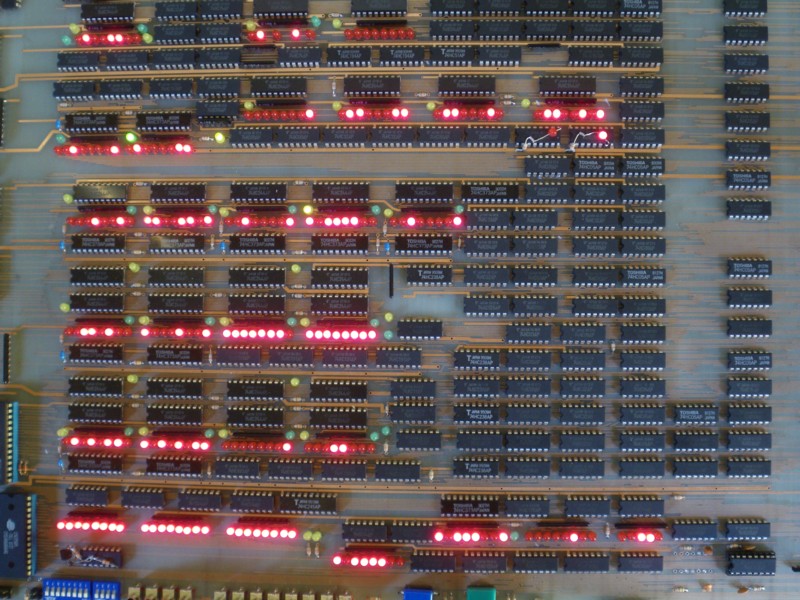

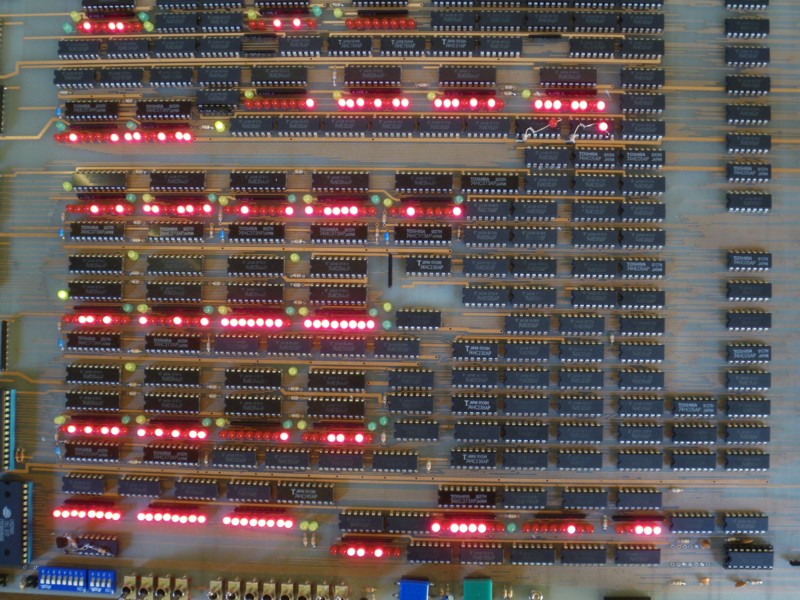

俠俵俹丂俠柦椷偺俿俇偺幨恀偱偡丅

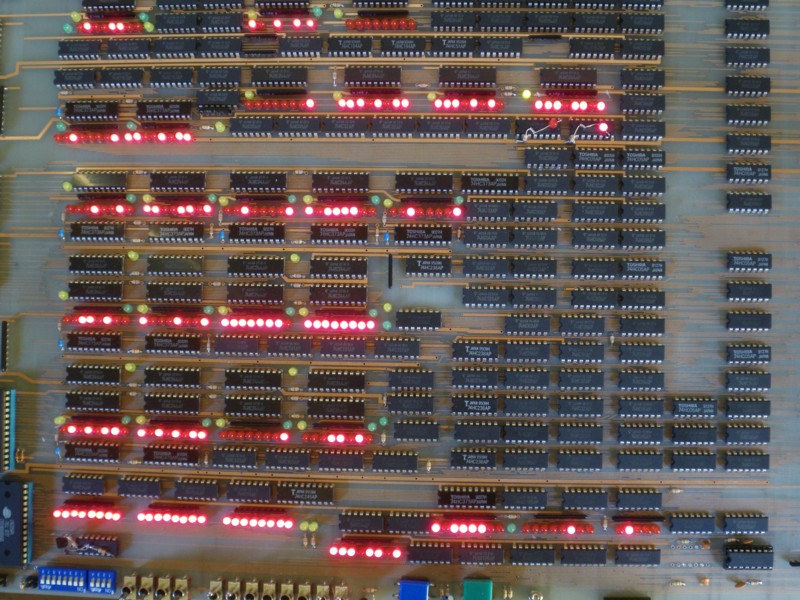

俠儗僕僗僞偺抣丄俛俠偑撪晹僨乕僞僶僗偵撉傒弌偝傟傑偟偨丅

俠儗僕僗僞偺嵍偵偁傞丄俠倰倕倗俼俢乮墿俴俤俢乯偑揰摂偟偰偄傑偡丅

撪晹僨乕僞僶僗傕俛俠偵側偭偰偄傑偡丅

俙俴倀偺儗僕僗僞乭俛乭偵偼丄撪晹僨乕僞僶僗偺俛俠偱偼側偔偰丄係俁偲偄偆抣偑彂偒崬傑傟偰偄傑偡丅

係俁偼俛俠傪斀揮偝偣偨抣偱偡丅

俙俴倀儗僕僗僞乭俙乭偲俙俴倀儗僕僗僞乭俛乭偺抣偼懄嵗偵壛嶼偝傟偰丄俙俢俢儗僕僗僞偵昞帵偝傟傑偡丅

俀侾亄係俁亄侾亖俇俆偺寁嶼偑峴傢傟偰丄俙俢俢儗僕僗僞偺昞帵偑俇俆偵側傝傑偟偨乮尭嶼偱偼昁偢亄侾偑壛嶼偝傟傑偡乯丅

壛嶼偺寢壥丄忋埵寘傊偺寘忋偘偼敪惗偟傑偣傫偐傜丄忋埵寘傊偺寘忋偘傪帵偡嵍懁偺俴俤俢偼徚摂偟偰偄傑偡丅

尭嶼偺偲偒偼丄偙偺寘忋偘偺桳柍傪媡揮偝偣偨抣偑丄忋埵寘傊偺僉儍儕乕乮儃儘乕乯偵側傝傑偡丅

偱偡偐傜丄崱夞偺寁嶼偺寢壥丄僉儍儕乕僼儔僌偼僙僢僩偝傟傞偙偲偵側傝傑偡偑丄傑偩偙偺抜奒偱偼丄僉儍儕乕僼儔僌傊偺斀塮偼峴傢傟傑偣傫丅

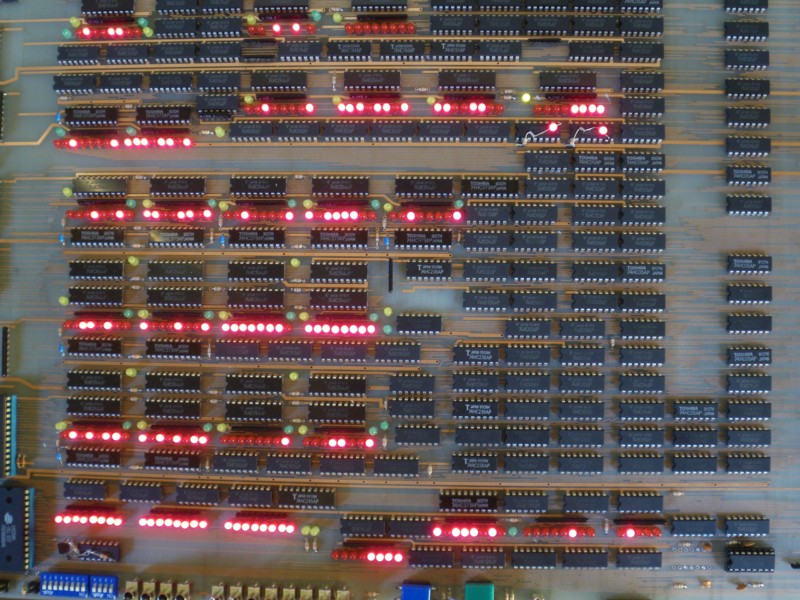

俠俵俹丂俠柦椷偺俿俈偺幨恀偱偡丅

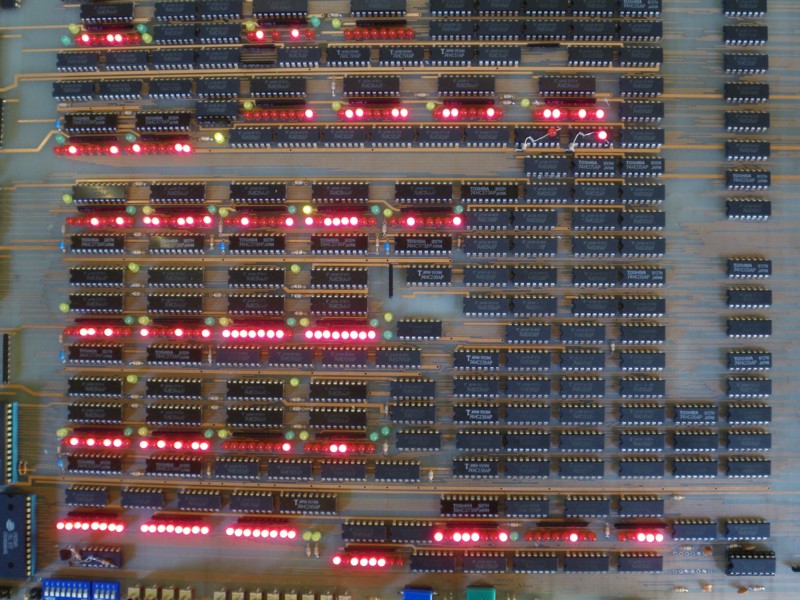

俠俵俹丂俠柦椷偺俿俉偺幨恀偱偡丅

俙俢俢儗僕僗僞偺俴俤俢昞帵偺嵍懁偵偁傞丄俙倓倓俼俢乮墿俴俤俢乯偑揰摂偟偰丄壛嶼偺寢壥乮俇俆乯偑撪晹僨乕僞僶僗偵弌偝傟偰偄傑偡丅

偟偐偟丄俙儗僕僗僞偵偼彂偒崬傒偼峴傢傟偢丄俙儗僕僗僞偼傕偲偺抣傪曐帩偟偰偄傑偡丅

僼儔僌儗僕僗僞偼丄嵍抂偺俽乮僒僀儞乯僼儔僌偲丄偦偺塃偺倅乮僛儘乯僼儔僌偑徚摂丄偦偺塃偺俫乮僴乕僼僉儍儕乕乯僼儔僌偲丄塃抂偺俠乮僉儍儕乕乯僼儔僌偑揰摂偟傑偟偨丅

俠俵俹丂俠柦椷偺俿俋偺幨恀偱偡丅

俠俵俹丂俠柦椷偑廔傢傝傑偟偨丅

師偼俠俵俹丂俢柦椷偱偡丅

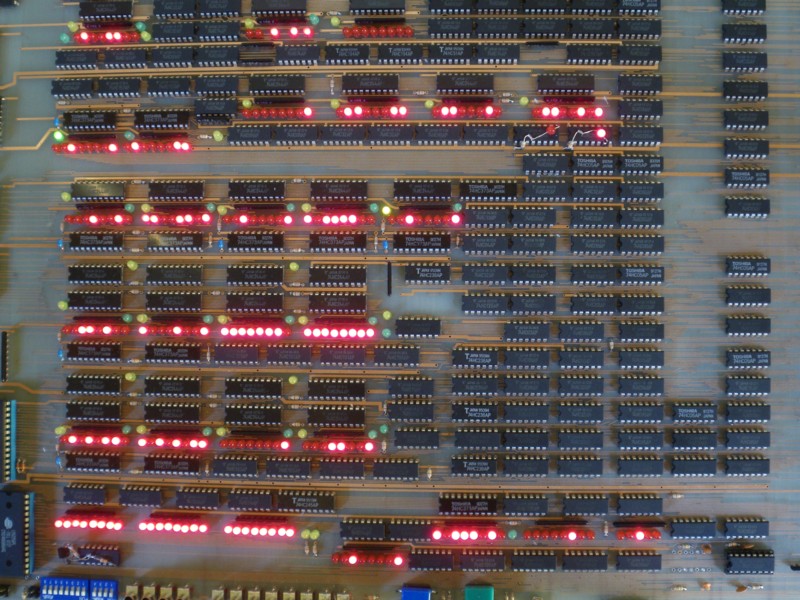

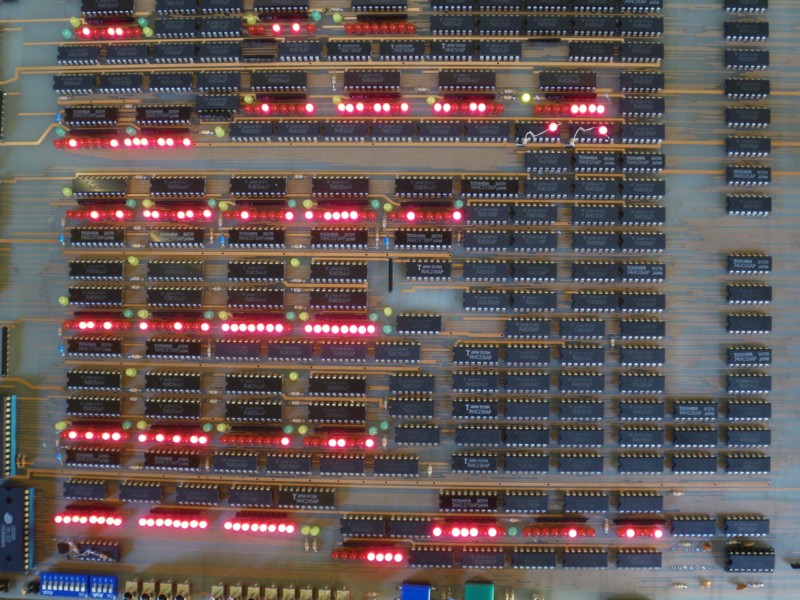

仠俠俵俹丂俢柦椷偺摦嶌偺幨恀偱偡

俙儗僕僗僞偵偼俀侾偑擖偭偨傑傑偱偡丅

俢儗僕僗僞偵偼侾俀偑擖偭偰偄傑偡丅

俀侾偲侾俀偲偺斾妑偱偡丅崱夞偼晞崋柍偟悢偲偟偰峫偊偰傕丄晞崋晅悢偲偟偰峫偊偰傕丄摉慠俀侾傛傝傕侾俀偺曽偑彫偝偄偱偡偐傜丄俠乮僉儍儕乕乯僼儔僌傕俽乮僒僀儞乯僼儔僌傕僋儕傾偝傟傑偡丅

俠俵俹丂俢柦椷偺俿係偺幨恀偱偡丅

俙儗僕僗僞偺抣乮俀侾乯偑撪晹僨乕僞僶僗偵撉傒弌偝傟丄俙俴倀偺儗僕僗僞乭俙乭偵彂偒崬傑傟偰偄傑偡丅

俠俵俹丂俢柦椷偺俿俆偺幨恀偱偡丅

俠俵俹丂俢柦椷偺俿俇偺幨恀偱偡丅

俢儗僕僗僞偺抣丄侾俀偑撪晹僨乕僞僶僗偵撉傒弌偝傟傑偟偨丅

俢儗僕僗僞偺嵍偵偁傞丄俢倰倕倗俼俢乮墿俴俤俢乯偑揰摂偟偰偄傑偡丅

撪晹僨乕僞僶僗傕侾俀偵側偭偰偄傑偡丅

俙俴倀偺儗僕僗僞乭俛乭偵偼丄撪晹僨乕僞僶僗偺侾俀偱偼側偔偰丄俤俢偲偄偆抣偑彂偒崬傑傟偰偄傑偡丅

俤俢偼侾俀傪斀揮偝偣偨抣偱偡丅

俙俴倀儗僕僗僞乭俙乭偲俙俴倀儗僕僗僞乭俛乭偺抣偼懄嵗偵壛嶼偝傟偰丄俙俢俢儗僕僗僞偵昞帵偝傟傑偡丅

俀侾亄俤俢亄侾亖侾侽俥偺寁嶼偑峴傢傟偰丄俙俢俢儗僕僗僞偺昞帵偑侽俥偵側傝傑偟偨乮尭嶼偱偼昁偢亄侾偑壛嶼偝傟傑偡乯丅

壛嶼偺寢壥丄忋埵寘傊偺寘忋偘偑敪惗偟傑偡偐傜丄忋埵寘傊偺寘忋偘傪帵偡嵍懁偺俴俤俢偑揰摂偟偰偄傑偡丅

尭嶼偺偲偒偼丄偙偺寘忋偘偺桳柍傪媡揮偝偣偨抣偑丄忋埵寘傊偺僉儍儕乕乮儃儘乕乯偵側傝傑偡丅

偱偡偐傜丄崱夞偺寁嶼偺寢壥丄僉儍儕乕僼儔僌偼僋儕傾偝傟傞偙偲偵側傝傑偡偑丄傑偩偙偺抜奒偱偼丄僉儍儕乕僼儔僌傊偺斀塮偼峴傢傟傑偣傫丅

俠俵俹丂俢柦椷偺俿俈偺幨恀偱偡丅

俠俵俹丂俢柦椷偺俿俉偺幨恀偱偡丅

俙俢俢儗僕僗僞偺俴俤俢昞帵偺嵍懁偵偁傞丄俙倓倓俼俢乮墿俴俤俢乯偑揰摂偟偰丄壛嶼偺寢壥乮侽俥乯偑撪晹僨乕僞僶僗偵弌偝傟偰偄傑偡丅

偟偐偟丄俙儗僕僗僞偵偼彂偒崬傒偼峴傢傟偢丄俙儗僕僗僞偼傕偲偺抣傪曐帩偟偰偄傑偡丅

僼儔僌儗僕僗僞偼丄嵍抂偺俽乮僒僀儞乯僼儔僌偲丄偦偺塃偺倅乮僛儘乯僼儔僌偑徚摂丄偦偺塃偺俫乮僴乕僼僉儍儕乕乯僼儔僌偼揰摂偟傑偟偨偑丄塃抂偺俠乮僉儍儕乕乯僼儔僌偼徚摂偟傑偟偨丅

俀侾亅侾俀偺尭嶼偱偼丄壓埵係價僢僩偺尭嶼乮侾亅俀乯偱丄忋埵係價僢僩傊偺儃儘乕偑敪惗偡傞偨傔丄俫乮僴乕僼僉儍儕乕乯僼儔僌偑僙僢僩偝傟傑偡丅

俠俵俹丂俢柦椷偺俿俋偺幨恀偱偡丅

俠俵俹丂俢柦椷偑廔傢傝傑偟偨丅

師偼俠俵俹丂俫柦椷偱偡丅

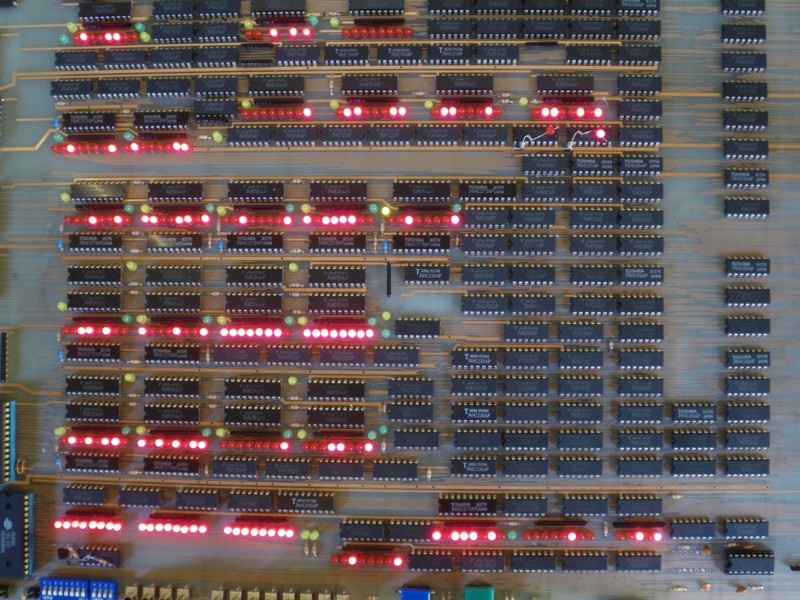

仠俠俵俹丂俫柦椷偺摦嶌偺幨恀偱偡

俙儗僕僗僞偵偼俀侾偑擖偭偨傑傑偱偡丅

俫儗僕僗僞偵偼俁係偑擖偭偰偄傑偡丅

俀侾偲俁係偲偺斾妑偱偡丅晞崋柍偟悢偲偟偰峫偊傞偲丄摉慠俀侾傛傝傕俁係偺曽偑戝偒偄偱偡偐傜丄俠乮僉儍儕乕乯僼儔僌偑僙僢僩偝傟傑偡丅

晞崋晅偺悢偲偟偰峫偊偰傕丄俀侾亅俁係偺寢壥偼晧偺悢偵側傝傑偡偐傜偱偡偐傜丄俽乮僒僀儞乯僼儔僌傕僙僢僩偝傟傑偡丅

俠俵俹丂俫柦椷偺俿係偺幨恀偱偡丅

俙儗僕僗僞偺抣乮俀侾乯偑撪晹僨乕僞僶僗偵撉傒弌偝傟丄俙俴倀偺儗僕僗僞乭俙乭偵彂偒崬傑傟偰偄傑偡丅

俠俵俹丂俫柦椷偺俿俆偺幨恀偱偡丅

俠俵俹丂俫柦椷偺俿俇偺幨恀偱偡丅

俫儗僕僗僞偺抣丄俁係偑撪晹僨乕僞僶僗偵撉傒弌偝傟傑偟偨丅

俫儗僕僗僞偺嵍偵偁傞丄俫倰倕倗俼俢乮墿俴俤俢乯偑揰摂偟偰偄傑偡丅

撪晹僨乕僞僶僗傕俁係偵側偭偰偄傑偡丅

俙俴倀偺儗僕僗僞乭俛乭偵偼丄撪晹僨乕僞僶僗偺俁係偱偼側偔偰丄俠俛偲偄偆抣偑彂偒崬傑傟偰偄傑偡丅

俠俛偼俁係傪斀揮偝偣偨抣偱偡丅

俙俴倀儗僕僗僞乭俙乭偲俙俴倀儗僕僗僞乭俛乭偺抣偼懄嵗偵壛嶼偝傟偰丄俙俢俢儗僕僗僞偵昞帵偝傟傑偡丅

俀侾亄俠俛亄侾亖俤俢偺寁嶼偑峴傢傟偰丄俙俢俢儗僕僗僞偺昞帵偑俤俢偵側傝傑偟偨乮尭嶼偱偼昁偢亄侾偑壛嶼偝傟傑偡乯丅

壛嶼偺寢壥丄忋埵寘傊偺寘忋偘偼敪惗偟傑偣傫偐傜丄忋埵寘傊偺寘忋偘傪帵偡嵍懁偺俴俤俢偼徚摂偟偰偄傑偡丅

尭嶼偺偲偒偼丄偙偺寘忋偘偺桳柍傪媡揮偝偣偨抣偑丄忋埵寘傊偺僉儍儕乕乮儃儘乕乯偵側傝傑偡丅

偱偡偐傜丄崱夞偺寁嶼偺寢壥丄僉儍儕乕僼儔僌偑僙僢僩偝傟傞偙偲偵側傝傑偡偑丄傑偩偙偺抜奒偱偼丄僉儍儕乕僼儔僌傊偺斀塮偼峴傢傟傑偣傫丅

俠俵俹丂俫柦椷偺俿俈偺幨恀偱偡丅

俠俵俹丂俫柦椷偺俿俉偺幨恀偱偡丅

俙俢俢儗僕僗僞偺俴俤俢昞帵偺嵍懁偵偁傞丄俙倓倓俼俢乮墿俴俤俢乯偑揰摂偟偰丄壛嶼偺寢壥乮俤俢乯偑撪晹僨乕僞僶僗偵弌偝傟偰偄傑偡丅

偟偐偟丄俙儗僕僗僞偵偼彂偒崬傒偼峴傢傟偢丄俙儗僕僗僞偼傕偲偺抣傪曐帩偟偰偄傑偡丅

僼儔僌儗僕僗僞偼丄嵍抂偺俽乮僒僀儞乯僼儔僌偑揰摂丄偦偺塃偺倅乮僛儘乯僼儔僌偑徚摂丄偦偺塃偺俫乮僴乕僼僉儍儕乕乯僼儔僌偲丄塃抂偺俠乮僉儍儕乕乯僼儔僌偑揰摂偟傑偟偨丅

俠俵俹丂俫柦椷偺俿俋偺幨恀偱偡丅

俀侽侽俋丏係丏侾俇倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞