昗弨俿俿俴偩偗乮両乯偱CPU傪偮偔傠偆両乮慻棫偰僉僢僩偱偡両乯

(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞俀俆俉夞乶

仠俬俶俼丄俢俠俼偺僥僗僩僾儘僌儔儉偱偡

俵俷倁柦椷偺師偼俬俶俼丄俢俠俼柦椷偺僥僗僩偱偡丅

俁杮栚偺僥僗僩僾儘僌儔儉偱偡丅

俬俶俼丂倰丄俢俠俼丂倰偩偗偱偼側偔偰丄俬俶俼丂俵丄俢俠俼丂俵傕僥僗僩偟傑偡丅

僥僗僩僾儘僌儔儉偺儕僗僩偱偡丅

2009/6/12 7:40 TEST3.TXT

END=40E5

;;; MYCPU80 TEST3

;;; INR DCR

;;; 09/6/11 6/12

;

ORG $4000

;

STCK=$5000

ERBF=$6000

;

4000 310050 LXI SP,STCK

4003 0E00 MVI C,00

4005 C5 PUSH B

4006 F1 POP PSW;CLEAR FLAG REGISTER

;

; INR M DCR M

4007 210050 LXI H,STCK

400A 2B DCX H

400B 36FE MVI M,FE

400D 2B DCX H

400E F9 SPHL

400F 23 INX H

4010 0604 MVI B,04

4012 34 LOOP1:INR M

4013 7E MOV A,M

4014 F5 PUSH PSW

4015 05 DCR B

4016 C21240 JNZ LOOP1

4019 4E MOV C,M

401A 2B DCX H

401B 71 MOV M,C

401C 0604 MVI B,04

401E 35 LOOP2:DCR M

401F 7E MOV A,M

4020 F5 PUSH PSW

4021 05 DCR B

4022 C21E40 JNZ LOOP2

;INR r

4025 0E00 MVI C,00

4027 C5 PUSH B

4028 F1 POP PSW;CLEAR FLAG REGISTER

4029 06FE MVI B,FE

402B 04 INR B

402C 78 MOV A,B

402D F5 PUSH PSW

402E 48 MOV C,B

402F 0C INR C

4030 79 MOV A,C

4031 F5 PUSH PSW

4032 51 MOV D,C

4033 14 INR D

4034 7A MOV A,D

4035 F5 PUSH PSW

4036 5A MOV E,D

4037 1C INR E

4038 7B MOV A,E

4039 F5 PUSH PSW

403A 63 MOV H,E

403B 24 INR H

403C 7C MOV A,H

403D F5 PUSH PSW

403E 6C MOV L,H

403F 2C INR L

4040 7D MOV A,L

4041 F5 PUSH PSW

4042 7D MOV A,L

4043 3C INR A

4044 F5 PUSH PSW

4045 C5 PUSH B

4046 D5 PUSH D

4047 E5 PUSH H

;DCR r

4048 47 MOV B,A

4049 1E00 MVI E,00

404B 1600 MVI D,00

404D D5 PUSH D

404E F1 POP PSW;CLEAR FLAG&A REGISTER

404F 05 DCR B

4050 78 MOV A,B

4051 F5 PUSH PSW

4052 48 MOV C,B

4053 0D DCR C

4054 79 MOV A,C

4055 F5 PUSH PSW

4056 51 MOV D,C

4057 15 DCR D

4058 7A MOV A,D

4059 F5 PUSH PSW

405A 5A MOV E,D

405B 1D DCR E

405C 7B MOV A,E

405D F5 PUSH PSW

405E 63 MOV H,E

405F 25 DCR H

4060 7C MOV A,H

4061 F5 PUSH PSW

4062 6C MOV L,H

4063 2D DCR L

4064 7D MOV A,L

4065 F5 PUSH PSW

4066 7D MOV A,L

4067 3D DCR A

4068 F5 PUSH PSW

4069 C5 PUSH B

406A D5 PUSH D

406B E5 PUSH H

;;;

; CHECK

;INR M DCR M

;

406C 310060 LXI SP,ERBF

406F 210050 LXI H,STCK

4072 2B DCX H

4073 11BD40 LXI D,TBL1END

4076 0612 MVI B,12;=18

4078 1A CKLP1:LDAX D

4079 BE CMP M

407A CA7E40 JZ CKLP1_2

407D E5 PUSH H;ERR

407E 2B CKLP1_2:DCX H

407F 1B DCX D

4080 05 DCR B

4081 C27840 JNZ CKLP1

;INR r

4084 11D140 LXI D,TBL2END

4087 0614 MVI B,14;=20

4089 1A CKLP2:LDAX D

408A BE CMP M

408B CA8F40 JZ CKLP2_2

408E E5 PUSH H;ERR

408F 2B CKLP2_2:DCX H

4090 1B DCX D

4091 05 DCR B

4092 C28940 JNZ CKLP2

;DCR r

4095 11E540 LXI D,TBL3END

4098 0614 MVI B,14;=20

409A 1A CKLP3:LDAX D

409B BE CMP M

409C CAA040 JZ CKLP3_2

409F E5 PUSH H;ERR

40A0 2B CKLP3_2:DCX H

40A1 1B DCX D

40A2 05 DCR B

40A3 C29A40 JNZ CKLP3

;

40A6 E5 PUSH H

40A7 210000 LXI H,$0000

40AA E5 PUSH H

40AB 76 HLT

;

;COMPARE DATA TABLE

;INR M DCR M

40AC 80 TBL1:DB 80

40AD FE DB FE

40AE 94 DB 94

40AF FF DB FF

40B0 44 DB 44

40B1 00 DB 00

40B2 00 DB 00

40B3 01 DB 01

40B4 00 DB 00

40B5 02 DB 02

40B6 00 DB 00

40B7 01 DB 01

40B8 54 DB 54

40B9 00 DB 00

40BA 84 DB 84

40BB FF DB FF

40BC FE DB FE;DCR M

40BD 02 TBL1END:DB 02;INR M

;INR r

40BE 04 DB 04;L

40BF 03 DB 03;H

40C0 02 DB 02;E

40C1 01 DB 01;D

40C2 00 DB 00;C

40C3 FF DB FF;B

40C4 04 DB 04;F

40C5 05 DB 05;A

40C6 00 DB 00

40C7 04 DB 04

40C8 04 DB 04

40C9 03 DB 03

40CA 00 DB 00

40CB 02 DB 02

40CC 00 DB 00

40CD 01 DB 01

40CE 54 DB 54

40CF 00 DB 00

40D0 84 DB 84

40D1 FF TBL2END:DB FF

;DCR r

40D2 FF DB FF;L

40D3 00 DB 00;H

40D4 01 DB 01;E

40D5 02 DB 02;D

40D6 03 DB 03;C

40D7 04 DB 04;B

40D8 80 DB 80;F

40D9 FE DB FE;A

40DA 94 DB 94

40DB FF DB FF

40DC 44 DB 44

40DD 00 DB 00

40DE 00 DB 00

40DF 01 DB 01

40E0 00 DB 00

40E1 02 DB 02

40E2 04 DB 04

40E3 03 DB 03

40E4 00 DB 00

40E5 04 TBL3END:DB 04

;

CKLP1 =4078 CKLP1_2 =407E CKLP2 =4089

CKLP2_2 =408F CKLP3 =409A CKLP3_2 =40A0

ERBF =6000 LOOP1 =4012 LOOP2 =401E

STCK =5000 TBL1 =40AC TBL1END =40BD

TBL2END =40D1 TBL3END =40E5

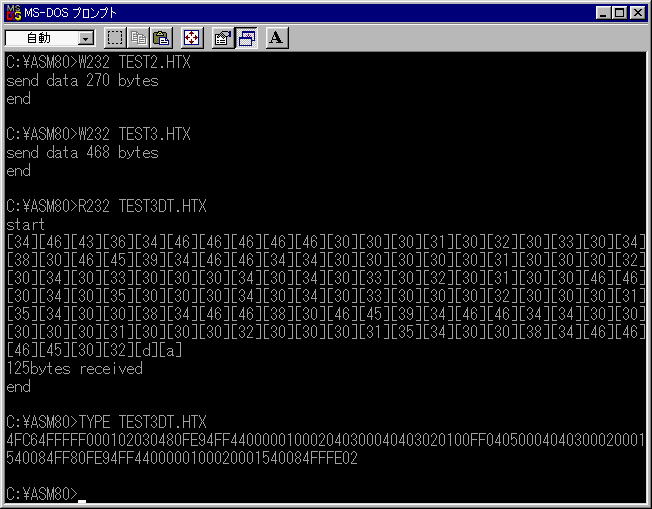

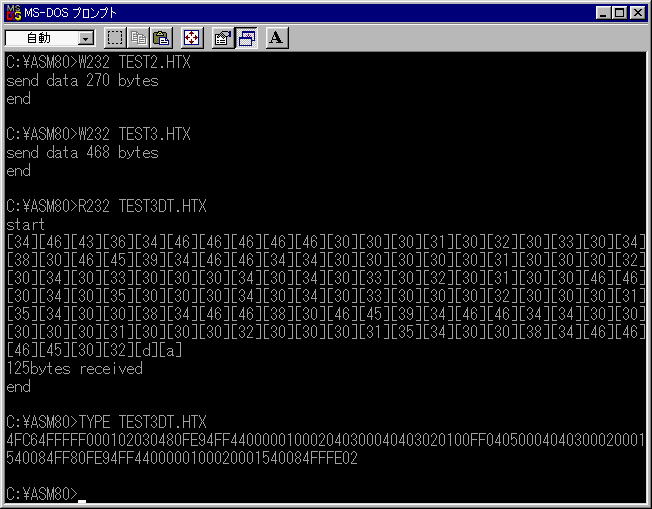

幚峴偟偨寢壥偺抣偼丄傑偨倀俽俛宱桼偱僷僜僐儞偵憲怣偟傑偟偨丅

慜夞丄慜乆夞偺俿俤俽俿俀丄俿俤俽俿侾偲摨偠偱丄寢壥偺抣偑僗僞僢僋偵擖傟傜傟傞弴斣偲丄斾妑僨乕僞偺僥乕僽儖偺暲傃弴偑擖傟懼傢偭偰偄傑偡丅

斾妑偡傞僨乕僞偺僥乕僽儖傪丄寢壥偺抣偺暲傃弴偲摨偠偵偡傞偵偼丄嘆係侽俢俀乣係侽俤俆嘇係侽俛俤乣係侽俢侾嘊係侽俙俠乣係侽俛俢偺弴偵偟傑偡丅

偦偺傛偆偵暲傋懼偊偰斾妑偟偰傒傞偲丄慡偰偺寢壥偑偁傜偐偠傔梡堄偟偨僨乕僞偲堦抳偟偰偄傞偙偲偑傢偐傝傑偡丅

偟偐偟丄偨偩偦偺傛偆偵彂偄偨偩偗偱偼丄傆乕傫丄偦偆側偺丄偱廔傢偭偰偟傑偄偦偆偱偡丅

偙偺僾儘僌儔儉偼愢柧偑昁梫偱偡丅

偄偭偨偄壗傪傗偭偰偄傞偺偱偟傚偆丅

仠俬俶俼丂俵丄俢俠俼丂俵偺僥僗僩

傑偢丄嵟弶偼俬俶俼丂俵丄俢俠俼丂俵偺僥僗僩偱偡丅

偁偲偱僠僃僢僋偑偱偒傞傛偆偵丄俬俶俼丂俵偺偨傔偵偼丄僗僞僢僋僩僢僾偺係俥俥俥傪丄偦偟偰俢俠俼丂俵梡偵偼偦偺師偺係俥俥俤傪巊偄傑偡丅

嵟弶偵係俥俥俥傪俫俴偵擖傟偰乮偮傑傝俵偺傾僪儗僗偼係俥俥俥偵側傝傑偡乯丄偦偙偵弶婜抣俥俤傪擖傟傑偡乮係侽侽俈乣係侽侽俠乯丅

慜夞偺俵俷倁丄俵倁俬柦椷偼僼儔僌偑曄壔偟側偄柦椷偱偟偨偑丄俬俶俼丄俢俠俼柦椷偼僼儔僌偑曄壔偟傑偡丅

偱偡偐傜寢壥偺抣傪妋擣偡傞偲偲傕偵丄僼儔僌偺曄壔傕妋擣偡傞昁梫偑偁傝傑偡丅

弶婜抣偲偟偰俥俤偺傛偆側曄側抣傪慖傫偩偺偼偦偺偨傔偱偡丅

俬俶俼柦椷傪孞傝曉偟幚峴偡傞偙偲偵傛偭偰丄俵偺抣偼俥俤仺俥俥仺侽侽仺侽侾仺侽俀偺傛偆偵曄壔偟傑偡丅

抣偺曄壔偲偲傕偵僼儔僌傕曄壔偟傑偡丅

庡梫側僼儔僌偱偁傞俽乮僒僀儞乯僼儔僌偲倅乮僛儘乯僼儔僌偺曄壔偑妋擣偱偒傞傛偆偵丄偲偄偆偙偲偱偦偺抣傪慖傃傑偟偨丅

俬俶俼丂俵傪係夞孞傝曉偟幚峴偡傞偛偲偵丄俵俷倁丂俙丆俵偱寢壥傪俙儗僕僗僞偵擖傟偨偆偊偱僼儔僌偲堦弿偵僗僞僢僋偵曐懚偟傑偡乮係侽侽俢乣係侽侾俉乯丅

俫俴傪亅侾偟偰俥俥俥俤傪俵偺傾僪儗僗偵偟偨偆偊偱丄嵟屻偺寢壥偺抣偺侽俀傪丄怴偟偄俵偵擖傟傑偡乮係侽侾俋乣係侽侾俛乯丅

崱搙偼俢俠俼丂俵傪係夞孞傝曉偟傑偡丅

寢壥偺抣偼丄侽俀仺侽侾仺侽侽仺俥俥仺俥俤偲曄壔偟傑偡丅

偙傟傕俬俶俼丂俵偲摨偠傛偆偵丄俙儗僕僗僞偵擖傟偨偆偊偱僼儔僌偲偲傕偵僗僞僢僋偵曐懚偟傑偡乮係侽侾俠乣係侽俀係乯丅

僗僞僢僋偼係俥俥俥偐傜慜偵岦偐偭偰徚旓偝傟偰偄偒傑偡丅

偱偡偐傜柦椷偑幚峴偝傟偨弴偵寢壥偺婰榐傪妋擣偟傛偆偲偡傞偲丄僗僞僢僋傪屻傠偐傜尒偰偄偔偙偲偵側傝傑偡丅

僷僜僐儞夋柺偺壓偺曽丄倀俽俛宱桼偱庴怣偟偨寢壥偺抣偼丄堦斣嵟屻偑傾僪儗僗係俥俥俥偵側偭偰偄傑偡丅

偦偙偐傜媡偵尒偰偄偒傑偡丅

堦斣嵟屻偼侽俀偱偡丅

偙偙偼俬俶俼丂俵柦椷偱俵偲偟偰巊偭偨傾僪儗僗偱偡丅

俥俤偐傜巒傑偭偰丄係夞俬俶俼丂俵傪孞傝曉偟傑偟偨偐傜丄寢壥偼侽俀偱偡丅

偦偺慜偼俥俤偵側偭偰偄傑偡丅

偙偙偼俢俠俼丂俵柦椷偱俵偲偟偰巊偭偨傾僪儗僗偱偡丅

侽俀偐傜巒傑偭偰係夞俢俠俼丂俵傪孞傝曉偟傑偟偨偐傜丄寢壥偼俥俤偱偡丅

偦偺慜偐傜俉僶僀僩偼俬俶俼丂俵傪侾夞幚峴偡傞偛偲偵丄寢壥偺抣偲僼儔僌傪曐懚偟偨偲偙傠偱偡丅

侾侽侽俀侽侽侽侾俆係侽侽俉係俥俥丂偺俉僶僀僩偱偡丅仼岆婰偑偁傝傑偡乮掶惓丂侽侽侽俀侽侽侽侾俆係侽侽俉係俥俥乯

偝傜偵偦偙偐傜慜偺俉僶僀僩偼俢俠俼丂俵傪侾夞幚峴偡傞偛偲偵丄寢壥偺抣偲僼儔僌傪曐懚偟偨偲偙傠偱偡丅

俉侽俥俤俋係俥俥係係侽侽侽侽侽 丂偺俉僶僀僩偱偡丅仼岆婰偑偁傝傑偡乮掶惓丂俉侽俥俤俋係俥俥係係侽侽侽侽侽侾乯

俉係俥俥偼俉係偑僼儔僌偱俥俥偑寢壥偺抣偱偡丅

俥俥偼晧悢側偺偱俽乮僒僀儞乯僼儔僌偑俷俶偵側偭偰偄傑偡丅

偦偺慜偺俆係侽侽偼俆係偑僼儔僌偱侽侽偑寢壥偺抣偱偡丅

倅乮僛儘乯僼儔僌偲俫乮僴乕僼僉儍儕乕乯僼儔僌偑俷俶偵側偭偰偄傑偡丅

俬俶俼丄俢俠俼柦椷偱偼丄俠乮僉儍儕乕乯僼儔僌偼曄壔偟傑偣傫丅

仠俉侽俉侽偺僼儔僌

僼儔僌偵偮偄偰偼乵戞俆俋夞乶偱愢柧偟偰偄傑偡丅

偱傕傕偆偢偄傇傫帪娫偑宱偭偰偟傑偄傑偟偨偐傜丄嶲峫傑偱偵丄僼儔僌儗僕僗僞偺拞偺奺僼儔僌偺價僢僩埵抲傪壓偵帵偟傑偡丅

| bit7 |

bit6 |

bit5 |

bit4 |

bit3 |

bit2 |

bit1 |

bit0 |

| S |

Z |

- |

H |

- |

P |

- |

C |

偙偺楢嵹婰帠傪嵟弶偐傜偢偭偲偍撉傒偄偨偩偄偰偄傞曽偱丄側偍巹偲堘偭偰婰壇椡偺傛傠偟偄曽偺拞偵偼丄偙偙傑偱偍撉傒偄偨偩偄偰丄偁傟偉丠偲偍巚偄偵側傜傟偨曽傕偄傜偭偟傖傞偐傕偟傟傑偣傫丅

偊偊丅

偠偮偼丄偦偆側傫偱偡丅

偱傕丄偦傟偵偮偄偰偼丄傕偆彮偟偁偲偱偍榖傪偡傞偮傕傝偱偡偐傜丄崱偼丄偙偺傑傑偲偄偆偙偲偱丅

仠俬俶俼丂倰偺僥僗僩

係侽俀俆乣係侽係俈偺僾儘僌儔儉偼俬俶俼丂倰偺僥僗僩偱偡丅

婎杮揑偵偼俬俶俼丂俵偺僥僗僩偲摨偠偱偡丅

嵟弶偵俛儗僕僗僞偵俥俥傪擖傟偰丄俬俶俼丂俛傪幚峴偟傑偡丅

寢壥偺抣傪俙儗僕僗僞偵擖傟偰丄僼儔僌偲偲傕偵僗僞僢僋偵曐懚偟傑偡丅

師偵摨偠寢壥偺抣傪俠儗僕僗僞偵擖傟偰丄崱搙偼俬俶俼丂俠傪幚峴偟傑偡丅

偙偺傛偆偵俛仺俠仺俢仺俤仺俫仺俴仺俙偺弴偵俬俶俼丂倰傪幚峴偟側偑傜寢壥偺抣偲僼儔僌傪僗僞僢僋偵曐懚偟偰偄偒傑偡丅

嵟屻偵俹倀俽俫丂俛丄俹倀俽俫丂俢丄俹倀俽俫丂俫偱奺儗僕僗僞偺抣傕曐懚偟傑偡丅

寢壥偺抣偼丄

侽係侽俁丂侽俀侽侾丂侽侽俥俥丂侽係侽俆丂侽侽侽係丂侽係侽俁丂侽侽侽俀丂侽侽侽侾丂俆係侽侽丂俉係俥俥偺晹暘偱偡丅

暘偐傝堈偔偡傞偨傔偵俀僶僀僩偢偮偵嬫愗偭偰傒傑偟偨丅

幚峴偝傟偨寢壥偼丄屻傠偐傜慜偵岦偐偭偰偄偔弴偱曐懚偝傟偰偄傑偡丅堦斣屻傠偺俥俥偑俬俶俼丂俛偺寢壥偺抣偱俉係偑僼儔僌偱偡丅

堦斣慜偺侽係侽俁偼堦斣嵟屻偵幚峴偝傟偨俹倀俽俫丂俫偵傛偭偰曐懚偝傟偨丄俴儗僕僗僞偺抣乮侽係乯偲俫儗僕僗僞偺抣乮侽俁乯偱偡丅

仠俢俠俼丂倰偺僥僗僩

係侽係俉乣係侽俇俛偺僾儘僌儔儉偼俢俠俼丂倰偺僥僗僩偱偡丅

婎杮揑偵偼俢俠俼丂俵偺僥僗僩偲摨偠偱偡丅

俬俶俼偺僥僗僩偱偺嵟屻偺抣偼俙儗僕僗僞偺侽俆偱偡丅

偦偺侽俆傪俛儗僕僗僞偵擖傟偰俢俠俼丂俛偺幚峴偐傜奐巒偟傑偡丅

嵟弶偵俛儗僕僗僞偵侽俆傪擖傟偰丄俬俶俼丂俛傪幚峴偟傑偡丅

寢壥偺抣傪俙儗僕僗僞偵擖傟偰丄僼儔僌偲偲傕偵僗僞僢僋偵曐懚偟傑偡丅

師偵摨偠寢壥偺抣傪俠儗僕僗僞偵擖傟偰丄俢俠俼丂俠傪幚峴偟傑偡丅

偙偺傛偆偵俛仺俠仺俢仺俤仺俫仺俴仺俙偺弴偵俢俠俼丂倰傪幚峴偟側偑傜寢壥偺抣偲僼儔僌傪僗僞僢僋偵曐懚偟偰偄偒傑偡丅

嵟屻偵俹倀俽俫丂俛丄俹倀俽俫丂俢丄俹倀俽俫丂俫偱奺儗僕僗僞偺抣傕曐懚偟傑偡丅

寢壥偺抣偼丄

俥俥侽侽丂侽侾侽俀丂侽俁侽係丂俉侽俥俤丂俋係俥俥丂係係侽侽丂侽侽侽侾丂侽侽侽俀丂侽係侽俁丂侽侽侽係偺晹暘偱偡丅

偝偒傎偳偲摨偠傛偆偵俀僶僀僩偢偮偵嬫愗傝傑偟偨丅

幚峴偝傟偨寢壥偼丄屻傠偐傜慜偵岦偐偭偰偄偔弴偱曐懚偝傟偰偄傑偡丅堦斣屻傠偺侽係偑俢俠俼丂俛偺寢壥偺抣偱侽侽偑僼儔僌偱偡丅

堦斣慜偺俥俥侽侽偼堦斣嵟屻偵幚峴偝傟偨俹倀俽俫丂俫偵傛偭偰曐懚偝傟偨丄俴儗僕僗僞偺抣乮俥俥乯偲俫儗僕僗僞偺抣乮侽侽乯偱偡丅

俀侽侽俋丏俇丏俀係倳倫倢倧倎倓

俀侽侾侾丏俆丏侾岆婰掶惓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞