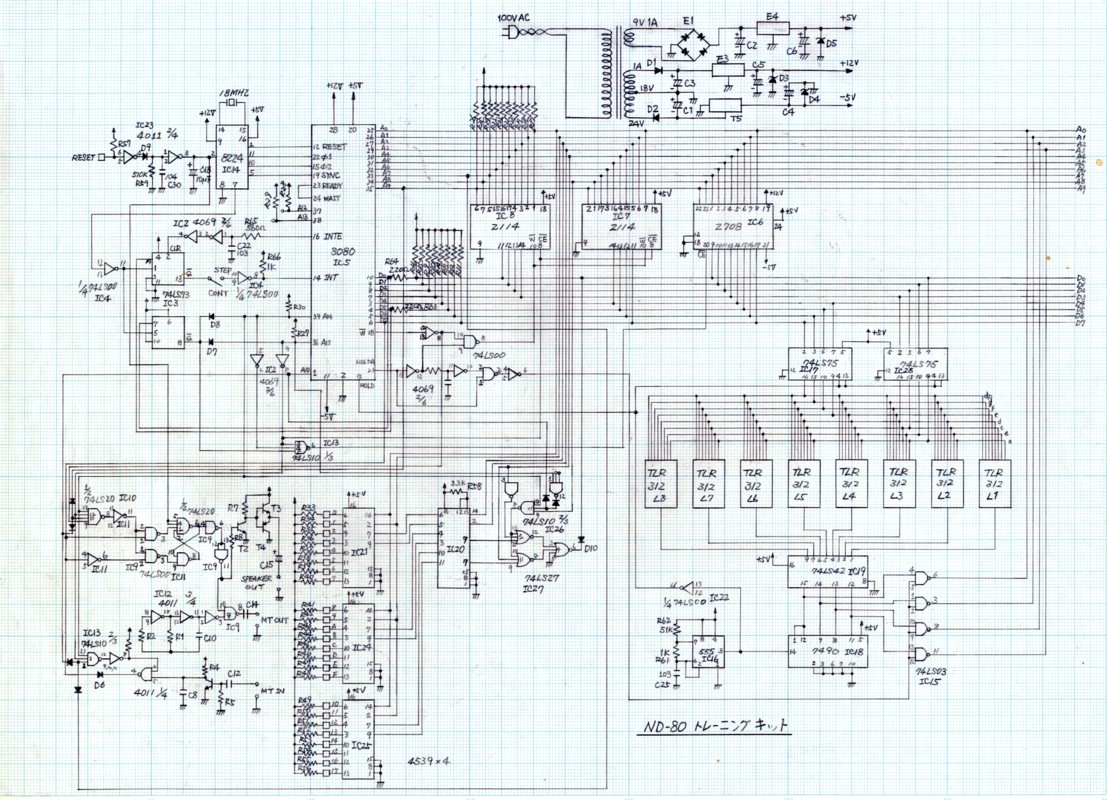

昗弨俿俿俴偩偗乮両乯偱CPU傪偮偔傠偆両乮慻棫偰僉僢僩偱偡両乯

(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞係俆俀夞乶

仠寁嶼偑崌偄傑偣傫丠丠丠

慜夞偼丄

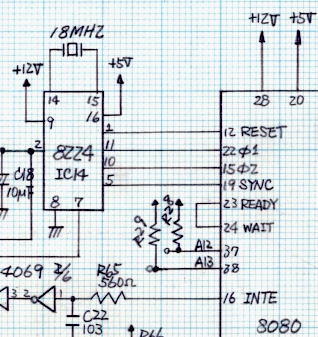

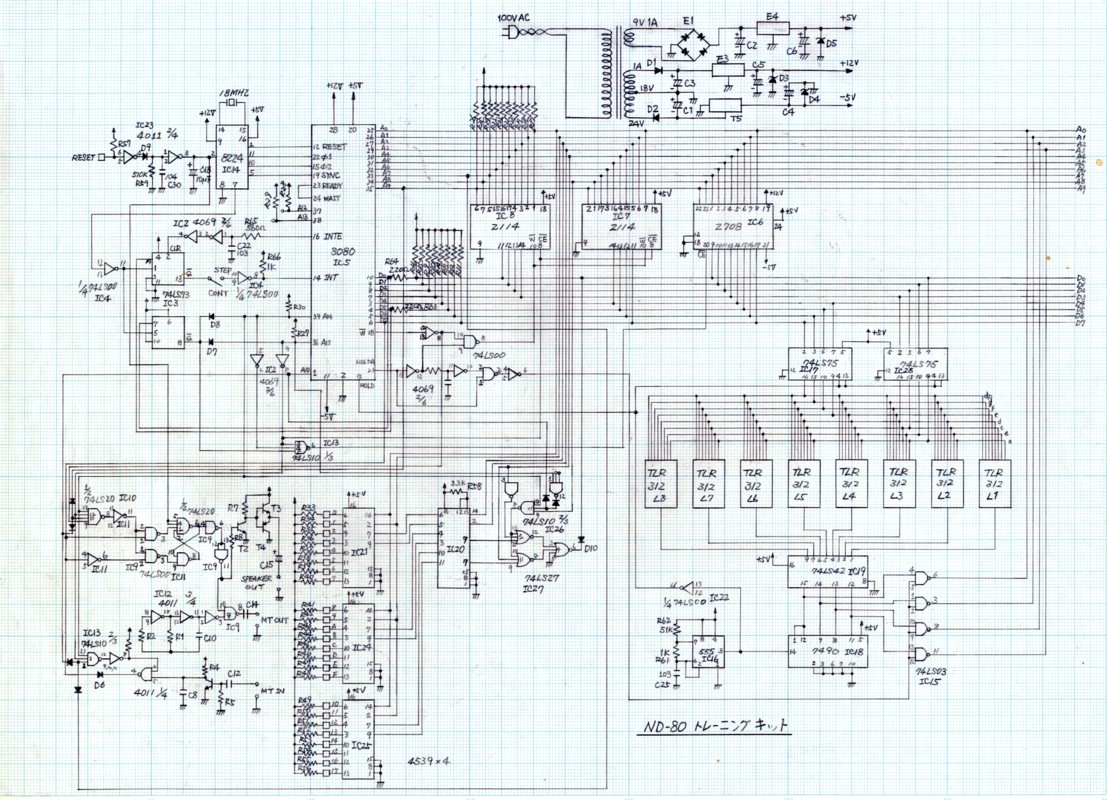

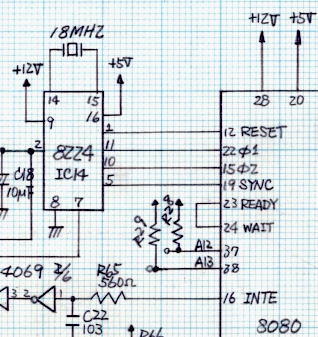

俿俲俉侽偺俠俹倀僋儘僢僋偑俀俵俫倸偩偭偨偺偵丄倅俉侽斉俿俲俉侽儃乕僪乮俶俢俉侽倅俫乯偺俠俹倀僋儘僢僋偑係俵俫倸側偺偱丄儌僯僞僾儘僌儔儉偺僠儍僞儕儞僌僞僀儅乕傪曗惓偟傑偟偨丅

偲偄偆偍榖傪偄偨偟傑偟偨丅

俠俹倀僋儘僢僋偑俀俵俫倸偺儃乕僪乮俿俲俉侽乯偱丄俋倣倱倕們偺僞僀儅乕僾儘僌儔儉傪丄俠俹倀僋儘僢僋偑係俵俫倸偺儃乕僪乮俶俢俉侽倅俫乯偱偦偺傑傑幚峴偟偨傜丄係丏俆倣倱倕們僞僀儅乕偵側偭偰偟傑偄傑偡丅

僉乕擖椡帪偺僠儍僞儕儞僌偵傛傞岆擖椡傪夞旔偡傞偨傔偺僞僀儅乕儖乕僠儞偱偡偐傜丄偦傟偑敿暘偺帪娫偵側偭偰偟傑偭偰偼丄巊偄暔偵側傜側偄壜擻惈偑偁傝傑偡偐傜丄僋儘僢僋傪係俵俫倸偵偟偰傕丄栺俋倣倱倕們偵側傞傛偆偵掕悢傪彂偒姺偊偨偺偱偡丅

倅俉侽偼俉侽俉侽偺柦椷傪偦偺傑傑幚峴偱偒傑偡偐傜丄扨弮偵峫偊偨傜丄帪娫懸偪偺儖乕僾夞悢傪攞偵偡傟偽寁嶼偑崌偆丄偼偢偱偟偨丅

擮偺偨傔偵丄偲偄偆偙偲偱丄僆儕僕僫儖偺傑傑偺僞僀儅乕儖乕僠儞偺奺柦椷偺幚峴僋儘僢僋悢傪慡晹寁嶼偟偰丄偦偙偐傜俢俀偺僒僽儖乕僠儞偺幚峴帪娫偑俋倣倱倕們偵側傞傛偆偵丄孞傝曉偟夞悢傪寁嶼偱媮傔偰丄摼傜傟偨抣偑丄

傾僪儗僗侽俀俢俥偺俵倁俬丂俤丆俀俁

偱偟偨丅

侾俇恑悢偺俀俁偼廫恑悢偱偼俁俆偱偡丅

偲偙傠偑丅

僆儕僕僫儖偺俿俲俉侽儌僯僞僾儘僌儔儉偺偦偺晹暘偼丄

俵倁俬丂俤丆侽俠

偩偭偨偺偱偡丅

侽俠偼廫恑悢偱偼侾俀偱偡丅

偁傟傑丅寁嶼偑崌偄傑偣傫偱偡偹偊丠

俀俵俫倸偺偲偒偵孞傝曉偟夞悢偑侾俀夞偩偭偨偺偱偡偐傜丄係俵俫倸側傜俀係夞偵側傞偼偢偱偟傚偆丅

偦傟偑係俵俫倸偩偲俁俆夞偵側偭偰偟傑偆偺偱偡傛偍丅

俆妱嬤偔傕堘偆偠傖偁傝傑偣傫偐偁丅

側偤偊丠

俠俹倀僋儘僢僋係俵俫倸偱栺俋倣倱倕們偵側傞傛偆偵寁嶼偱媮傔偰彂偒捈偟偨僞僀儅乕儖乕僠儞傪僥僗僩僾儘僌儔儉傪彂偄偰妋擣偟偰傒偨偲偙傠丄娫堘偄柍偔栺俋倣倱倕們偱偁傞偙偲偼丄僥僗僩僾儘僌儔儉傪幚峴偟偰摼傜傟偨弌椡攇宍偐傜柧傜偐偱偡乮慜夞乵戞係俆侾夞乶偺僆僔儘偺幨恀乯丅

偱偼丄俿俲俉侽儌僯僞僾儘僌儔儉偑娫堘偭偰偄傞偺偐丠

偄傗丄偄偔傜側傫偱傕丄偦傟偼側偄偱偟傚偆傛丅

偳偆偱傕傛偄偙偲偐傕偟傟傑偣傫偑乧丅

偄傗偁丄偙傟偼偳偆偱傕傛偄偙偲偱偼嵪傑偝傟傑偣傫偱偟傚偆丅

傓傓丅擺摼偑偄偒傑偣傫丅

偙偆偄偆偙偲偼丄傗偭傁傝擺摼偑偄偔偲偙傠傑偱丄捛媦偟偰傒偨偔側偭偰偟傑偄傑偡偱偡丅

堦扷丄婥偵側傞偲丄偦偺傑傑偵偟偰偍偔偺偑丄偳偆偵傕婥帩偪偑埆偄偺偱偡傛偹偊丅

偱丅

僆儕僕僫儖偺俿俲俉侽儌僯僞偺僞僀儅乕儖乕僠儞偺奺柦椷偵俉侽俉侽偺僋儘僢僋悢傪摉偰偼傔偰丄幚峴帪娫傪寁嶼偟偰傒傑偟偨丅

偡傞偲丄堄奜側寢壥偵側偭偨偺偱偡丅

;

;CHATTERING TIMER

;

ORG $02DD

02DD 1624 D1:MVI D,24;WAIT 1/2 BIT TIME 4.5112MSEC (7)

02DF 1E0C MVI E,0C (7)

02E1 1D DCR E (5)

02E2 C2E102 JNZ $-1 (10)

02E5 15 DCR D (5)

02E6 C2DF02 JNZ $-7 (10)

02E9 C9 RET (10)

02EA 1648 D2:MVI D,48;WAIT 1 BIT TIME 9.0176MSEC (7)

02EC C3DF02 JMP D1+2 (10)

02EF 16D8 D3:MVI D,D8;WAIT 3 BIT TIME 27.0176MSEC (7)

02F1 C3DF02 JMP D1+2 (10)

乵弌揟乶俶俤俠擔杮揹婥噴俿俲俉侽儐乕僓乕僘丒儅僯傾儖

慜夞偍尒偣偟偨儕僗僩偺奺柦椷偵僋儘僢僋悢傪彂偒壛偊偰傒傑偟偨丅

偙偺僋儘僢僋悢傪傕偲偵丄幚峴帪娫傪寁嶼偟偰傒傑偟偨丅

俢侾乣俢俁偺儖乕僠儞偼丄偄偢傟傕侽俀俢俥乣侽俀俤俋傪幚峴偟偰偄傑偡丅

偦偙偱傑偢偙偺晹暘偺僩乕僞儖僋儘僢僋悢傪寁嶼偟偰傒傑偟偨丅

侽俠偼廫恑偺侾俀偱偡偐傜丄

侽俀俢俥乣侽俀俤俀偺晹暘偼丄俈亄乮俆亄侾侽乯亊侾俀亖侾俉俈偵側傝傑偡丅

俢俀偺俵倁俬丂俢丆係俉偺係俉偼廫恑偺俈俀偱偡偐傜丄俢俀偐傜侽俀俤俋偺俼俤俿傑偱偺僩乕僞儖僋儘僢僋悢偼丄

俈亄侾侽亄乮侾俉俈亄俆亄侾侽乯亊俈俀亄侾侽亖侾係俆俈侾偱偡丅

俿俲俉侽偺俠俹倀僋儘僢僋偼侾俉丏係俁俀俵俫倸傪俋暘廃偟偰摼傜傟傞俀丏侽係俉俵俫倸偱偡偐傜丄侾僋儘僢僋偼侾乛俀丏侽係俉兪倱倕們偱偡丅

偱偡偐傜俢俀偺幚峴帪娫偼丄侾係俆俈侾亊乮侾乛俀丏侽係俉乯亖俈侾侾係丏俈兪倱倕們乧丅

傗偭傁傝寁嶼偑崌偄傑偣傫乧丅

幚偼偙偺抜奒偱婥偑偮偄偨偙偲偑偁傝傑偡丅

偦傟偼丄俢俠俼柦椷偺僋儘僢僋悢偱偡丅

俉侽俉侽偺俢俠俼柦椷偺僋儘僢僋悢偼丄倅俉侽偲堘偭偰偄偨偺偱偡丅

慜夞偍尒偣偟偨丄俠俹倀僋儘僢僋係俵俫倸梡偵彂偒捈偟偨丄忋偲摨偠僞僀儅乕儖乕僠儞偺儕僗僩偱偡丅

偙偺儕僗僩偵僐儊儞僩偟偰偁傞僋儘僢僋悢偼倅俉侽偺僋儘僢僋悢偱偡丅

;

;CHATTERING TIMER

;

ORG $02DD

02DD 1624 D1:MVI D,24;=36 ck=7 127.75*36+(7+10)*0.25=4603.25microsec

02DF 1E23 D1_2:MVI E,23;=35 ck=7 7+14*35+14=511 0.25*511=127.75microsec

02E1 1D D1_3:DCR E; ck=4

02E2 C2E102 JNZ D1_3; ck=10

02E5 15 DCR D; ck=4

02E6 C2DF02 JNZ D1_2; ck=10

02E9 C9 RET; ck=10

02EA 1648 D2:MVI D,48;=72 127.75*72+(7+10+10)*0.25=9204.75microsec

02EC C3DF02 JMP D1_2

02EF 16D8 D3:MVI D,D8;=216 127.75*216+27*0.25=27600.75microsec

02F1 C3DF02 JMP D1_2

倅俉侽偱偼俢俠俼柦椷偺僋儘僢僋悢偑係偱偁傞偺偵丄俉侽俉侽偱偼俆偵側偭偰偄傑偡丅

俉侽俉侽偼侾僋儘僢僋梋寁偵偐偐偭偰偄傞偺偱偡丅

偟偐偟丄偦偺偙偲偲丄俉侽俉侽偺柦椷僋儘僢僋悢傪偁偰偼傔偰寁嶼偟偨寢壥丄俢俀偺幚峴帪娫偑僆儕僕僫儖偺儌僯僞僾儘僌儔儉偺儕僗僩偵彂偐傟偰偄傞俋丏侽侾俈俇倣倱倕們偵側傜側偄丄偲偄偆偙偲偲偼丄暿偺栤戣偱偡丅

偙傟偼堦懱偳偆偄偆偙偲側偺偱偟傚偆偐丠

仠俿俲俉侽偼儊儌儕傾僋僙僗偵侾僂僃僀僩傪壛偊偰偄偨

偁傜偨傔偰丄俿俲俉侽偺儐乕僓乕僘儅僯傾儖傪撉傫偱傒偰丄偦偆偩偭偨偺偐両偲崌揰偑偄偒傑偟偨丅

愄偼儊儌儕偺傾僋僙僗僞僀儉偑抶偐偭偨偺偱偡丅

摿偵俼俷俵偼抶偐偭偨偙偲傪丄巚偄弌偟傑偟偨丅

俠俹倀僋儘僢僋偑俀俵俫倸偱傕丄俼俷俵傪傾僋僙僗偡傞偺偵偼懍偡偓偨偺偱丄俿俲俉侽偼儊儌儕傪傾僋僙僗偡傞搙偵侾僋儘僢僋傪捛壛偟偰偄偨偺偱偡丅

偡傞偲丄俢俠俼偼侾僶僀僩柦椷偱偡偐傜丄偦偺僋儘僢僋悢偼俆亄侾亖俇偵側傝傑偡偑丄俵倁俬偼俀僶僀僩柦椷側偺偱乮儊儌儕傪俀夞傾僋僙僗偡傞偺偱乯丄僋儘僢僋悢偼俈亄俀亖俋偵側傝丄俰俵俹偼俁僶僀僩柦椷側偺偱丄僋儘僢僋悢偼侾侽亄俁亖侾俁偵側傝傑偡丅

傓傓傓丅

傗偭偲撉傔偰偒傑偟偨丅

傕偆堦搙丄寁嶼偺傗傝捈偟偱偡丅

02DD 1624 D1:MVI D,24;WAIT 1/2 BIT TIME 4.5112MSEC (9)

02DF 1E0C MVI E,0C (9)

02E1 1D DCR E (6)

02E2 C2E102 JNZ $-1 (13)

02E5 15 DCR D (6)

02E6 C2DF02 JNZ $-7 (13)

02E9 C9 RET (13)

02EA 1648 D2:MVI D,48;WAIT 1 BIT TIME 9.0176MSEC (9)

02EC C3DF02 JMP D1+2 (13)

02EF 16D8 D3:MVI D,D8;WAIT 3 BIT TIME 27.0176MSEC (9)

02F1 C3DF02 JMP D1+2 (13)

侽俀俢俥乣侽俀俤俀偺晹暘偼丄俋亄乮俇亄侾俁乯亊侾俀亖俀俁俈偵側傝傑偡丅

俢俀偐傜侽俀俤俋偺俼俤俿傑偱偺僩乕僞儖僋儘僢僋悢偼丄

俋亄侾俁亄乮俀俁俈亄俇亄侾俁乯亊俈俀亄侾俁亖侾俉係俇俈偱偡丅

俢俀偺幚峴帪娫偼丄侾俉係俇俈亊乮侾乛俀丏侽係俉乯亖俋侽侾俈丏侾兪倱倕們両

偍偍両崌偄傑偟偨丅

偲偙傠偱丄忋偺寁嶼偺俀俁俈亄俇亄侾俁偼丄俀俆俇偵側傝傑偡丅偙偙偵侾乛俀丏侽係俉傪妡偗傞偲丄俀俆俇亊乮侾乛俀丏侽係俉乯亖侾俀俆兪倱倕們偵側傝傑偡乮抂悢側偟丄偪傚偆偳偱偡乯丅

偦偺愄丄俿俲俉侽偺夞楬恾傪偼偠傔偰尒偨偲偒丄側傫偱偙傫側敿抂側廃攇悢傪巊偭偰偄傞偺偩傠偆丄偲媈栤偵巚偭偨偺偱偡偑丄偦偺屻偵偙偺僋儕僗僞儖乮侾俉丏係俁俀俵俫倸乯偑俼俽俀俁俀俠夞楬偱巊傢傟偰偄傞偙偲傪抦傝傑偟偨丅

俀偺値忔傪埖偆僶僀僫儕夞楬偲憡惈偑偄偄廃攇悢偩偭偨偺偱偡偹偊丅

梋択偱偡偑丄俿俲俉侽偺儐乕僓乕僘儅僯傾儖偵傛傝傑偡偲丄俉侽俉侽偼俼俤俙俢倄乮俀俁倫倝値乯偲倂俙俬俿乮俀係倫倝値乯傪寢慄偡傞偲丄儊儌儕傾僋僙僗帪偵侾僂僃僀僩乮侾僋儘僢僋乯偑捛壛偝傟傞丄偺偩偦偆偱偡丅

偲偄偆偙偲偼丄倅俉侽傪巊偭偰丄幚峴帪娫偺忋偱傕俿俲俉侽偲偺屳姺惈傪堐帩偡傞偺偼丄帠幚忋柍棟丄偲傑偱偼尵偄傑偣傫偗傟偳丄偦偙傑偱傗傞偐丄偲偄偆偙偲偱偡偐傜丄俠俹倀僋儘僢僋偵偮偄偰偺屳姺惈偼丄慜夞偵傕彂偒傑偟偨傛偆偵丄峫椂偟側偄偙偲偵偟傑偟傚偆丄偲偄偆偺偑惓夝偺傛偆偱偡丅

仠俶俢俉侽偺夞楬恾偑偱偰偒傑偟偨

僠儍僞儕儞僌僞僀儅乕偺栤戣偱丄偁傟偙傟挷傋傛偆偲偟偰丄愄偺帒椏傪偁偝偭偰偄傑偟偨傜丄側傫偲偲偭偔偺愄偵張暘偟偰偟傑偭偨偲巚偭偰偄偨丄弶戙俶俢俉侽偺夞楬恾乮尨杮乯偑弌偰偒傑偟偨丅

愄偼俠俙俢側偳偁傝傑偣傫偱偟偨偐傜丄曽娽巻偵僄儞僺僣偱庤彂偒傪偟偰偄傑偡丅

傓傓傓丅

夰偐偟偄偱偡偹偊丅

徚旓揹棳傪墴偝偊傞偨傔偵丄懍搙偑婥偵側傜側偄晹暘偵偼俠俵俷俽僎乕僩傪巊偭偰偄傑偡丅

俼俷俵偼侾俲俛偺俀俈侽俉丄俼俙俵偼侾俲亊係價僢僩偺俀侾侾係傪巊偭偰偄傑偡丅

儊僇僯僇儖僉乕偑崅偐偭偨偺偱乮崱偱傕寢峔崅偄偱偡偗傟偳乯丄儊僇僯僇儖僉乕偺戙傢傝偵俠俵俷俽僎乕僩傪棙梡偟偨僞僢僠僉乕夞楬偵側偭偰偄傑偡丅

塃忋偵偼僩儔儞僗偲僽儕僢僕惍棳夞楬丄俁抂巕偵傛傞惍棳夞楬傕尒偊傑偡丅

摉帪崅偐偭偨儅儖僠揹尮傕婎斅忋偵忔偣偰偟傑偄傑偟偨丅

僗僉儍僫偵偐偗傛偆偲偟傑偟偨傜丄棤偵擔晅偑彂偄偰偁傝傑偟偨丅

徍榓俆係擭偱偡偐傜丄偊乧偲丄侾俋俈俋擭偱偡偹偊丅

偍偍丄俁侾擭慜偱偡丅

俠俹倀晹暘傪奼戝偟偰傒傑偟偨丅

偆偆丅偙偪傜傕偪傖傫偲丄俼俤俙俢倄偲倂俙俬俿偑寢慄偟偰偁傝傑偟偨丅

俀侽侾侽丏俁丏俋倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞