(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞係俆俁夞乶

仠偨偐偑侾僋儘僢僋偝傟偳侾僋儘僢僋

慜夞丄俿俲俉侽偑儊儌儕傾僋僙僗偵僂僃僀僩傪偐偗偰偄偨偙偲偑傢偐偭偰丄偦傟傪峫椂偟偰僠儍僞儕儞僌僞僀儅乕偺儖乕僠儞偺僋儘僢僋悢傪寁嶼偟捈偟偨偲偙傠丄傗偭偲寁嶼偑崌偄傑偟偨丄偲彂偒傑偟偨丅

嶐斢偦偺婰帠傪倀俹偟偨偲偒偵偼丄傕偆柊偐偭偨偺偱丄乽偍偍両崌偄傑偟偨乿偲彂偄偰丄働儕傪偮偗偰偟傑偭偨偺偱偡偗傟偳乧丅

杮摉偼崌偭偰偄傑偣傫偱偟偨丅

偦偺揰偵偮偄偰偼丄寁嶼傪偟偨帪揰偱婥偑偮偄偰偄傑偟偨乮偦傝傖偁婥偑偮偒傑偡乯丅

抂悢偑崌偭偰偄傑偣傫偱偡丅

巹偺寁嶼偱偼丄俢俀亖俋侽侾俈丏侾兪倱倕們側偺偱偡偗傟偳丄俿俲俉侽儐乕僓乕僘儅僯傾儖偺儕僗僩偱偼丄俋侽侾俈丏俇乮兪倱倕們乯偵側偭偰偄傑偡乮慜夞乵戞係俆俀夞乶偺寁嶼傪嶲徠乯丅

寁嶼偑侽丏俆兪倱倕們崌偄傑偣傫丅

僋儘僢僋俀俵俫倸偱丄侾僋儘僢僋暘偺嵎偱偡丅

嵟弶偼寁嶼岆嵎偩傠偆丄偲巚偭偨偺偱偡偑乧丅

侽俀俢俥偺儖乕僠儞偑偪傚偆偳俀俆俇僋儘僢僋偱丄偦偟偰偦偺幚峴帪娫偑抂悢側偟偺侾俀俆兪倱倕們僕儍僗僩偵側傞偙偲偑傢偐偭偰偟傑偄傑偡偲丅

偆偆丅

偙傟偼丄寁嶼岆嵎側傫偐偠傖偁傝偊側偄丅

偙偙偵偼丄壗偐偑偁傞乧丅

側偤偐偲尵偄傑偡偲丅

侽俀俢俥乣侽俀俤俇偺儖乕僠儞傪侾夞幚峴偡傞偺偵偐偐傞幚峴帪娫偑侾俀俆兪倱倕們僕儍僗僩偲偄偆偙偲偼丄偦傟偵俢侾丄俢俀丄俢俁偺孞傝曉偟夞悢傪妡偗傞偲丄奺僞僀儅乕儖乕僠儞偺侾侽侽兪倱倕們扨埵偱偺幚峴帪娫偑偦偺傑傑抂悢柍偟偱媮傑偭偰偟傑偆偐傜偱偡丅

俢侾偺応崌孞傝曉偟夞悢偼俀係俫乮亖俁俇乯側偺偱侾俀俆亊俁俇亖係俆侽侽偵側傝傑偡偟丄

俢俀偼係俉俫乮亖俈俀乯側偺偱侾俀俆亊俈俀亖俋侽侽侽偵側傝傑偡偟丄

俢俁偼俢俉俫乮亖俀侾俇乯側偺偱侾俀俆亊俀侾俇亖俀俈侽侽侽偵側傝傑偡丅

俠俹倀僋儘僢僋偑俀俵俫倸偪傚偆偳偱偼側偔偰俀丏侽係俉俵俫倸偱偁傞偙偲偑丄偙傫側偲偙傠偱惗偒偰偔傞側傫偰丄傑偝偐偙偺偨傔偵僋儕僗僞儖傪侾俉丏係俁俀俵俫倸偵偟偨丄側傫偰偙偲偼側偄偱偟傚偆偐傜丄偙偙偱偪傚偆偳侾俀俆兪倱倕們偑摼傜傟偨偺偼丄偨傑偨傑僕儍僗僩偵側偭偨丄偲偄偆偙偲側偺偱偟傚偆偗傟偳丄偦偙傜偁偨傝偺帠忣偼偲傕偐偔偲偟偰丄偦偺傛偆偵峫偊傞偲丄夆慠抂悢晹暘偩偗偑僋儘乕僘傾僢僾偝傟偰偒傑偡丅

侾侽侽兪倱倕們埲忋傪彍奜偟偰偟傑偆偲丄巆傞偺偼俢侾偼侾侾丏俀兪倱倕們丄俢俀偲俢俁偼侾俈丏俇兪倱倕們偱偡丅

偙偺巆偭偨帪娫偼丄俢侾偵偮偄偰偼俵倁俬偲俼俤俿丄俢俀偲俢俁偵偮偄偰偼丄俵倁俬偲俰俵俹偲俼俤俿偺幚峴帪娫偱偡丅

儊儌儕傾僋僙僗偺僂僄僀僩傪峫椂偡傞偲丄俵倁俬偼俋僋儘僢僋丄俼俤俿偲俰俵俹偼侾俁僋儘僢僋偵側傝傑偡丅

寁嶼傪偟偰傒傑偡丅

俢侾偼俀俀亊乮侾乛俀丏侽係俉乯亖侾侽丏俈係兪倱倕們偱丄俢俀偲俢俁偼俁俆亊乮侾乛俀丏侽係俉乯亖侾俈丏侽俋兪倱倕們偱偡丅

偄偢傟偺応崌傕丄傗偭傁傝俿俲俉侽儐乕僓乕僘儅僯傾儖偺儕僗僩偺悢抣偼丄巹偑寁嶼偵傛偭偰媮傔偨悢抣傛傝傕栺侽丏俆兪倱倕們戝偒偄抣偱偡丅

俢侾乣俢俁偱嫟捠偟偰偄傞柦椷偼丄俵倁俬偲俼俤俿偱偡丅

偆偆丅

偝偰偼丄偳偪傜偐偺柦椷偺僋儘僢僋悢傪娫堘偭偰偟傑偭偨偺偐丅

偟偐偟丄俵倁俬偼侽俀俢俥乣偺儖乕僠儞偱傕巊傢傟偰偄傑偡丅

傕偟傕俵倁俬偺僋儘僢僋悢傪娫堘偊偰偟傑偭偨偲偡傞偲丄偙傫側傢偢偐側嵎偱偼偁傝偊側偄偙偲偵側傝傑偡丅

偍偍丅崱搙偙偦丄杮摉偵尒偊偰偒傑偟偨丅

偡傞偲丄斊恖偼丄俼俤俿埲奜偵偼偁傝偊側偄丅

側偺偱偡偑乧丅

乵弌揟乶俬値倲倕倢幮乽俉侽俉侽丂俵倝們倰倧們倧倣倫倳倲倕倰丂俽倷倱倲倕倣倱丂倀倱倕倰乫倱丂俵倎値倳倎倢丂俽倕倫倲倕倣倐倕倰丂侾俋俈俆乿

偙偺俉侽俉侽倀倱倕倰乫倱丂俵倎値倳倎倢偼乵戞俈俈夞乶偱偛徯夘傪偄偨偟傑偟偨丅

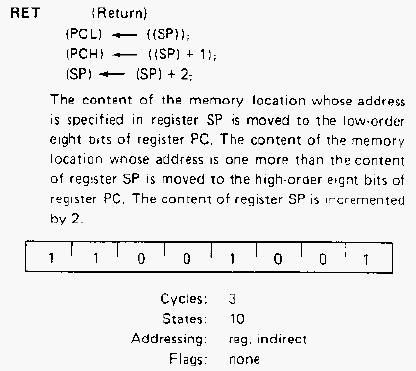

俼俤俿柦椷偺僋儘僢僋悢乮俽倲倎倲倕倱乯偼偪傖傫偲侾侽偵側偭偰偄傑偡丅

巹偑娫堘偊偰偄傞傢偗偱偼偁傝傑偣傫偱偟偨丅

偡傞偲丠

偆偆丅傑偰傛丅偊乧偲丅

俶俤俠偺俉侽俉侽屳姺僠僢僾偲僀儞僥儖偺俉侽俉侽偲偼丄偳偙偐偑堘偭偰偄傞丄偲偄偆傛偆側偙偲傪丄偳偙偐偱撉傫偩偙偲偑偁傞傛偆側乧丅

傂傚偭偲偟偨傜丄偲巚偭偰媣偟傇傝偵偛朘栤傪偝偣偰偄偨偩偒傑偟偨丅

乵戞侾俋夞乶偱偛徯夘偝偣偰偄偨偩偄偨丄 敿摫懱僐儗僋僔儑儞揥帵夛応偝傑偺僒僀僩偱偡丅

傗偭傁傝丅巚偭偨捠傝偱偟偨丅

偙偺僒僀僩偺婰帠偵傛傝傑偡偲丄俶俤俠偺俉侽俉侽屳姺僠僢僾乮兪俹俢俉侽俉侽俙乯偼僀儞僥儖偺僙僇儞僪僜乕僗偱偼側偔偰丄俶俤俠偺撈帺愝寁乮偲偄偭偰傕扨側傞恀帡偩偭偨傛偆偱偡偑乯偵傛傞傕偺丄側偺偩偦偆偱偡乮埲忋丄懛堷偒丄揱暦偱偡乯丅

偦偺偨傔偵丄僆儕僕僫儖偺俉侽俉侽偲偼丄堦晹偺柦椷偺僋儘僢僋悢偑堎側偭偰偄偨丄偺偩偦偆偱偡丅

偍偍丅偦偙丄偦偙傫偲偙偑抦傝偨偐偭偨両

壓婰偼摨僒僀僩偐傜堦晹傪彑庤偵堷梡偝偣偰偄偨偩偒傑偟偨丅