(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞俇係俈夞乶

仠俹俬俠侾俉俥侾係俲俆侽偺俫俬俢僾儘僌儔儉乮俤値倳倣倕倰倎倲倝倧値偦偺俀乯

慜夞偺懕偒偱偡丅

俹俬俠侾俉俥侾係俲俆侽偺俫俬俢僾儘僌儔儉偱丄倀俽俛儂僗僩僐儞僩儘乕儔偐傜憲傜傟偰偔傞俽俤俿倀俹僩乕僋儞僷働僢僩傪専弌偟偨偁偲丄嵟弶偵

們倢倰倖丂倀俬俼

傪幚峴偟偰偄傞偙偲偵偮偄偰偺愢柧偺懕偒偱偡丅

倀俬俼偼倀俽俛娭學偺妱傝崬傒偺忬嫷傪曐帩偡傞儗僕僗僞偱偡丅

價僢僩枅偵堎側傞梫場偺妱傝崬傒傪婰榐曐帩偟傑偡丅

妱傝崬傒忦審偑惉棫偟偨偲偒偵俽俬俤乮俹俬俠撪憻偺倀俽俛僐儞僩儘乕儔乯偵傛偭偰倀俬俼偺偦偺價僢僩偑侾偵側傝傑偡丅

堦搙俽俬俤偵傛偭偰侾偵偝傟偨價僢僩偼丄僾儘僌儔儉偱僋儕傾偡傞傑偱偦偺傑傑曐帩偝傟傑偡丅

俫俬俢僾儘僌儔儉偱丂們倢倰倖丂倀俬俼丂傪幚峴偟偰偄傞偺偼丄倀俬俼儗僕僗僞偺價僢僩俁乮俿俼俶俬俥乯傪僋儕傾偡傞偨傔偱偡丅

偲偄偆偲偙傠傑偱偑慜夞偺愢柧偱偟偨丅

偲偙傠偱丄俫俬俢僾儘僌儔儉偱偼倀俽俛偺偨傔偺妱傝崬傒偼巊偭偰偄傑偣傫丅

妱傝崬傒傪巊偭偰偄側偄乮妱傝崬傒傪僀僱乕僽儖偵偟偰偄側偄乯偺偵倀俬俼偺價僢僩偑俷俶偵側傞偺偐丠

偲偄偆媈栤傪傕偨傟傞偐傕偟傟傑偣傫丅

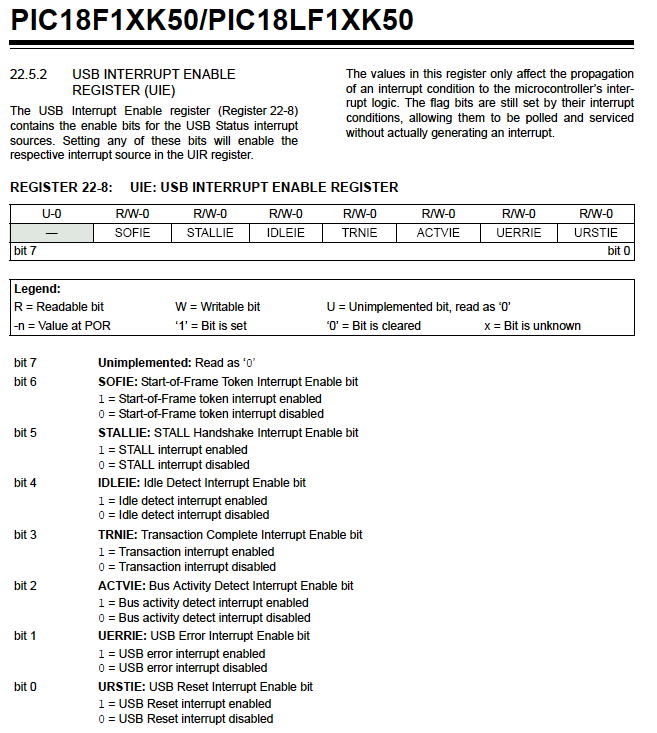

倀俬俼偺價僢僩枅偺妱傝崬傒偵嫋壜傪梌偊傞偺偼倀俬俤儗僕僗僞偱偡丅

仠倀俬俤儗僕僗僞

乵弌揟乶俵倝們倰倧們倛倝倫幮俹俬俠侾俉俥侾係俲俆侽俢倎倲倎俽倛倕倕倲

俿倛倕丂倖倢倎倗丂倐倝倲倱丂倎倰倕丂倱倲倝倢倢丂倱倕倲丂倐倷丂倲倛倕倝倰丂倝値倲倕倰倰倳倫倲丂們倧値倓倝倲倝倧値倱丆倎倢倢倧倵倝値倗丂倲倛倕倣丂倲倧丂倐倕丂倫倧倢倢倕倓丂倎値倓丂倱倕倰倴倝們倕倓丂倵倝倲倛倧倳倲丂倎們倲倳倎倢倢倷丂倗倕値倕倰倎倲倝値倗丂倎値丂倝値倲倕倰倰倳倫倲丏

偲彂偄偰偁傞偲偙傠偑丄偦偺媈栤偵懳偡傞摎偊偱偡丅

倀俬俤偺價僢僩傪侾偵偡傞偲丄倀俬俼偺摨偠價僢僩偵娭學晅偗傜傟偨妱傝崬傒偑嫋壜偝傟傑偡乮弶婜忬懺偱偼慡價僢僩偑侽偱偡乯丅

偦傟偱偼丄倀俬俤偺價僢僩偑侽偺傑傑偺偲偒偵偼倀俬俼偼偳偆側傞偺偐丄偲偄偆偙偲偵偮偄偰偺愢柧傪偟偰偄傞偺偑忋偺暥復偱偡丅

乮幚嵺偺妱傝崬傒偼敪惗偟側偔偰傕乯倀俬俼偺價僢僩偼俷俶偵側傞丄偲偄偆堄枴偺偙偲偑彂偄偰偁傝傑偡丅

俹俬俠偺妱傝崬傒僼儔僌偼丄倀俽俛埲奜偺妱傝崬傒偵偮偄偰傕摨條偺摦嶌傪偟傑偡丅

妱傝崬傒僀僱乕僽儖偵偟側偔偰傕乮偦偺応崌偵偼摉慠幚嵺偺妱傝崬傒摦嶌偼敪惗偟傑偣傫偑乯妱傝崬傒梫場偑敪惗偟偨偙偲傪抦傜偣傞偨傔偺僼儔僌偩偗偼俷俶偵側傝傑偡丅

偦偙傑偱偺偲偙傠偼偛棟夝偄偨偩偄偨偁偲丄偦傟偱偼倀俬俼偺價僢僩俁偼堦懱偳偺傛偆側忬懺偺偲偒偵僙僢僩偝傟傞偺偐丄偲偄偆偙偲偺愢柧偵恑傒傑偡丅

慜夞乮乵戞俇係俇夞乶乯偍尒偣偟傑偟偨俹俬俠侾俉俥侾係俲俆侽偺俢倎倲倎俽倛倕倕倲偺倀俬俼偺愢柧偱偼丄倀俬俼偺價僢僩俁偼

TRNIF:Transaction Complete Interrupt bit

偲彂偄偰偁傝傑偡丅

偦偟偰偦偺價僢僩偼

Processing of pending transaction is complete;read USTAT register for endpoint information

枹幚峴偩偭偨僩儔儞僓僋僔儑儞偑姰椆偟偨乮幚峴偝傟偨乯偲偒偵丄侾偵側傞丄偲彂偄偰偁傝傑偡丅

偝傜偵丄偦偺拲婰偲偟偰乮偙傟偼慜夞偵傕彂偄偨偙偲偱偡偑乯

俠倢倕倎倰倝値倗丂倲倛倝倱丂倐倝倲丂倵倝倢倢丂們倎倳倱倕丂倲倛倕丂倀俽俿俙俿丂俥俬俥俷丂倲倧丂倎倓倴倎値們倕丏

偲彂偄偰偁傝傑偡丅

偟偐偟丄偙傟偩偗偱偼壗傪尵偭偰偄傞偺偐傢偗偑傢偐傝傑偣傫丅

偦偙偱傑偨俹俬俠侾俉俥侾係俲俆侽偺俢倎倲倎俽倛倕倕倲偱倀俽俿俙俿偵偮偄偰尒偰傒傞偙偲偵抳偟傑偡丅

偲偄偆偮傕傝偩偭偨偺偱偡偑丄傑偨傑偨帪娫偑側偔側偭偰偟傑偄傑偟偨丅

偙偺懕偒偼師夞偵偡傞偙偲偵偄偨偟傑偡丅

俀侽侾侽丏侾侽丏俀俈倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞