偲傝偁偊偢丄俠俹倀偺拞怱偲側傞晹暘偼丄偳偆傗傜弌棃偨傛偆偱偡丅偁偲偼丄僈乕僶乕僨乕僞傪婎斅儊乕僇乕偵憲傟偽丄偟偽傜偔懸偮偆偪偵儂儞儌僲偺僾儕儞僩婎斅偵側偭偰丄憲傜傟偰偒傑偡丅

偟偐偟丄偙傟偩偗偱偼丄傑偩俠俹倀傜偟偄偙偲偼壗傕偱偒傑偣傫丅俵俷倁柦椷偑幚峴偱偒傞偩偗偱偡丅

幚偼俵俷倁柦椷偩偗偩偲偄偭偰傕丄柦椷僐乕僪偺偆偪偺偐側傝偺晹暘傪曅晅偗偨偙偲偵側傝傑偡丅

俉侽俉侽偺柦椷僐乕僪偼俉價僢僩偱偡丅偲偄偆偙偲偼丄柦椷偲偟偰巊偆偙偲偺弌棃傞僐乕僪偼侽侽侽侽侽侽侽侽乣侾侾侾侾侾侾侾侾偺俀俆俇屄偲偄偆偙偲偵側傝傑偡丅俉侽俉侽偼偙偺慡偰傪巊偭偰偄傞偺偱偼側偔偰丄偄偔偮偐枹掕媊偺僐乕僪偑偁傝傑偡丅倅俉侽偼偦偺枹掕媊偺僐乕僪偵撈帺偺柦椷傪妱傝摉偰偰偄傞偺偱偡丅偟偐偟丄偦偺偙偲偼丄偙偙偱偼梋択偱偡丅

柦椷僐乕僪偺奺價僢僩偵偼偍偍傑偐側暘椶偺偨傔偺栶妱偑妱傝摉偰偰傜傟偰偄傑偡丅

俵俷倁柦椷偵偼丄柦椷僐乕僪偺忋埵俀價僢僩丄倐倝倲俈偲倐倝倲俇偑侽侾偺僐乕僪丄侽侾侽侽侽侽侽侽乣侽侾侾侾侾侾侾侾偑慡偰妱傝摉偰傜傟偰偄傞偺偱偡丅

側傫偲妱傝摉偰壜擻側慡僐乕僪偺偆偪偺俀俆亾傪俵俷倁柦椷偨偩侾偮偑愯桳偟偰偄傞偺偱偡丅

偄傗侾偮偩偗椺奜偑偁傝傑偡丅侽侾侾侾侽侾侾侽偱偡丅偙傟偼俵俷倁柦椷偺僐乕僪偺栺懇偵廬偊偽丄俵俷倁丂俵丆俵偵側傞偼偢偱偡偑丄俉侽俉侽偵偦偺傛偆側柦椷偼偁傝傑偣傫丅俉侽俉侽偱偼偙偺僐乕僪偼俫俴俿柦椷乮偨偩偪偵幚峴傪掆巭偡傞乯偵妱傝摉偰傜傟偰偄傑偡丅

傑偨偙偺俫俴俿埲奜偵傕丄俵俷倁柦椷偲偟偰幚峴偼偝傟傞偗傟偳丄幚嵺偵偼堄枴偺側偄柦椷僐乕僪傕娷傑傟偰偄傑偡丅

偨偲偊偽侽侾侽侽侽侽侽侽偼丄傾僙儞僽儔僯乕儌僯僢僋偱昞婰偡傟偽丄俵俷倁丂俛丆俛偵側傝傑偡偑乮俛儗僕僗僞偺撪梕傪俛儗僕僗僞偵僐僺乕偡傞乯丄俹俬俠側偳偲偼堘偄丄俉侽俉侽偺俵俷倁偼僼儔僌偵塭嬁傪梌偊傑偣傫偐傜丄偙傟偼丄幚幙揑偵偼俶俷俹乮値倧丂倧倫倕倰倎倲倝倧値丄壗傕偟側偄乯偲摨偠偱偡丅

崱夞偺儊僀儞婎斅偵偼丄俵俷倁丄俫俴俿偺傎偐偵丄偮偄偱偵俵倁俬柦椷傕搵嵹偟傑偟偨丅

俵倁俬乮倣倧倴倕丂倝倣倣倕倓倝倎倲倕乯偲偼丄俉價僢僩儗僕僗僞傑偨偼儊儌儕偵丄柦椷僐乕僪偵懕偔俉價僢僩偺僨乕僞傪揮憲偡傞柦椷偱偡丅

僐乕僪偼侽侽侽侽侽侾侾侽乣侽侽侾侾侾侾侾侽偺俉屄偱偡丅偙傟偵偼俵俷倁偺応崌偲偼堎側傝丄儊儌儕偵懳偡傞柦椷僐乕僪侽侽侾侾侽侾侾侽傕娷傑傟傑偡丅

偙偺儊僀儞婎斅偩偗偱丄慡柦椷僐乕僪偺係暘偺侾埲忋偺摥偒傪偡傞偲尵偭偨偲偙傠偱丄傕偪傠傫丄俵俷倁偲俫俴俿偲俵倁俬偩偗偟偐偱偒側偄偺偱偼丄偲偰傕俠俹倀偲偼尵偊傑偣傫丅

偼偨偟偰偦偺懠偺柦椷偼偪傖傫偲偮偔傞偙偲偑偱偒傞偺偱偟傚偆偐丠

仠巆傝偺夞楬偺婎斅

偝偒偵傕彂偒傑偟偨傛偆偵丄夞楬恾偲偟偰偼偡偱偵俉侽俉侽偺慡婡擻丄柦椷偵偮偄偰偺愝寁偼堦捠傝偼姰椆偟偰偄傑偡丅

偟偐偟丄偦傟傪慡晹幚嵺偵僾儕儞僩婎斅偵幚憰偱偒傞傛偆偵丄嬶懱揑側攝慄嶌嬈傑偱偍偙側偆偲偡傟偽丄偼偨偟偰嵟屻傑偱柍帠傗傝偲偘傞偙偲偑偱偒傞偱偟傚偆偐丠

幚嵺偵儊僀儞婎斅偺嶌嬈傪偟偰傒偰丄憐憸埲忋偵戝曄偩偭偨偙偲偐傜丄崱屻偺嶌嬈偵巹帺恎偑偄偝偝偐晄埨偵側偭偰偒偰偟傑偄傑偟偨丅

偦偙偱丄戞俀偺婎斅偺嶌惉嶌嬈偵偲傝偐偐偭偨偺偱偡偑乧丅

柦椷偺偆偪俵俷倁偑僐乕僪偺偐側傝偺晹暘傪愯傔傞偙偲偼偡偱偵愢柧偟傑偟偨丅傑偨儗僕僗僞孮偺夞楬傕憡摉偺傕偺偵側傞偙偲偵偮偄偰傕丄偡偱偵愢柧偟傑偟偨丅偙傟傜偼嵟弶偵嶌惉偡傞儊僀儞婎斅偵嵹偣傑偡丅

偟偐偟幚偼偲偄偆偐丄傗偼傝偲偄偆偐丄儗僕僗僞傗俵俷倁偵晧偗偢楎傜側偄夞楬偼丄俙俢俢丄俽倀俛側偳偺墘嶼夞楬偱偡丅偙傟偼偦傟偙偦僴儞僷偱偼側偄丅偦傟傕摉慠偱丄偙傟偙偦偑丄傑偝偵俠俹倀偺拞妀偲傕尵偊傞晹暘偩偐傜偱偡丅偙偙偼懡暘戝巇帠偵側傝傑偡丅

偦偙偱丄婎斅偲偟偰偼丄偙偺晹暘偼偁偲夞偟偵偟偰偟傑偄傑偡丅

戞俀偺婎斅偱偼丄俰俵俹丄俠俙俴俴丄俼俤俿偺僌儖乕僾偲俬俶俼丄俢俠俼丄偦傟偵俬俶丄俷倀俿傪拞怱偵峫偊傞偙偲偵偟傑偟偨丅俠俙俴俴丄俼俤俿偺偨傔偵俽俹乮僗僞僢僋億僀儞僞乯偺夞楬傕搊応偟傑偡丅

傑偨俰俵俹丄俠俙俴俴丄俼俤俿偵偼偦傟偧傟僼儔僌偺忬懺偵傛偭偰摦嶌偑堎側傞丄忦審晅柦椷偑娷傑傟偰偄傑偡丅偲偄偆偙偲偱戞俀偺婎斅偵偼僼儔僌儗僕僗僞傕嵹偣側偗傟偽側傝傑偣傫丅

戞俀偺婎斅偺愝寁嶌嬈傪恑傔偰偄偔偆偪偵丄偁傟偉丄偙傟偼丄傑偢偄側偀丄偲偄偆偙偲偵婥偑偮偄偰偟傑偄傑偟偨丅

幚偼婎斅傪暋悢偵暘妱偡傞傛偆偵峫偊傞夁掱偱丄摉弶偼偱偒傞偩偗丄儗僕僗僞傕婡擻傕偟傏偭偰棙梡偱偒傞傕偺偼嬌椡寭梡偱偒傞傛偆側夞楬偵偡傞傛偆偵寁夋偟偰偄傑偟偨丅偦偙偱偼丄奜晹儊儌儕偺偨傔偺傾僪儗僢僔儞僌傪峴偆応崌偺丄俹俠乮僾儘僌儔儉僇僂儞僞乯傗俽俹乮僗僞僢僋億僀儞僞乯丄傑偨偼俫俴儗僕僗僞傗俛俠丄俢俤儗僕僗僞偺抣傪傾僪儗僗僶僗偵弌椡偡傞偨傔偵丄堦搙俉價僢僩偺撪晹僶僗傪宱桼偝偣偰丄奜晹傾僪儗僗僶僗愱梡偺弌椡儗僕僗僞偵憲傝崬傓傛偆偵峫偊偰偄傑偟偨丅

偙偺峫偊曽偩偲丄奺儗僕僗僞偼俉價僢僩偺撪晹僶僗偵偮側偄偱偍偔偩偗偱傛偄偺偱丄夞楬偑娙扨偵側傞偲峫偊偨偐傜偱偡丅偟偐偟丄偙偺峫偊傕丄娒偐偭偨両

幚嵺偵夞楬愝寁傪偡偡傔偰偄偔偲丄偙傟偱偼柦椷偵傛偭偰偼僋儘僢僋偑傗偨傜懡偔側偭偰偟傑偭偰丄壗傪傗偭偰偄傞偺傗傜傢偐傜側偄丄忬懺偵側偭偰偟傑偆偙偲偑傢偐偭偰偒傑偟偨丅傑偁丄偦傟傕丄夞楬偺僩儗乕僯儞僌偺嵽椏偵側傞偐傕丄偲傕巚偭偨偺偱偡偑丄僋儘僢僋悢偑憹偊傞偲偄偆偙偲偼丄偦偺僋儘僢僋傪堐帩丄僐儞僩儘乕儖偡傞夞楬傕憹戝偟傑偡偟丄僞僀儈儞僌偺岆嵎傕柍帇偱偒側偔側傝傑偡乮偙偺僞僀儈儞僌偺岆嵎偵偮偄偰偼丄偄偢傟愢柧偡傞婡夛偑偁傞偐傕偟傟傑偣傫乯丅

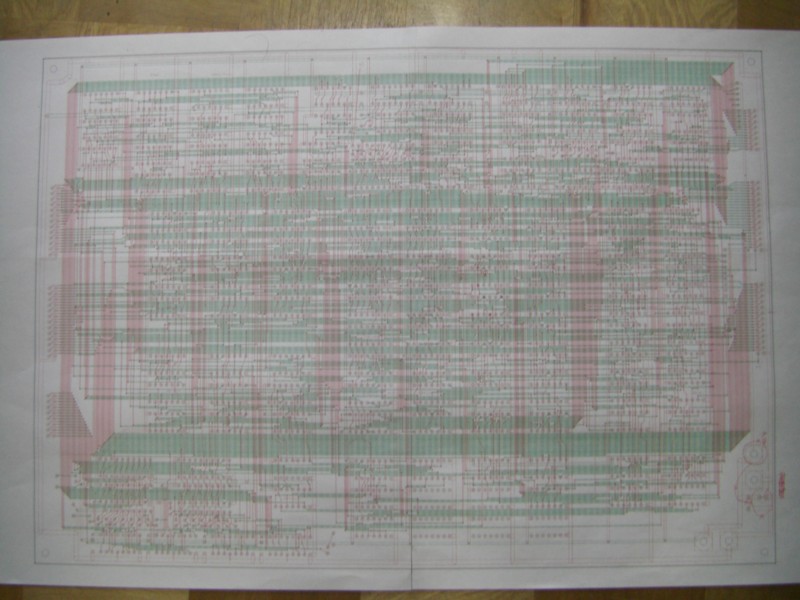

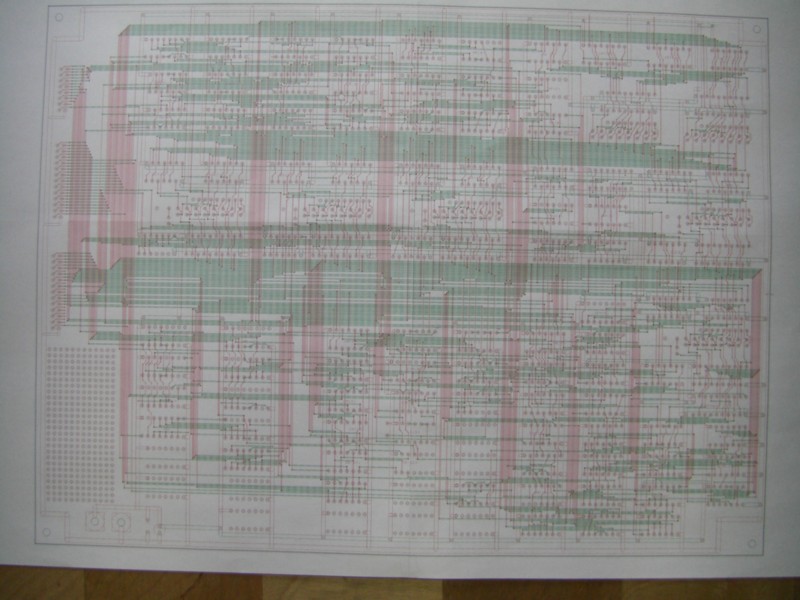

偲偄偆偙偲偱丄嵟弶偐傜愝寁傪傗傝捈偟偰丄奜晹傾僪儗僗僶僗偵偼丄俹俠丄俽俹丄俫俴儗僕僗僞偼捈愙侾俇價僢僩暆偱愙懕偡傞傛偆偵愝寁傪曄峏偟傑偟偨丅偡偱偵儊僀儞婎斅偼偍偍傛偦偱偒偁偑偭偰偄傑偟偨偐傜丄偙偺曄峏偼側偐側偐偵戝曄偱偟偨丅姷傟偨曽偑偙偺儊僀儞婎斅傪偛棗偵側傞偲丄俬俠偺儗僀傾僂僩偑偐側傝棎傟偰偄傞偙偲偵婥偯偐傟傞偐傕偟傟傑偣傫丅偡偱偵攝抲偟廔傢偭偨俬俠傪傓傝傗傝堏摦偟偰丄怴偟偄栚揑偺偨傔偺攝慄傗夞楬傪捛壛偟側偗傟偽側傜側偐偭偨偨傔偱偡丅

戞俀偺婎斅傪嶌傞夁掱偱丄偁傟偉丄傑偢偄側偀丄偲偄偆偙偲偵側偭偨傢偗傕丄偙偺偙偲偵娭學偟偰偄傑偡丅

戞俀偺婎斅偵俽俹傪攝抲偡傞偙偲偼偐側傝慜偺抜奒偱寛傔偰偄傑偟偨丅偟偐偟丄偦偺帪揰偱偼偡偱偵愢柧偟偨傛偆偵丄俽俹偐傜奜晹傾僪儗僗僶僗傊偼丄俉價僢僩偺撪晹僶僗傪宱桼偟偰峴偆丄偮傕傝偱偟偨丅

偙傟偼偦偺屻偵曄峏偟偰丄俹俠丄俽俹丄俫俴儗僕僗僞偐傜偼捈愙奜晹傾僪儗僗僶僗偵弌椡偡傞傛偆偵峫偊傪偁傜偨傔偨偺偱偟偨偑乮偙偺偙偲傕偡偱偵愢柧偟傑偟偨乯丄偦傟傪偡偭偐傝朰傟偰儊僀儞婎斅偺拞偩偗懳嶔偟偰丄廔傢偭偨丄廔傢偭偨丄偲巚偭偰偄偨偺偱偡丅

戞俀偺婎斅忋偵偁傞俽俹乮僗僞僢僋億僀儞僞乯偐傜儊僀儞婎斅忋偺奜晹傾僪儗僗僶僗偲偺愙揰傑偱偺愙懕儔僀儞偑柍偄乮両乯偙偲偵婥偑偮偒傑偟偨丅側傫偲丄俙侽乣俙侾俆偺侾俇杮傕偺儔僀儞偱偡丅

偙傟偵婥偑偮偐側偄偱丄儊僀儞婎斅傪愭偵敪拲偟偰偄偨傜丄側偐側偐偵偮傜偄偙偲偵側偭偰偄傑偟偨丅

傗偭傁傝丄愭偵儊僀儞婎斅偩偗敪拲偟偰偍偄偰丄偦偺娫偵備偭偔傝巆傝偺婎斅傪愝寁偟傛偆丄側偳偲偄偆峫偊偼娒偐偭偨両偺偱偡丅

妎屽傪偒傔偰丄巆傝偺婎斅偺愝寁傕偡偡傔傞偙偲偵偟傑偟偨丅

偡傞偲丄傗偭傁傝丄摉弶婘忋偱巚偭偰偄偨傛傝傕丄婎斅偺僒僀僘偑挻僨僇偔両側偭偰偟傑偆偙偲偑丄偩傫偩傫偲尒偊偰偒傑偟偨丅

偲傝偁偊偢偺嶌嬈偺搑拞偱傕丄戞俁偺婎斅丄偮傑傝俙俢俢側偳偺墘嶼傪拞怱偲偡傞夞楬婎斅偼丄偐側傝戝偒偔側偭偰偟傑偆偙偲偑梊憐偱偒傑偟偨丅偙傟偼俀俁侽倣倣妏偱傕偲偰傕儉儕偱俀俁侽倣倣亊俁侾侽倣倣偲偄偆偙偲偵側偭偰偟傑偄傑偟偨両乮晛捠僾儕儞僩婎斅偼侾倣妏偺掕広偺儃乕僪偐傜愗傝弌偡偺偱丄嶌嬈儘僗傪尒崬傓偲俀俁侽倣倣偺忋偼俁侾侽倣倣偵側偭偰偟傑偆偺偱偡乯

偳偆傗傜偦傟偱傕僷儞僋偟偦偆偩丄偲偄偆帠懺偵側偭偰丄摉弶偺梊掕傪傑偨傑偨曄峏偟丄偱偒傞偩偗懡偔偺柦椷夞楬傪戞俀偺婎斅偵堏摦偡傞偙偲偵偟傑偟偨丅偙偺抜奒偱偼戞俀偺婎斅傕俀俁侽倣倣妏偱傎傏嶌恾偑姰椆偟偰偄偨偺偱偡偑乧丅偄偔傜側傫偱傕偙傫側戝偒側婎斅傪係枃傕偮側偖側偳偲偰傕峫偊傜傟側偄丅側傫偲偐俁枃偵偍偝傔偨偄乧丅偲偄偆偙偲偱丄傑偨傕傗媰偔媰偔戞俀偺婎斅傪曄峏偟偰丄嵟廔揑偵偼戞俀丄戞俁偺婎斅偲傕丄側傫偲俀俁侽倣倣亊俁侾侽倣倣偲偄偆嫄戝側婎斅偵側偭偰偟傑偄傑偟偨両

偄偔傜側傫偱傕偙傫側婎斅丄偙偺傑傑慻棫僉僢僩偵偡傞偺偼丄偲偰傕儉儕偱偡傛偹両

偦傟偵偮偄偰偼丄傑偨偁傜偨傔偰丄峫偊偰傒傑偡丅傕偆彮偟彫偝偄婎斅偵暘妱偟偰丄婡擻傕惍棟偟偰丄偲傝偁偊偢傕偆彮偟彫偝偔偰傕婎杮揑側摦嶌偑偱偒傞傛偆側僉僢僩偵偱偒傟偽丄側偳丄岺晇偺巇曽傕偁傞偐傕偟傟傑偣傫丅

偣偭偐偔偙偙傑偱嶌嬈偟偰偒偨偺偱偡偐傜丄偲傝偁偊偢丄嶌傞偩偗偼偮偔傞偙偲偵偟偨偄偲巚偄傑偡丅

偐偔偟偰丄摉弶丄偲傝偁偊偢儊僀儞婎斅偩偗傑偢愭偵偮偔偭偰乧丄偲偄偆偮傕傝偩偭偨偺偑丄偦偆傕偄偐側偄偧丄偲偄偆偙偲偵側偭偰丄寢嬊偺偲偙傠丄戞俀丄戞俁偺婎斅偵偮偄偰傕丄堦墳偺婎斅愝寁傑偱丄姰椆偝偣偰偟傑偭偨偺偱偡丅

偑乧丅偟偐偟丅

偲傫偱傕側偄偙偲偵丄崱丄婥偑偮偄偰偟傑偄傑偟偨乧丅