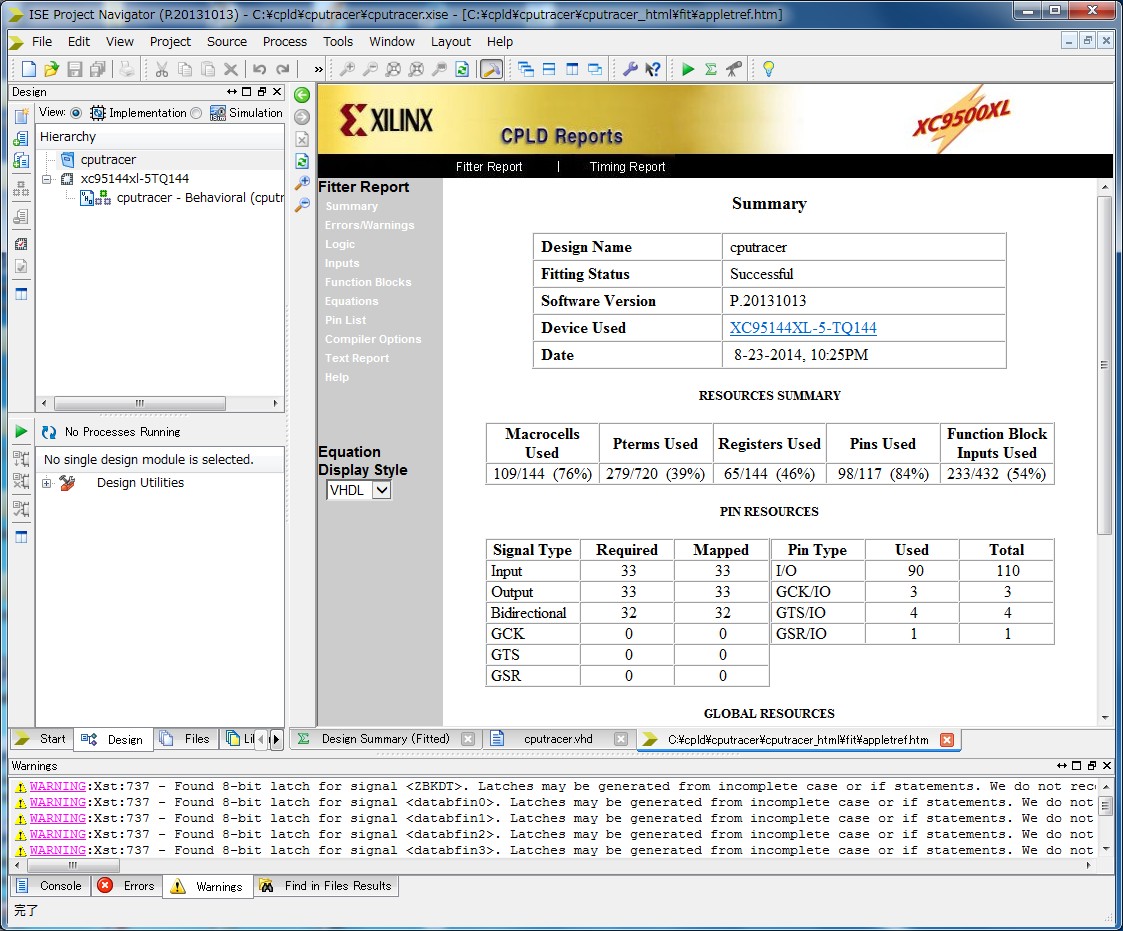

--- cpu tracer

--- from test9t3 14/8/3 8/4 8/5 8/6 8/7 8/8

---

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity cputracer is

PORT (CPUDATA:in std_logic_vector(7 downto 0);

CPUADRSL:in std_logic_vector(7 downto 0);

CPUADRSH:in std_logic_vector(7 downto 0);

OPFTCH:in std_logic;

REGWR:in std_logic;

MRD:in std_logic;

MWR:in std_logic;

IORD:in std_logic;

IOWR:in std_logic;

BUSRQ:out std_logic;

ZBKSTB:out std_logic;

ZBKRDY:in std_logic;

AN :out std_logic_vector(16 downto 0);

RES :in std_logic;

MCLK :out std_logic;

GW:out std_logic;

OE:out std_logic;

ADSC:out std_logic;

CE3:out std_logic;

CPUCTRL2OUT: out std_logic;

CPUCTRL2IN: in std_logic;

ZBKDT :out std_logic_vector(7 downto 0);

MDT0 :inout std_logic_vector(7 downto 0);

MDT1 :inout std_logic_vector(7 downto 0);

MDT2 :inout std_logic_vector(7 downto 0);

MDT3 :inout std_logic_vector(7 downto 0));

attribute PIN_ASSIGN :string;

attribute PIN_ASSIGN of CPUDATA:signal is "118,117,116,115,113,112,111,110";

attribute PIN_ASSIGN of CPUADRSL:signal is "129,128,126,125,124,121,120,119";

attribute PIN_ASSIGN of CPUADRSH:signal is "137,136,135,134,133,132,131,130";

attribute PIN_ASSIGN of OPFTCH:signal is "138";

attribute PIN_ASSIGN of REGWR:signal is "139";

attribute PIN_ASSIGN of MRD:signal is "143";

attribute PIN_ASSIGN of MWR:signal is "2";

attribute PIN_ASSIGN of IORD:signal is "3";

attribute PIN_ASSIGN of IOWR:signal is "4";

attribute PIN_ASSIGN of BUSRQ:signal is "5";

attribute PIN_ASSIGN of ZBKSTB:signal is "140";

attribute PIN_ASSIGN of ZBKRDY:signal is "142";

attribute PIN_ASSIGN of MCLK:signal is "98";

attribute PIN_ASSIGN of OE:signal is "96";

attribute PIN_ASSIGN of ADSC:signal is "95";

attribute PIN_ASSIGN of CE3:signal is "10";

attribute PIN_ASSIGN of CPUCTRL2OUT:signal is "9";

attribute PIN_ASSIGN of CPUCTRL2IN:signal is "7";

attribute PIN_ASSIGN of ZBKDT:signal is "103,102,101,100,104,105,106,107";

attribute PIN_ASSIGN of AN:signal is "71,70,69,68,66,64,61,93,94,11,12,31,32,33,34,35,38";

attribute PIN_ASSIGN of RES:signal is "6";

attribute PIN_ASSIGN of MDT0:signal is "81,80,79,78,77,76,75,74";

attribute PIN_ASSIGN of MDT1:signal is "92,91,88,87,86,85,83,82";

attribute PIN_ASSIGN of MDT2:signal is "21,20,19,17,16,15,14,13";

attribute PIN_ASSIGN of MDT3:signal is "30,28,27,26,25,24,23,22";

attribute PIN_ASSIGN of GW:signal is "97";

end cputracer;

architecture Behavioral of cputracer is

constant zero17 : std_logic_vector(17 downto 0) :="000000000000000000";

signal an1:std_logic_vector(17 downto 0):=zero17;

signal databf0:std_logic_vector(7 downto 0);

signal databf1:std_logic_vector(7 downto 0);

signal databf2:std_logic_vector(7 downto 0);

signal databf3:std_logic_vector(7 downto 0);

signal databfin0:std_logic_vector(7 downto 0);

signal databfin1:std_logic_vector(7 downto 0);

signal databfin2:std_logic_vector(7 downto 0);

signal databfin3:std_logic_vector(7 downto 0);

signal clkq:std_logic_vector(2 downto 0):="000";

signal zbkrdymk:std_logic;

signal rwsw:std_logic:='1';

signal cpuctrl:std_logic;

signal adrsupmk:std_logic;

signal adrsupmk1:std_logic;

signal adrsupmk2:std_logic;

signal cpuctrl2:std_logic;

signal clkupmk:std_logic;

signal mclk1:std_logic;

signal mclk2:std_logic;

signal iowr2:std_logic;

signal iord2:std_logic;

signal mwr2:std_logic;

signal mrd2:std_logic;

begin

BUSRQ<=RES and (not an1(17));

mrd2<=(not MRD) and (not REGWR);

cpuctrl<=MWR and IORD and IOWR and (not OPFTCH) and (not mrd2);

zbkrdymk<=an1(17) and ZBKRDY;

ZBKSTB<=not zbkrdymk;

ADSC<='0';

CE3<='0';

rwsw<=an1(17);

AN<=an1(16 downto 0);

cpuctrl2<=(not rwsw) and (not cpuctrl);

CPUCTRL2OUT<=cpuctrl2;

adrsupmk1<=CPUCTRL2IN;

adrsupmk2<=rwsw and clkupmk;

adrsupmk<=adrsupmk1 or adrsupmk2;

mclk1<=(not rwsw) and cpuctrl;

mclk2<=rwsw and (not zbkrdymk);

MCLK<=mclk1 or mclk2;

databf0<=CPUDATA;

databf1<=CPUADRSL;

databf2<=CPUADRSH;

databf3(7)<='1';

databf3(6)<='1';

databf3(5)<=iowr2;

databf3(4)<=iord2;

databf3(3)<=mwr2;

databf3(2)<=not mrd2;

databf3(1)<=not OPFTCH;

databf3(0)<='1';

process (adrsupmk1)

begin

if rising_edge(adrsupmk1) then

iowr2<=IOWR;

iord2<=IORD;

mwr2<=MWR;

end if;

end process;

process (an1(17),clkq,ZBKRDY)

begin

if an1(17)='1' then

if rising_edge(ZBKRDY) then

clkq<=clkq+'1';

end if;

if clkq="111" then

clkq<="000";

end if;

end if;

end process;

process (clkq)

begin

if clkq="110" then

clkupmk<='1';

else

clkupmk<='0';

end if;

end process;

process (RES,adrsupmk)

begin

if RES='0' then

an1<=zero17;

elsif falling_edge(adrsupmk) then

an1<=an1+'1';

end if;

end process;

process (rwsw,clkq,databf0,databf1,databf2,databf3,MDT0,MDT1,MDT2,MDT3,an1)

begin

if rwsw='0' then

OE<='1';

GW<='0';

MDT0<=databf0;

MDT1<=databf1;

MDT2<=databf2;

MDT3<=databf3;

elsif rwsw='1' then

GW<='1';

OE<='0';

MDT0<="ZZZZZZZZ";

MDT1<="ZZZZZZZZ";

MDT2<="ZZZZZZZZ";

MDT3<="ZZZZZZZZ";

databfin0<=MDT0;

databfin1<=MDT1;

databfin2<=MDT2;

databfin3<=MDT3;

if clkq="000" then ZBKDT<=an1(7 downto 0);

elsif clkq="001" then ZBKDT<=an1(15 downto 8);

elsif clkq="010" then ZBKDT<="111111"&an1(17 downto 16);

elsif clkq="011" then ZBKDT<=databfin0;

elsif clkq="100" then ZBKDT<=databfin1;

elsif clkq="101" then ZBKDT<=databfin2;

elsif clkq="110" then ZBKDT<=databfin3;

end if;

end if;

end process;

end Behavioral;

|