僩儔儞僕僗僞偱俉侽俉侽傪偮偔偭偰偟傑偍偆偲偄偆傑偝偵傃偭偔傝嬄揤丄嫸婥偺僾儘僕僃僋僩偱偡両

仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚

尒帠偵偱偒傑偟偨傜丄傕偪傠傫俿俲亅俉侽儌僯僞傪忔偣偰丄偦傟偐傜俛俙俽俬俠丄俠俹乛俵傪憱傜偣傑偟傚偆両

仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚

乵戞侾俈俆夞乶

仠儅僔儞僋儘僢僋乮俿僋儘僢僋乯夞楬乮俀乯

崱夞偺夞楬傕俹俬俠亅俠俹俴俢儘僕傾僫偱摦嶌妋擣傪偟偰傒傞偙偲偵偟傑偟偨丅

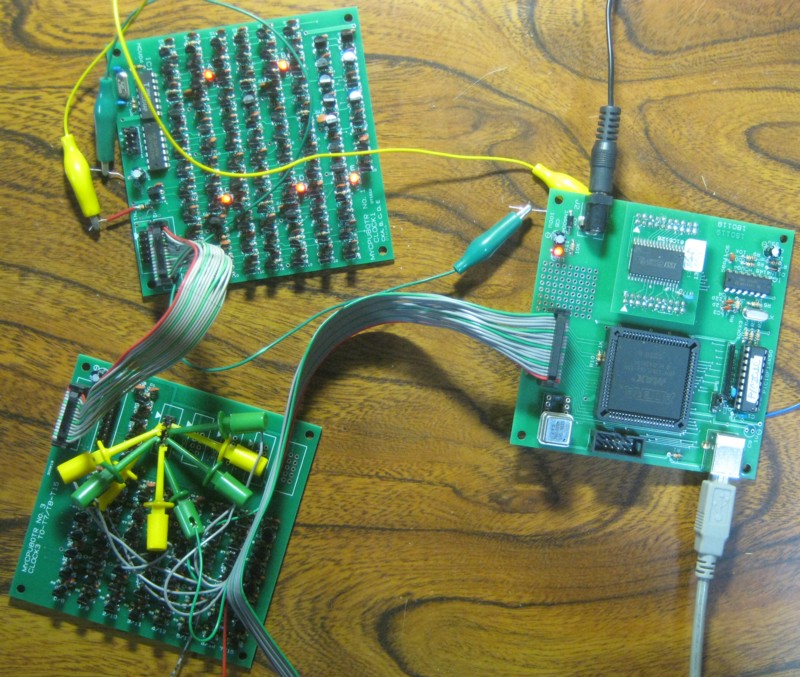

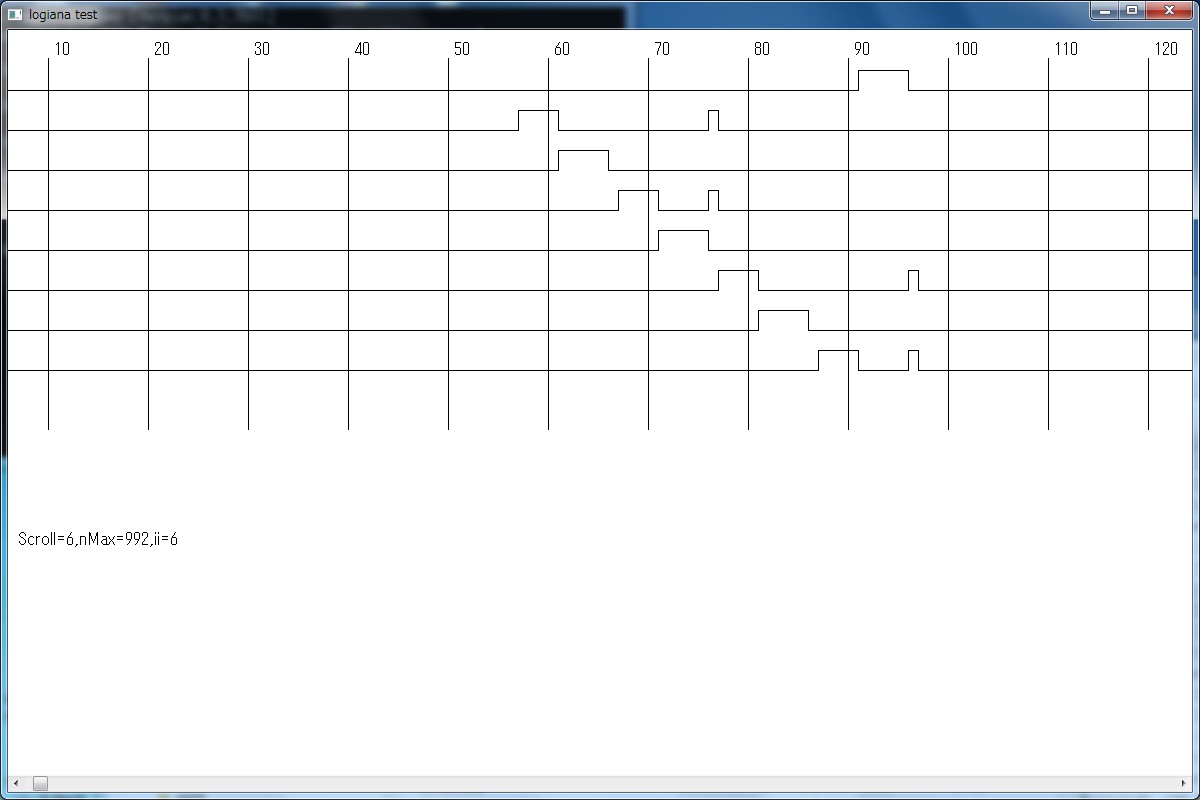

壓偼偦偺應掕傪峴側偭偰偄傞偲偒偺幨恀偱偡丅

嵍忋偑俠俹倀僋儘僢僋婎斅偱偡丅

偦偺壓偑崱夞惢嶌偟偨俿侽乕俿俈乮俿俉亅俿侾俆乯夞楬婎斅偱偡丅

塃懁偼俹俬俠亅俠俹俴俢儘僕傾僫婎斅偱偡丅

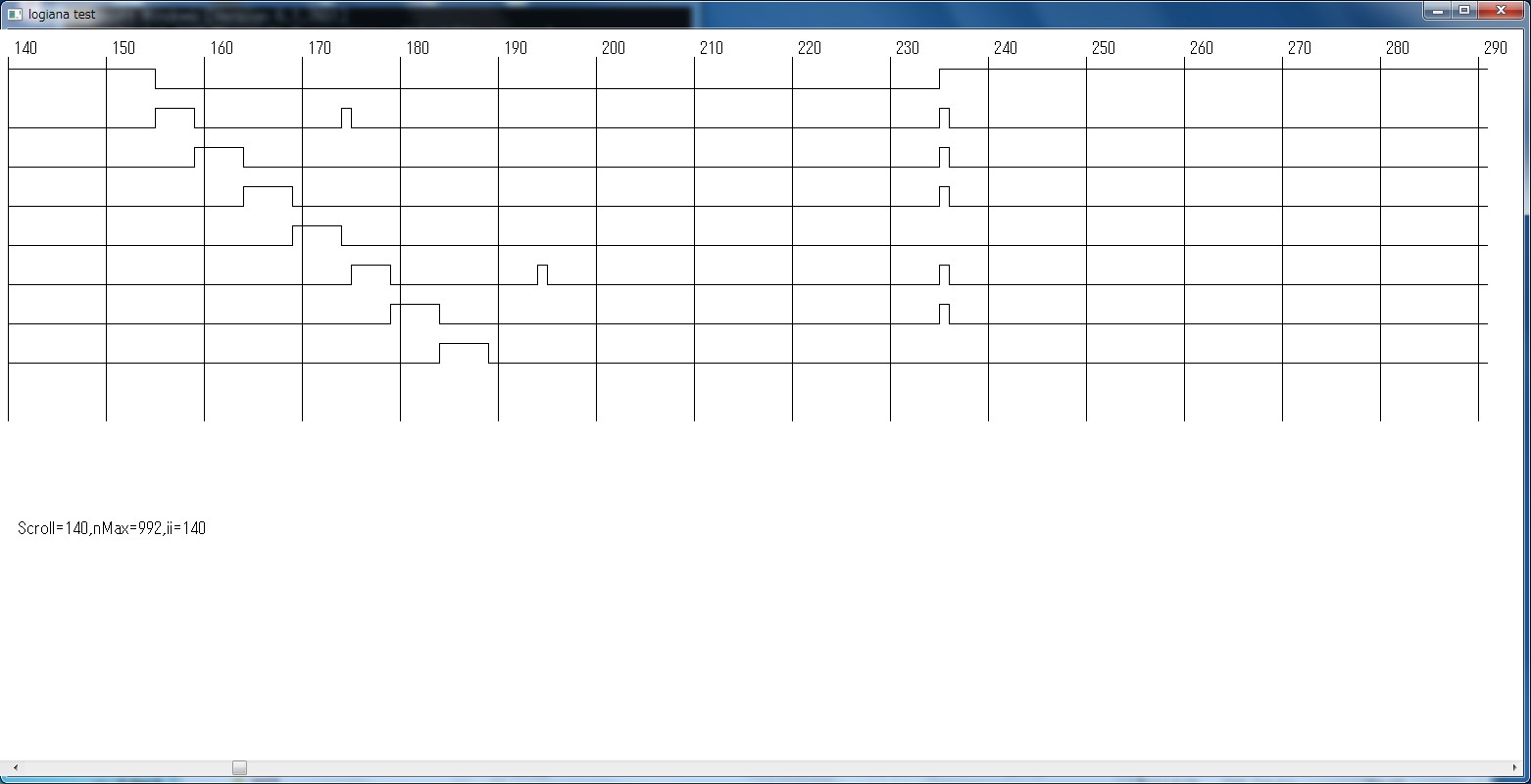

應掕偟偨攇宍偱偡丅

偙偺昞帵憢偼僗僋儘乕儖僶乕偑偁傞偙偲偺傎偐丄儅僂僗傪昞帵憢偺塃抂偵帩偭偰偄偭偰偦偙偱僪儔僢僌偡傞偙偲偱丄昞帵憢傪嵍塃偵峀偘傞偙偲偑偱偒傑偡丅

僾儘僌儔儉傪帺暘偱嶌偭偰偍偄偰丄旛傢偭偰偄傞婡擻偵偮偄偰偼偡偭偐傝朰傟偰偟傑偭偰偄傑偟偨丅

堦斣忋偺攇宍偼僋儘僢僋俤乮侾俀俆俲俫倸乯偱偡丅

偦偺壓偼忋偐傜弴偵俿侽乣俿俇偱偡丅

俿侽乣俿侾俆偼僋儘僢僋俤偑俴偺婜娫拞乮係兪倱乯偵弌椡偝傟傑偡丅

奺弌椡怣崋偺暆偼僋儘僢僋俙乮俀俵俫倸丄侽丏俆兪倱乯偺敿暆乮侽丏俀俆兪倱乯偱偡丅

恾偺廲慄偺娫妘偼侽丏俆兪倱偱偡偐傜寁嶼捠傝偺攇宍偵側偭偰偄傑偡丅

俿僋儘僢僋夞楬婎斅偼婎斅忋偵俿侽乣俿俈偺楢懕偡傞俉弌椡夞楬偟偐嵹偣偰偄傑偣傫丅

僕儍儞僷僺儞偺愝掕偵傛偭偰俿侽乣俿俈偺弌椡偲俿俉乣俿侾俆偺弌椡傪慖傇偙偲偑偱偒傑偡丅

摨偠俀枃偺婎斅傪嶌偭偰偦傟傪偮側偖偙偲偱俿侽乣俿侾俆傑偱偺弌椡偑摼傜傟傞傛偆偵峫偊偰偁傝傑偡丅

偲偙傠偱丄崱偺偲偙傠俹俬俠亅俠俹俴俢儘僕傾僫偼摨帪偵俉價僢僩偟偐應掕偱偒傑偣傫偐傜忋偺恾偺傛偆偵偦偺偆偪偺侾價僢僩傪僋儘僢僋俤偵妱傝摉偰傞偲丄摨帪偵偼俿侽乣俿俇偺俈弌椡偟偐娤應偡傞偙偲偑偱偒傑偣傫丅

偦偙偱俿俈偺攇宍傪尒傞偨傔偵僋儘僢僋俤傪奜偟偰丄戙傢傝偵俿俈傪偮側偄偱傒傑偟偨丅

尒偨栚偱偼俿俈偑堦斣忋偵側偭偰偄傑偡偑丄弌椡偝傟傞弴偱尒傞偲俿侽乣俿俈偺弴偵暲傫偱偄傑偡丅

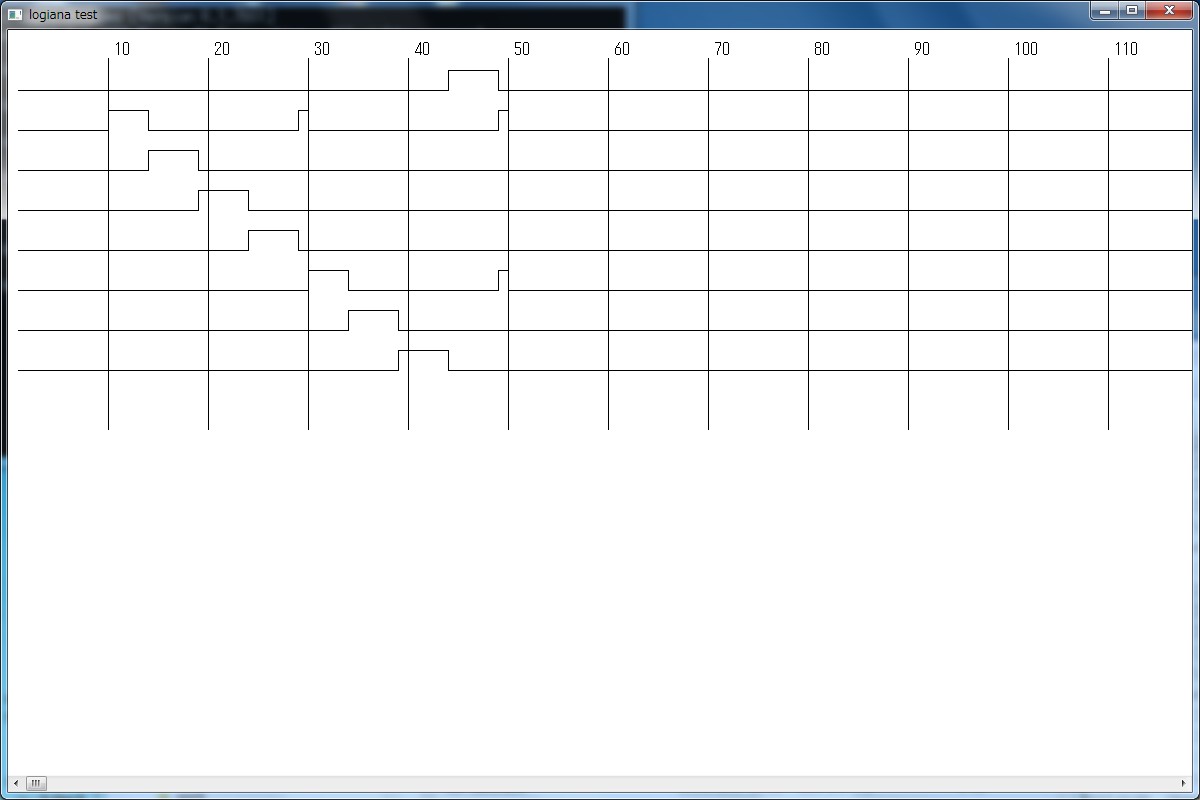

僕儍儞僷僺儞偺愝掕傪曄偊偰丄俿俉乣俿侾係傪娤應偟偰傒傑偟偨丅

僋儘僢僋俤偑俴偺婜娫偺偪傚偆偳敿暘偑夁偓偨偲偙傠偵俿俉偑偁傝傑偡丅

偝偒傎偳偺俿俈偲摨條偵丄俿侾俆偑巆偭偰偟傑偄傑偡偐傜丄俿俈偺偲偒偲摨偠傛偆偵偟偰僋儘僢僋俤偺戙傢傝偵俿侾俆傪偮側偄偱娤應偟傑偟偨丅

僋儘僢僋俤傪奜偟偰偄傞偨傔丄俿侽乣俿俈偺娤應夋柺偲摨偠偵尒偊傑偡偑丄偙偪傜偼俿俉乣俿侾俆偺娤應夋柺偱偡丅

偲偙傠偱忋偺娤應夋柺偺偲偙傠偳偙傠偵僑儈偺傛偆側僷儖僗偑尒偊傞偙偲偵偍婥晅偒偺偙偲偲巚偄傑偡丅

偙傟偼摉弶偐傜憐掕偟偰偄偨偙偲側偺偱偡偑丅

俿僋儘僢僋偼俙乣俤偺僋儘僢僋偺俙俶俢傪庢偭偰嶌惉偟傑偡丅

偲偙傠偑俙乣俤偺奺僋儘僢僋偼儘僕僢僋夞楬傪壗抜傕捠傝側偑傜弌椡偝傟傞偨傔丄偳偆偟偰傕弌椡偵抶傟偑惗偠傑偡丅

偦偺抶傟偑惗偠偰偄傞怣崋偺俙俶俢傪庢傞偨傔偵丄抶傟偑柍偄応崌偵偼敪惗偟側偄偼偢偺僸僎偑敪惗偟偰偟傑偄傑偡丅

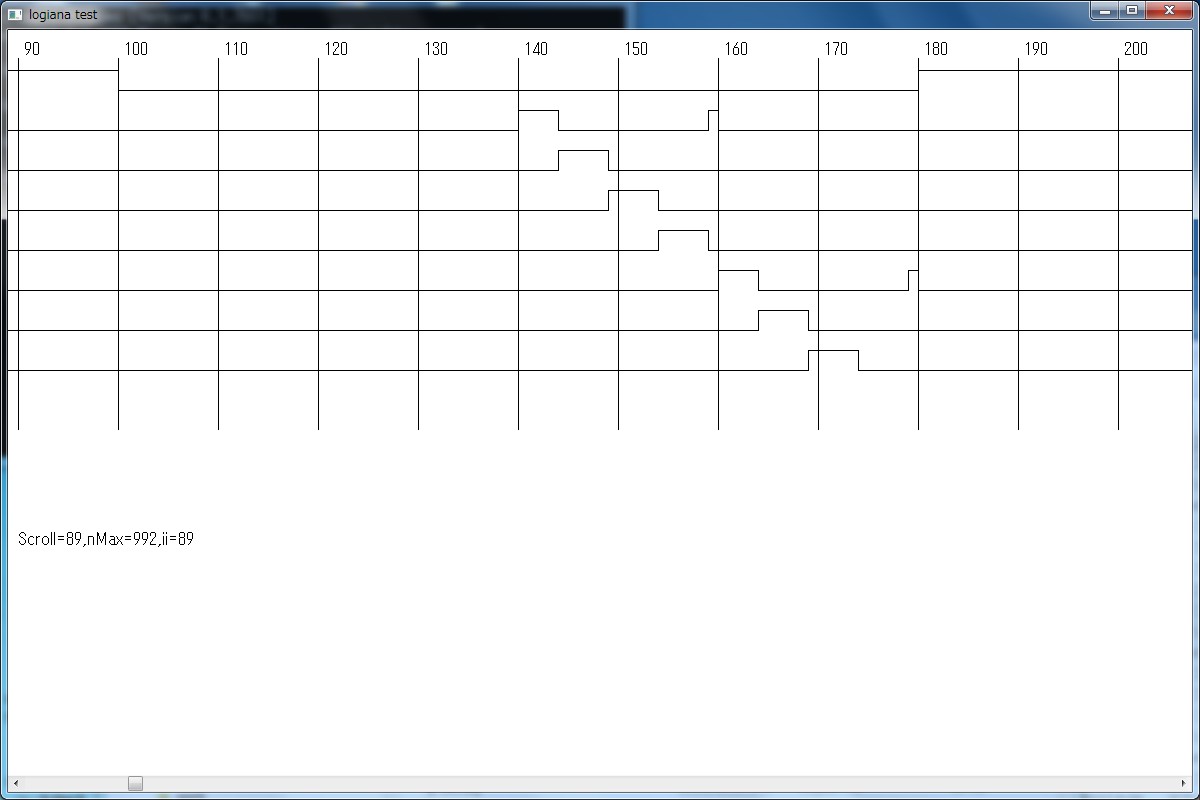

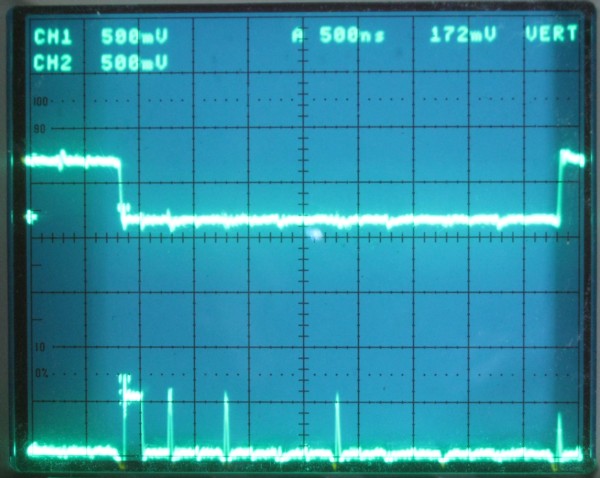

壓偼僋儘僢僋俤偲俿侽偺攇宍傪僆僔儘偱娤應偟偨幨恀偱偡丅

杮棃偺僷儖僗偺傎偐偵偐側傝偼偭偒傝偟偨僸僎偑尒偊傑偡丅

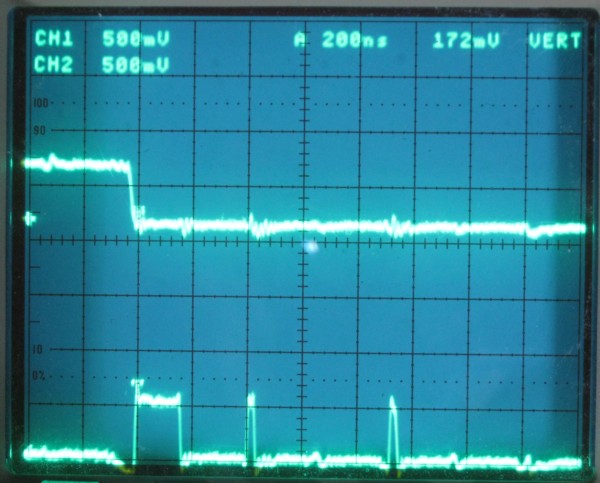

帪娫幉傪奼戝偟偰傒傑偟偨丅

偙偺掱搙偺帪娫幉偱偼僷儖僗暆偼偼偭偒傝撉傔傑偣傫偑丄僸僎偺暆偼係侽値倱偖傜偄偼偁傝偦偆偱偡丅

媡偵俿侽偼寁嶼忋偼俀俆侽値倱偺偼偢側偺偱偡偑丄俀侽侽値倱傪愗偭偰偄傞傛偆偵尒偊傑偡丅

侾俇侽乣侾俈侽値倱偖傜偄偟偐側偄傛偆偵尒偊傑偡丅

俿侽偺暆偑嫹偄偙偲傕栤戣偱偡偑丄僸僎傕婥偵側傝傑偡丅

俵倄俠俹倀俉侽偱傕偙傟傛傝偼嫹偄傕偺偺摨偠傛偆偵僸僎偑偁傝傑偟偨丅

俵倄俠俹倀俉侽偱偼偦偺僸僎偼僐儞僨儞僒偱偮傇偟偨偺偱偡偑丄崱夞偺傛偆偵暆偑峀偄僸僎傪僐儞僨儞僒偱偮傇偡傛偆偵偡傞偲丄偣偭偐偔偺僔儍乕僾側棫偪忋偑傝丄棫偪壓偑傝偺俿僋儘僢僋弌椡偦偺傕偺傑偱側傑偭偰偟傑偄傑偡丅

偙偙偼擸傑偟偄偲偙傠偱偡丅

嵟廔揑偵偼慡懱偱偼悢愮屄偺僩儔儞僕僗僞夞楬偵側傞梊掕側偺偱丄慡懱偺夞楬傪偮側偘偽偦偺晧壸梕検偺偨傔偵偳偆偣彫偝偄僷儖僗側偳偼偮傇傟偰偟傑偆偲傕峫偊傜傟傑偡丅

偟偐偟丅

偪傚偭偲僸僎偑戝偒偄偺偱丄傂傚偭偲偡傞偲丄俙乣俤偺弌椡偺懌暲傒傪懙偊偰弌椡偝偣傞傛偆偵岺晇偡傞昁梫偑弌偰偔傞偐傕偟傟傑偣傫丅

摨婜幃僇僂儞僞偺峫偊曽偱偡偑丄嫵壢彂揑側峫偊曽傪偡傞偲弌椡怣崋偑嵶偭偰偟傑偄偦偆偱偡丅

偄偢傟偦偆側傜側偄傛偆側岺晇傕峫偊偰傒傞偮傕傝偱偡偑丄偦偙偵庱傪撍偭崬傓偲愭偵恑傔側偔側偭偰偟傑偄傑偡丅

尰忬偺僸僎偑偁傞傑傑偱丄偟偽傜偔偼偙偺傑傑恑傓偙偲偵偟傑偡丅

僩儔儞僕僗僞偱俠俹倀傪偮偔傠偆両乵戞侾俈俆夞乶

俀侽侾俋丏侾侾丏俇倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞