僩儔儞僕僗僞偱俉侽俉侽傪偮偔偭偰偟傑偍偆偲偄偆傑偝偵傃偭偔傝嬄揤丄嫸婥偺僾儘僕僃僋僩偱偡両

仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚

尒帠偵偱偒傑偟偨傜丄傕偪傠傫俿俲亅俉侽儌僯僞傪忔偣偰丄偦傟偐傜俛俙俽俬俠丄俠俹乛俵傪憱傜偣傑偟傚偆両

仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚

乵戞侾俈俈夞乶

仠儅僔儞僋儘僢僋乮俵僋儘僢僋乛倂僋儘僢僋乯夞楬

僩儔儞僕僗僞俠俹倀偺柦椷偼婎杮揑側儅僔儞僋儘僢僋乮俿僋儘僢僋乯偵偟偨偑偭偰幚峴偝傟傑偡偑丄柦椷偵傛偭偰偼俿僋儘僢僋偺攞暆偺俵僋儘僢僋丄俿僋儘僢僋偺係攞暆偺倂僋儘僢僋傕昁梫側偲偙傠偑偁傝傑偡丅

偦偙偱俵僋儘僢僋偲俿僋儘僢僋偺夞楬婎斅傪嶌惉偟傑偟偨丅

壓偼俵僋儘僢僋偺夞楬偱偡丅

嶌恾偺搒崌偱俵僋儘僢僋偺堦晹偲倂僋儘僢僋偺夞楬恾偼暿偵嶌惉偟傑偟偨丅

偙偪傜偑俵僋儘僢僋偺堦晹偲倂僋儘僢僋偺夞楬恾偱偡丅

夞楬偺峫偊曽偼俿僋儘僢僋偺偲偒偲摨偠偱偡丅

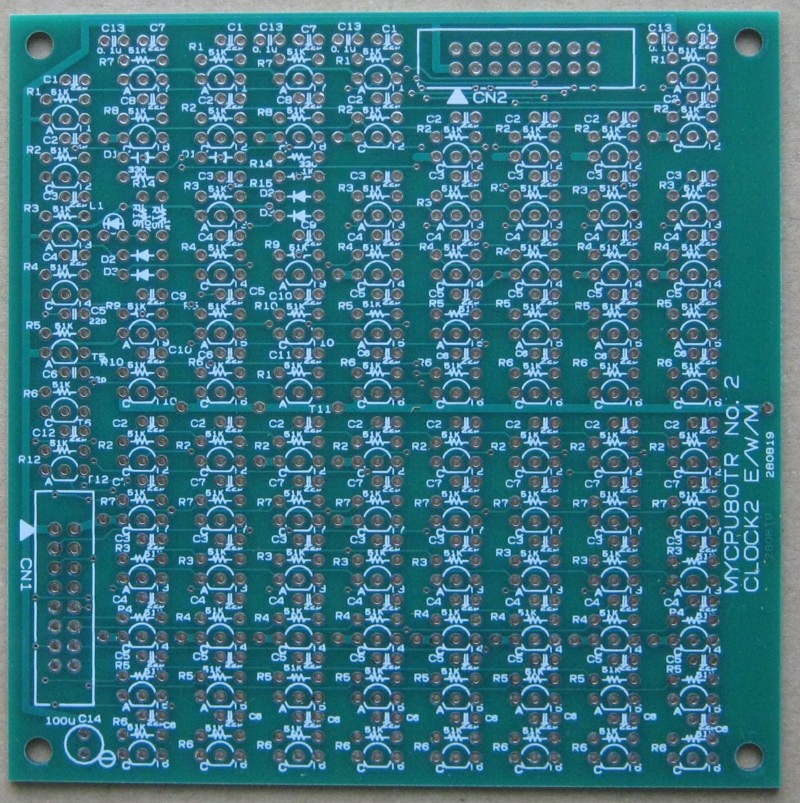

俵僋儘僢僋乛倂僋儘僢僋偺帋嶌婎斅偱偡丅

婎斅偺僒僀僘偼侾侽侽倣倣亊侾侽侽倣倣偱偡丅

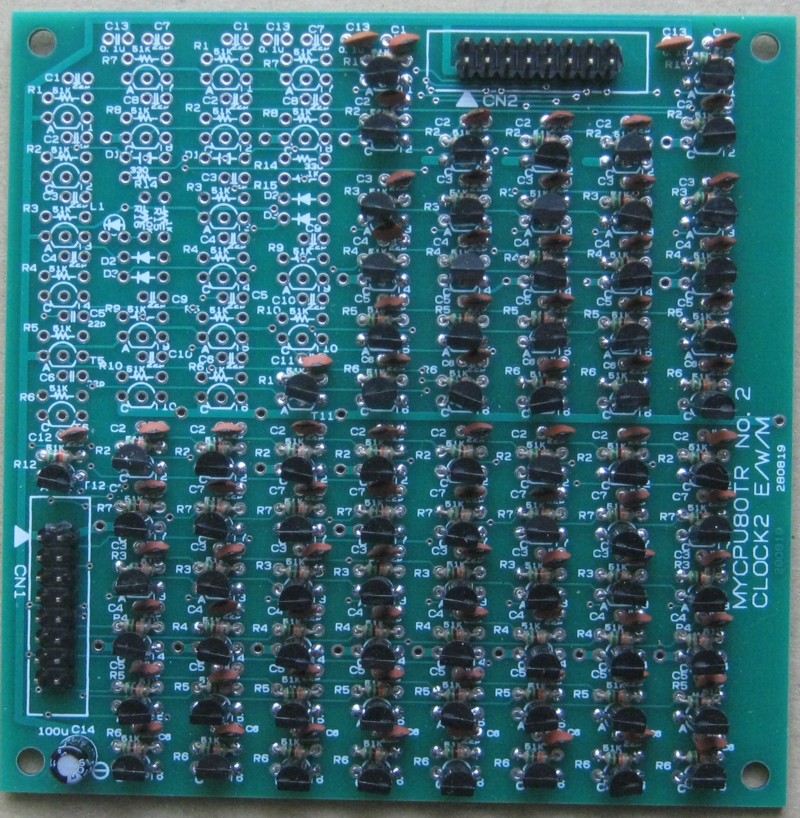

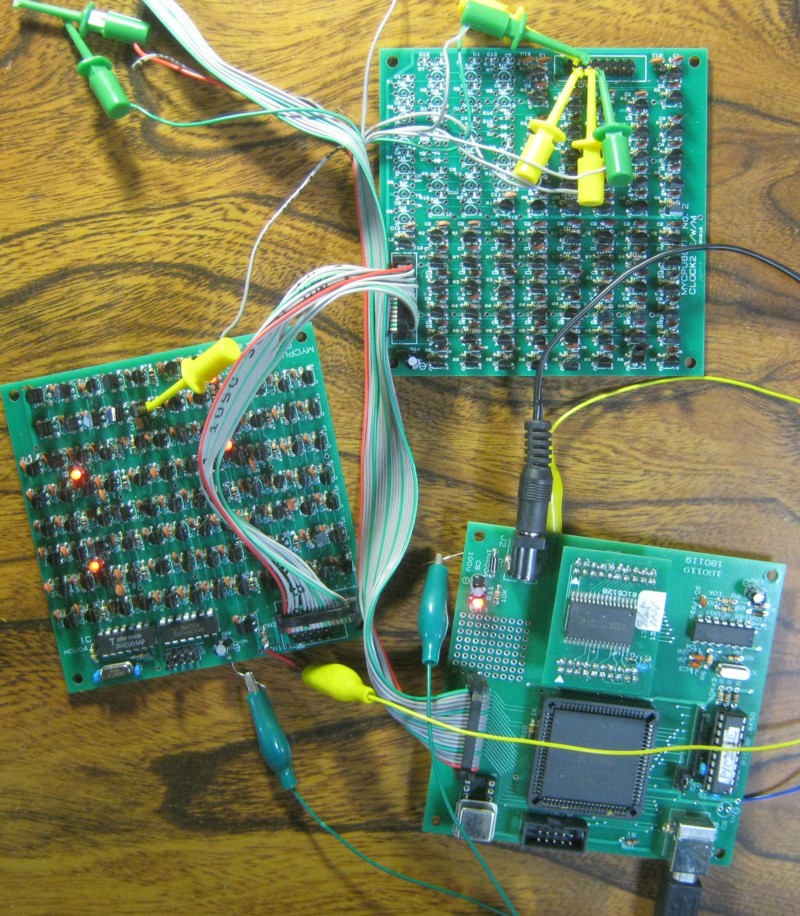

僷乕僣傪幚憰偟傑偟偨丅

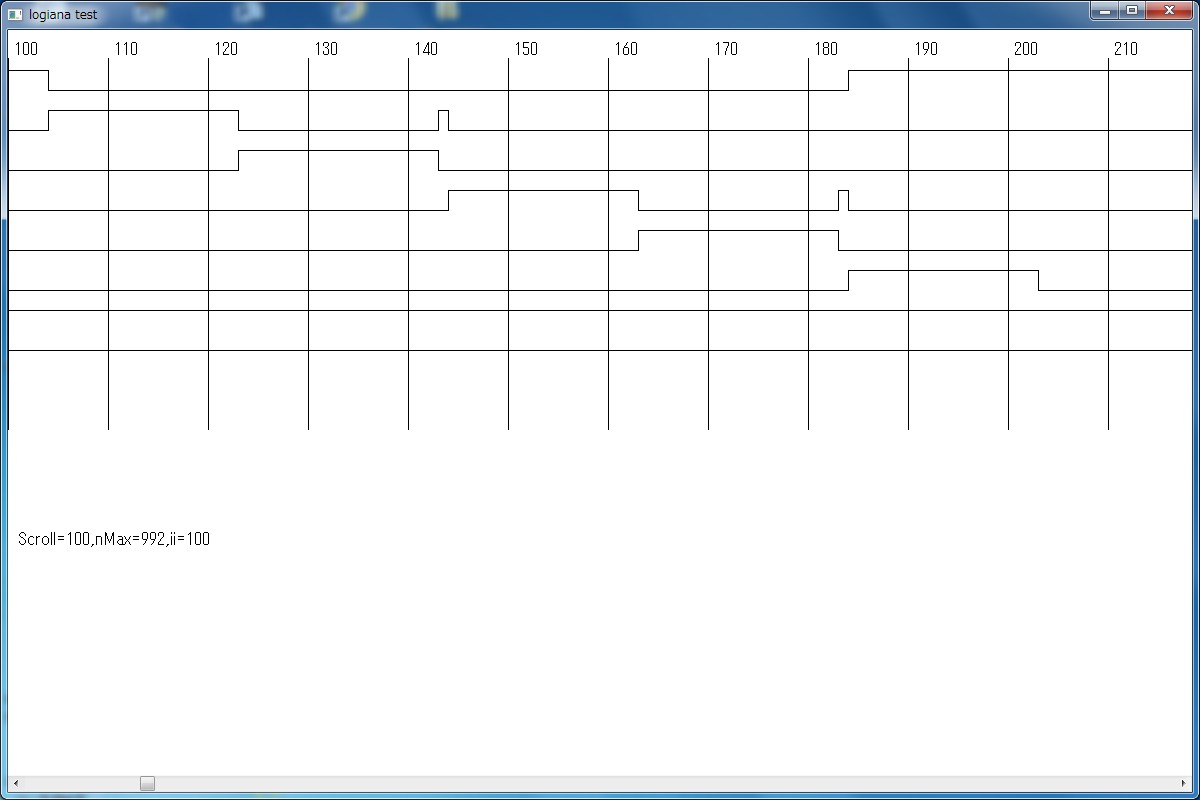

摉弶偼僗儁乕僗偺娭學偱偙偺婎斅偵俤僋儘僢僋夞楬傕嵹偣偰偄偨偺偱偡偑丄偦偺屻偺夞楬曄峏偵傛偭偰丄俤僋儘僢僋偼傎偐偺俙丄俛丄俠丄俢偺奺僋儘僢僋偲摨偠婎斅偵搵嵹偡傞偙偲偵側傝傑偟偨丅

忋偺幨恀偺嵍忋偺枹幚憰偺偲偙傠偼丄偙偺婎斅偵偼幚憰偟側偄偙偲偵側偭偨俤僋儘僢僋夞楬偱偡丅

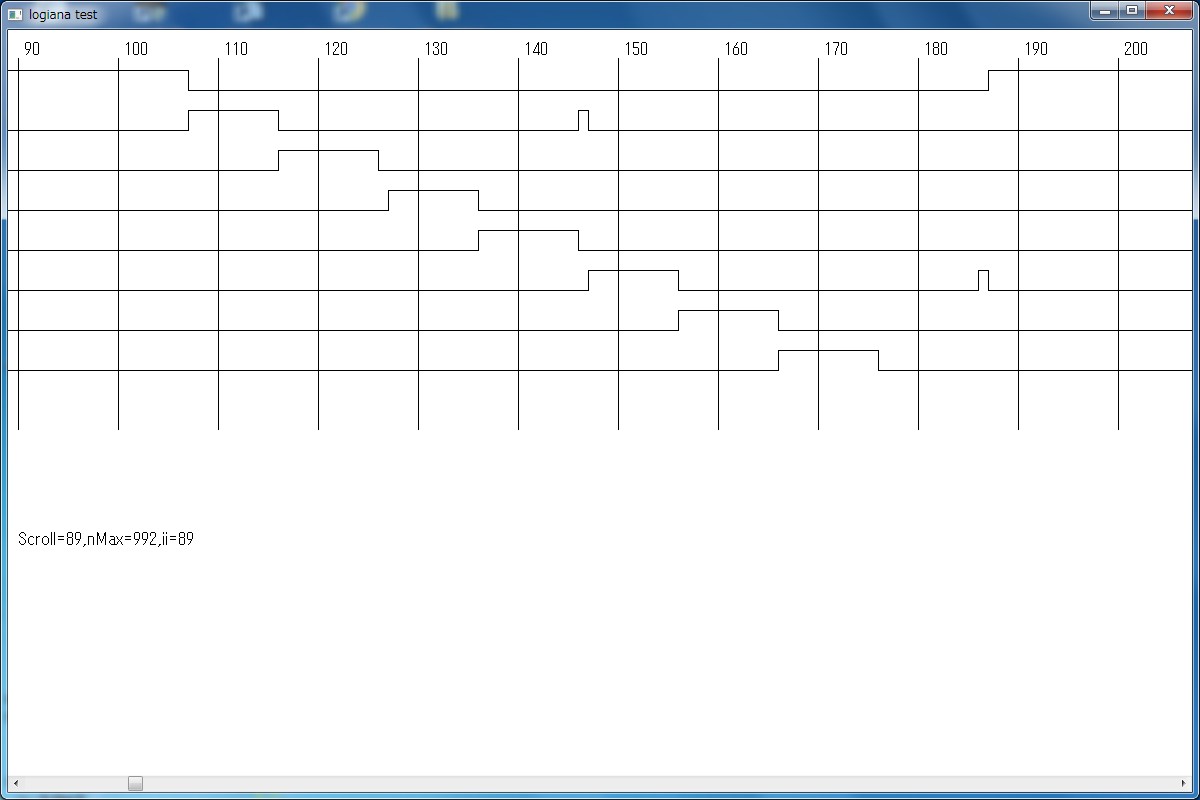

俿僋儘僢僋夞楬偲摨偠傛偆偵俹俬俠亅俠俹俴俢儘僕傾僫偱俵僋儘僢僋乛倂僋儘僢僋婎斅偺弌椡僷儖僗傪妋擣偟偰傒傑偟偨丅

壓偼應掕拞偺幨恀偱偡丅

嵍壓偼僋儘僢僋夞楬婎斅乮僋儘僢僋俙乣俤弌椡乯偱偡丅

塃忋偼俵侽亅俵俈乛倂侽亅倂係夞楬婎斅偱偡丅

偦偺壓懁偼俹俬俠亅俠俹俴俢儘僕傾僫婎斅偱偡丅

儘僕傾僫攇宍偱偡丅

堦斣忋偑僋儘僢僋俤偱偡丅

偦偺壓偐傜弴偵俵侽乣俵俇偱偡丅

俵侽乣俵俈偼僋儘僢僋俤偑俴偺婜娫偵弌椡偝傟傑偡丅

帋嶌拞偺儘僕傾僫側偺偱俉僠儍儞僱儖乮俉價僢僩乯偟偐應掕偑偱偒傑偣傫丅

偦偙偱堦斣忋偺俤僋儘僢僋傪奜偟偰丄戙傢傝偵俵俈傪偮側偓傑偟偨丅

俵俈偑昞帵偝傟偰偄傞埵抲偼堦斣忋偱偡偑丄悈暯曽岦乮帪娫幉乯偱尒傞偲堦斣壓偺俵俇偺師偵弌椡偝傟偰偄傑偡丅

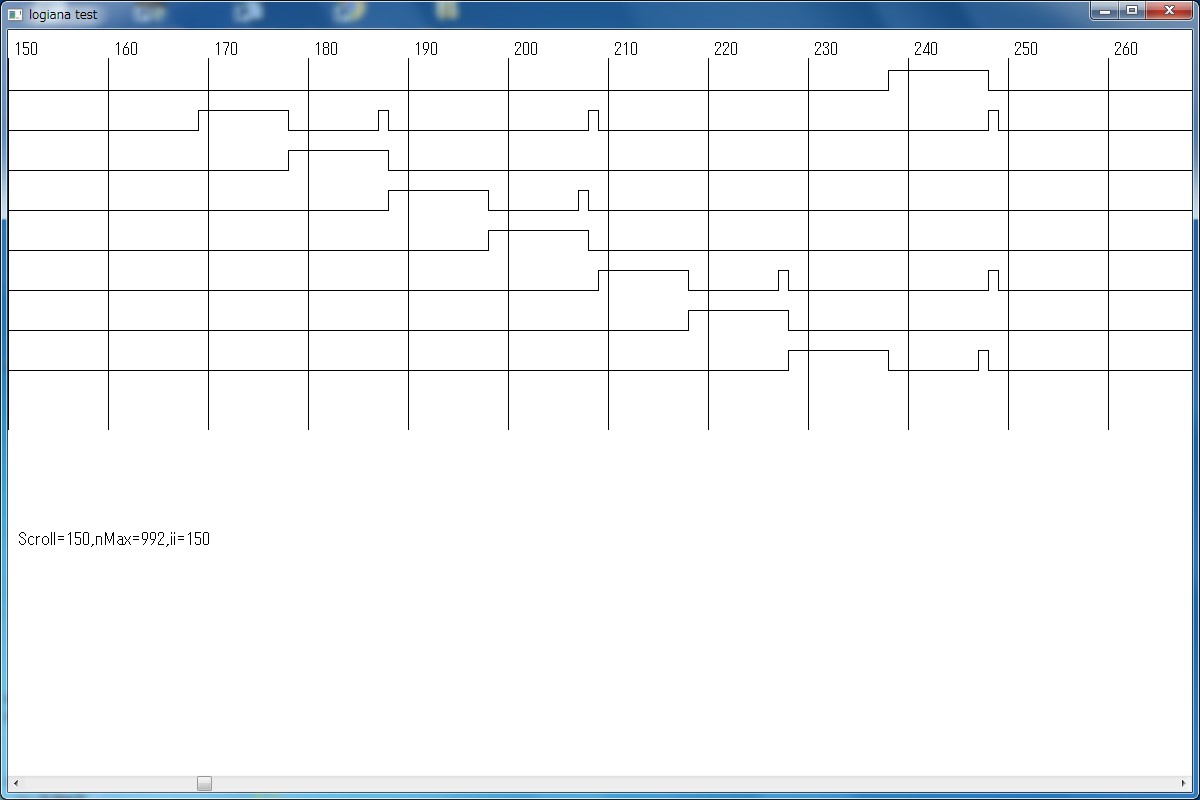

師偼倂僋儘僢僋偱偡丅

堦斣忋偼僋儘僢僋俤偱偡丅

偦偺壓偐傜弴偵倂侽乣倂係偱偡丅

倂侽乣倂俁偼僋儘僢僋俤偑俴偺婜娫偵弌椡偝傟傑偡丅

倂係偼僋儘僢僋俤偑俫偺婜娫偵弌椡偝傟傑偡丅

僩儔儞僕僗僞偱俠俹倀傪偮偔傠偆両乵戞侾俈俈夞乶

俀侽侾俋丏侾侾丏侾侾倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞