トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK−80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第202回]

●OPコードフェッチ回路(3)プリント基板が出来てきました

当テーマで書くのはおよそ2週間ぶりです。

当テーマの前回([第201回])ではOPコードWRITE回路のトランジスタのエミッタにダイオードを追加する変更を行ないました。

作業を進めていく過程で気がついたのですが、OPコードフェッチ回路はそこにREAD回路を追加すればそのままレジスタ回路にもなります。

レジスタ回路はもう半年以上も前に何回かの試作のあとで一旦は回路として完成したと思うところまでいっていたのですが、その後にその回路を応用して発展させたINC/DECレジスタ回路で異常が発生したために、もう一度考え直すことにしてそこで止まっていました。

今回のOPコードフェッチ回路の試作基板での動作テストがうまくいけば、一時棚上げ状態になっていたレジスタ回路も先に進めそうです。

OPコードフェッチ回路の実体は8ビットのデータラッチ回路です。

トランジスタのデータラッチ回路については随分時間をかけて試行錯誤を重ねてきましたが、ここへきてどうやらやっと終着点に到達できたように思います。

なかなかうまくクリアできなかったのは前回書きましたように、トランジスタが逆接続の状態になってしまうことに気が付かなかったというただ一点にあったように思います。

その解決にはトランジスタのエミッタにダイオードを追加することが必要でした。

そのように対策した最終的な回路図は前回のところでお見せしましたがかなり時間が経ってしまいましたので下に再掲します。

図の上側の回路(トランジスタ6石で構成)がデータラッチ回路です。

同じ回路が8ビット分(8回路)あります。

図の上側の回路はそのうちの1ビットを示したものです。

T1とT2のエミッタに図の向きにダイオードを追加することで、トランジスタの逆接続状態を回避できます。

上の図は前回の回路図をそのまま使いましたのでR14は10KΩになっていますが、前回の検討の結果ここは4.7KΩに変更することにしました。

図の下側の回路はデータ書き込み時のみ上側の回路の左側部分のトランジスタにVccとGNDを供給するための回路です。

この回路は1回路だけで、8ビット分のデータWRITE回路にWRV(+5V)とWRG(GND)を供給します。

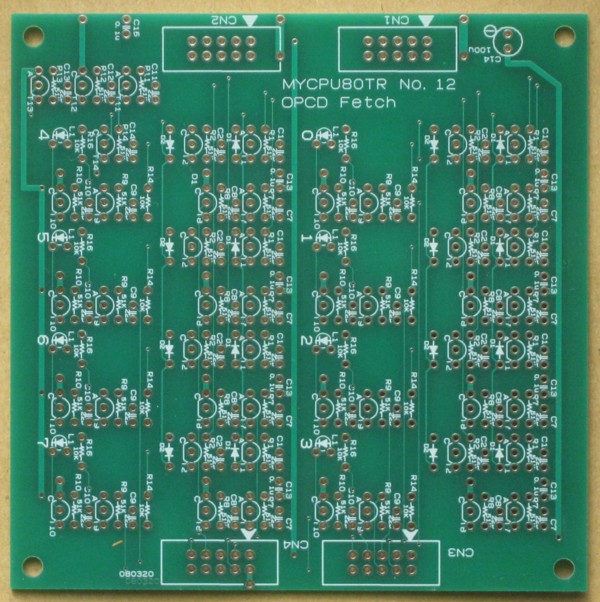

ダイオードを追加して作り直した試作基板です。

R14の検討前に発注してしまったのでシルク印刷ではR14はまだ10KΩのままです。

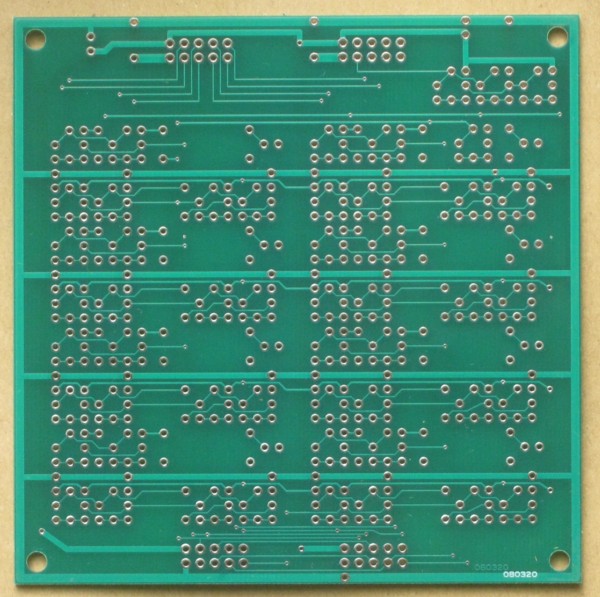

基板裏の写真です。

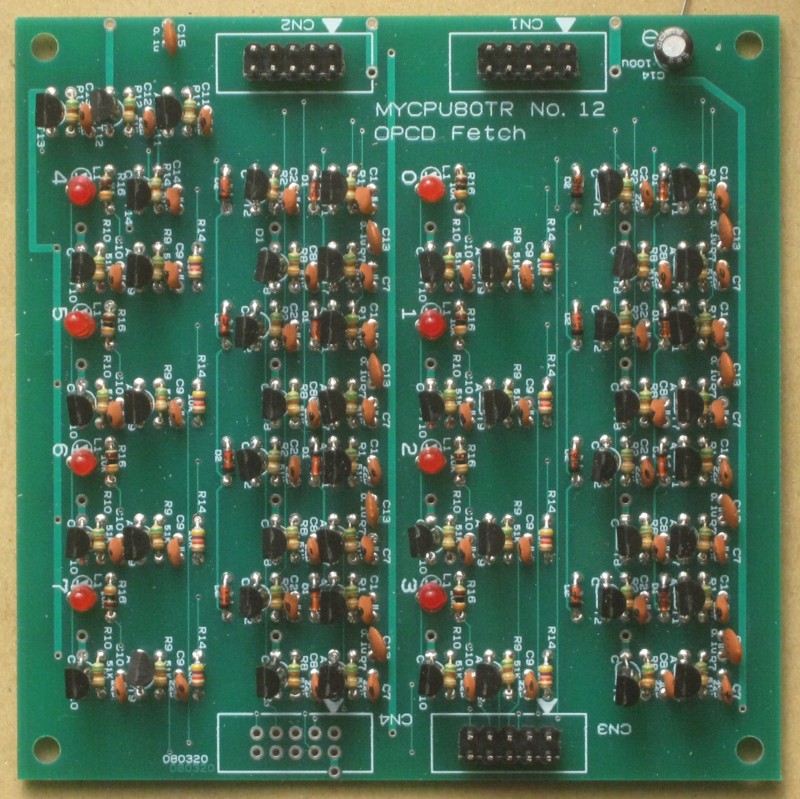

部品を実装しました。

R14には4.7KΩを実装しました。

写真で見て左上にあるトランジスタ3石はWRV、WRG出力回路です。

この部分は回路図ではトランジスタは4石ですが、T14は最終段なので不要と判断したため試作基板ではT14を外して3石としました。

OPコードフェッチ回路はCPUクロックのはじめのところ(T1)で8ビットの内部バスをOPコードとしてラッチします。

1ビットのラッチ回路はトランジスタ6石で構成しています。

上の基板は試行錯誤を繰り返した末に回路図の回路に落ち着いたため、当初の回路のうち余分になった部分を除外するなどして作成しました。

そのため写真のようにところどころが歯抜け状態になっています。

トランジスタでCPUをつくろう![第202回]

2020.3.24upload

前へ

次へ

ホームページトップへ戻る