トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK−80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第418回]

●バイナリカウンタ回路の改良(8)

今回はR14について書くつもりだったのですがまたまた予定変更です。

前回をUPしたあとで気が付いたことがあります。

MYCPU80TRはできればCPUクロックを1MHzにしたいと思っています。

でもいろいろテストしながら考えていると1MHzは無理なような気がします。

トランジスタで高速マシンを作ろうなんてことは毛頭考えていません。

最終目的は8080をトランジスタでつくることなのですが、実用性まで考えているわけではありません。

要は動きさえすれば遅くてもいいのです。

CPUクロックさえ落とせばいろいろ出てきている問題もおのずから解決するのではないかと思います。

ということなのですけれど。

今はテストですからいけるところまで1MHzでいきたいと思っています。

それで気が付いたことなのですが。

Q_出力の遅延時間を確認するためにCLOCKを1MHzにしてテストをしました。

しかしよくよく考えてみると確かにカウンタ回路に入力するクロックはテストとしては1MHzですがQ_出力がH、Lの変化をするのは1μsごとなので、するとテストするために入力するクロックは倍の500KHz(半波が1μs)になります。

すると前回テストのためにインバータの入力の前の遅延回路には1MHzのクロックを入れるのではなくて、本当は500KHzのクロックを入れるべきです。

ということに気が付きました。

クロックを下げれば前回のゆがんだ出力波形ももうすこしきれいになるかもしれません。

もうひとつ考えたことがあります。

前回の遅延回路はR=10KΩ、C=22pFで行いました。

実際のカウンタ回路でもその数値を使うつもりだったのですが、よくよく考えてみると22pFというのは余りに小さい値です。

トランジスタのベースに入れているスピードアップコンデンサは22pFでも十分効くのでそれはそれでよいのですが遅延回路のコンデンサとしてはちょっと小さ過ぎるように思えてきました。

RとCの値が遅延時間に直接関係してきますからコンデンサの値が小さいと浮遊容量などの影響が無視できなくなります。

そこでこれもまあ適当なのですがとりあえずはC=100pFにしてみることにしました。

Rのほうは5.1KΩにしました。

そのように考えて今回は前回のテストをクロック500KHz、R=5.1KΩ、C=100pFにしてもう一度行なってみました。

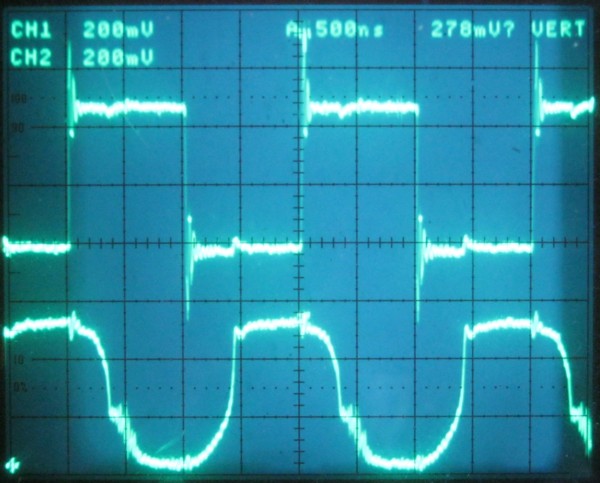

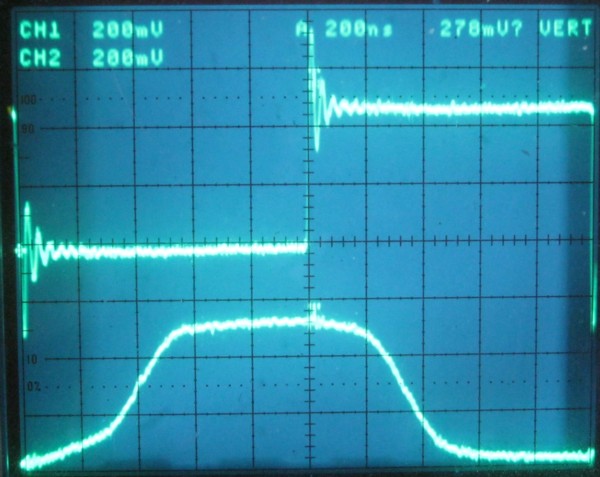

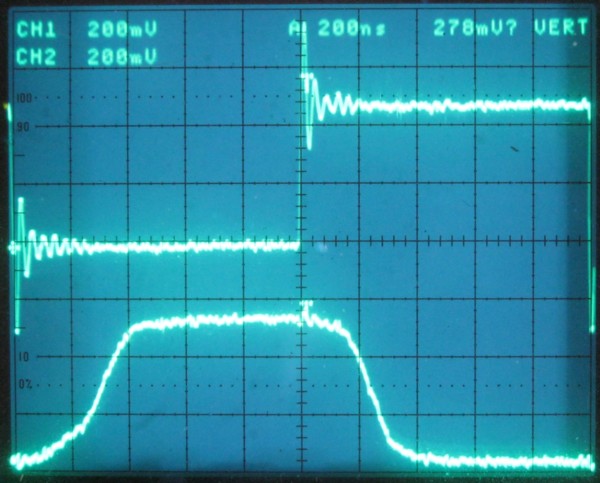

下はその波形の写真です。

上側(CH1)は遅延回路に入力した500KHzのクロックです。

カウンタ回路のQ_が1μsごとにON、OFFを繰り返すことを想定しています。

下側(CH2)は遅延回路を通した信号を入力したインバータ回路の出力です。

前回よりは少しはましな波形になりました。

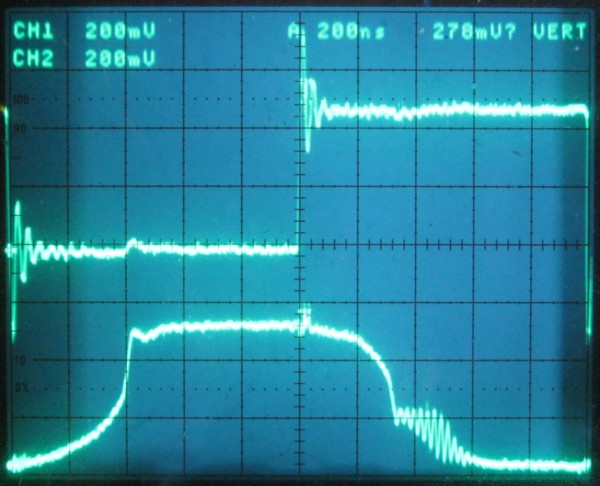

水平時間軸を拡大しました(下の写真)。

インバータの出力波形の立ち下りのところがなんだか少しゆがんでいてちょっと振動しているようです。

これって、ひょっとしたら。

今まで簡単なテストだからということでちょいと手抜きをしていました。

下が前回と今回行なったテスト回路です(前回はCLKIN=1MHz、R=10KΩ、C=22pF)。

トランジスタの両エミッタ間(つまりVccとGNDの間)にあるパスコン(0.1μFセラミックコンデンサ)は手抜きでつけていませんでした。

そのせいかと思ったので回路図の通りにつけてみました。

すると。

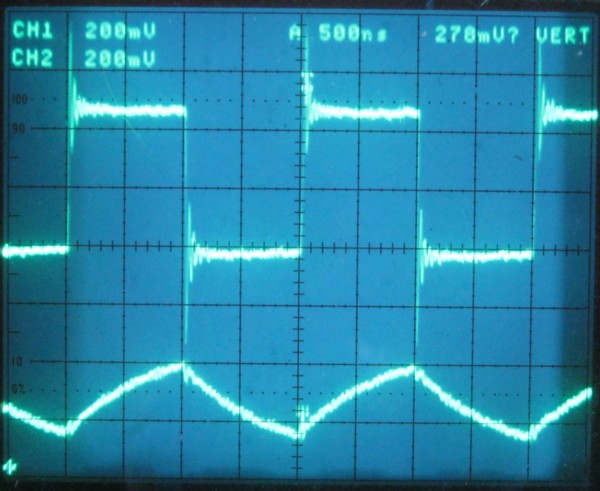

0.1μFの効果はてきめんでありました。

インバータの出力がきれいになりました。

水平時間軸を拡大しました(下の写真)。

立ち上がり、立ち下りはシャープではありませんが滑らかな波形になりました。

入力からの遅延は300〜400nsほどです。

このくらいの遅延時間が得られれば上々です。

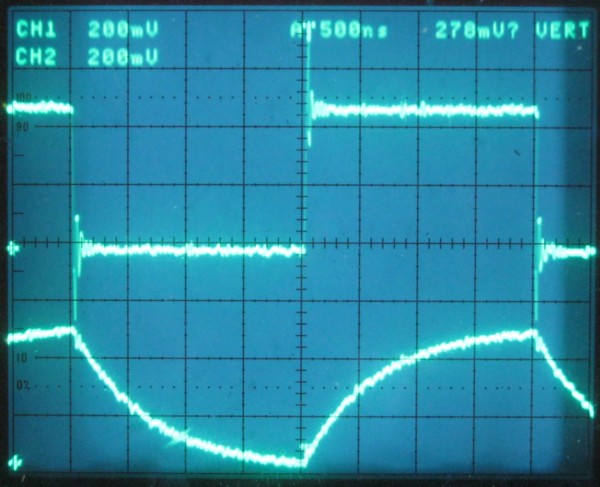

下は遅延回路の100pFコンデンサの+側の波形です。

上側(CH1)は遅延回路の入力側のクロック波形です。

下側(CH2)は遅延回路の出力側(100pFコンデンサの+側)の波形です。

2.5V近くを中心に1V〜3Vの三角波になっています。

フルスイングにはなっていません。

コンデンサが充放電するのに500KHzでは周期が短すぎるようです。

R=5KΩ、C=100pFのときにコンデンサが90%ぐらいまで充電、放電するには2μsほどかかります(下の写真)。

上側(CH1)は250Hzです。

半波は2μsです。

これなら充放電波形(CH2)はちょうど0Vから+5Vまでフルスイングしています。

しかしそれではCLOCK=1MHzでのカウンタ回路の条件(Q_の出力間隔1μs以内に遅延が終了する)には間に合いません。

さてどうするか。

入力電圧幅は狭くなるけれどそれでもなんとか動作しているし厳しいのは初段(入力クロック1MHz)だけでその上の段になれば入力は500KHz(Q_出力は250KHz、半波は2μs)になるので条件通りになります。

だから。

それでよいことにするか。

一旦はそのように思ったのですけれど。

それほど手間のかかることではありません。

それに5.1KΩは51KΩと色コードがほぼ同じです。

違うのは10のn乗を示す赤と橙のところのみ。

昔と違って抵抗のサイズも小さくなってカラーコードの読みにくいこと。

赤と橙など照明の下で虫眼鏡で見るかテスターで測らないと区別できません。

51KΩはおそらく千本単位で使うことになります。

これは避けたほうがよさそうです。

ということで。

結局R=4.7KΩ、C=56pFに変更して再々度テストをやり直しました。

なかなかにしんどいことです。

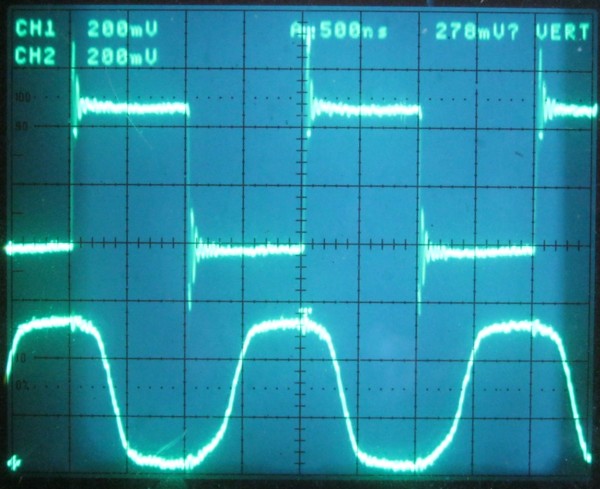

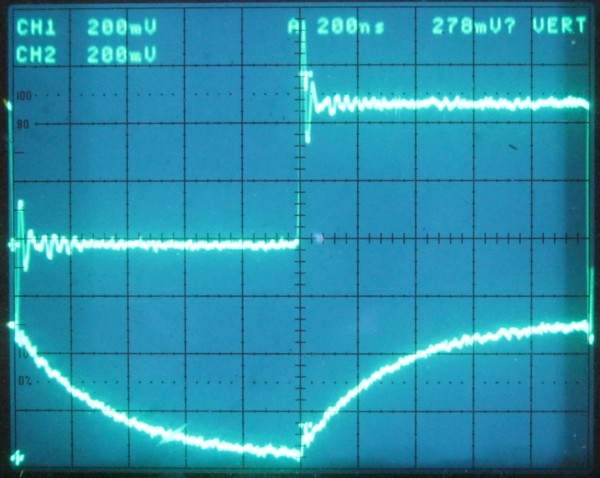

下はその波形です。

上側(CH1)は入力クロック(500KHz)です。

半波は1μsです。

下側(CH2)は遅延回路のコンデンサ(56pF)の+側の波形です。

+5Vから0Vまで放電、充電しています。

これなら文句なしです。

インバータの出力波形も確認してみました(下の写真)。

上側(CH1)は遅延回路に入力したクロック(500KHz)です。

下側(CH2)は遅延回路を通した信号を入力したインバータ回路の出力波形です。

入力クロックに対して300ns程度の遅延です。

そのくらいならまあまあよいのでは、と思います。

次回はR14とそのほかのことについて書くことにいたします。

トランジスタでCPUをつくろう![第418回]

2024.2.13upload

前へ

次へ

ホームページトップへ戻る