僩儔儞僕僗僞偱俠俹倀傪偮偔傠偆両

僩儔儞僕僗僞偱俉侽俉侽傪偮偔偭偰偟傑偍偆偲偄偆傑偝偵傃偭偔傝嬄揤丄嫸婥偺僾儘僕僃僋僩偱偡両

仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚

尒帠偵偱偒傑偟偨傜丄傕偪傠傫俿俲亅俉侽儌僯僞傪忔偣偰丄偦傟偐傜俛俙俽俬俠丄俠俹乛俵傪憱傜偣傑偟傚偆両

仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚仚

乵戞俆俋夞乶

仠倃俷俼夞楬乮俀乯

慜夞偼俠俹倀傪峔惉偡傞夞楬偼俶俙俶俢夞楬偱昞偡偙偲偑偱偒傞偼偢丄偲偄偆偙偲傪彂偒傑偟偨丅

偦偆偱偁傞側傜偽丄倃俷俼夞楬傕摉慠俶俙俶俢夞楬偱昞偡偙偲偑偱偒傞偼偢偱偡丅

慜夞偍尒偣偟偨倃俷俼偺榑棟墘嶼傪嵞宖偟傑偡丅

倃俷俼偺僔儞儃儖恾偱偡丅

壓偑倃俷俼偺榑棟墘嶼偱偡丅

| 俙 |

俛 |

俠 |

| 侽 |

侽 |

侽 |

| 侽 |

侾 |

侾 |

| 侾 |

侽 |

侾 |

| 侾 |

侾 |

侽 |

俙丄俛偑擖椡偱俠偑弌椡偱偡丅

俙丄俛偑偲傕偵侽傑偨偼侾側傜偽俠偼侽偱丄俙丄俛偑堎側傞抣偺偲偒俠偼侾偵側傝傑偡丅

偙傟傪俶俙俶俢僎乕僩偱嶌傞偲壓偺傛偆偵側傝傑偡丅

僀儞僶乕僞傕俶俙俶俢僎乕僩偱昞偡偙偲偑偱偒傑偡偑丄傢偞傢偞僀儞僶乕僞傪俶俙俶俢偱嶌傞偺偼柍懯偱偡偺偱丄偙偙偼慺捈偵僀儞僶乕僞傪巊偄傑偡丅

俶俙俶俢偑俁偮偲僀儞僶乕僞偑俀偮偱偡丅

偨偩偺婎杮揑側榑棟僎乕僩偵偟偰偼寢峔暋嶨偱偡丅

夞楬偺摦嶌傪専徹偟偰傒傑偡丅

俙俛偑偲傕偵侽偺偲偒偼慜抜偺俀偮偺俶俙俶俢僎乕僩偺擖椡偼侽丄侾偍傛傃侾丄侽偱偡偐傜弌椡偼偳偪傜傕侾偵側傝傑偡丅

偡傞偲屻抜偺俶俙俶俢偺擖椡偑侾丄侾偱偡偐傜弌椡偼侽偵側傝傑偡丅

俙俛偺擖椡偑侾丄侽偐侽丄侾偺偲偒偼慜抜偺俶俙俶俢偺偳偪傜偐偼擖椡偑侾丄侾偵側傝傑偡偐傜偦偺弌椡偼侽偵側傝傑偡丅

偡傞偲屻抜偺俶俙俶俢偺擖椡偺偳偪傜偐偼侽偲偄偆偙偲偱偡偐傜弌椡偼侾偵側傝傑偡丅

俙俛偺擖椡偑侾丄侾偺偲偒偼慜抜偺俶俙俶俢偺擖椡偼侾丄侽偍傛傃侽丄侾偱偡偐傜弌椡偼偳偪傜傕侾偵側傝傑偡丅

偡傞偲屻抜偺俶俙俶俢偺擖椡偑侾丄侾偱偡偐傜弌椡偼侽偵側傝傑偡丅

偙偺夞楬傪俵俷俽俥俤俿夞楬偵抲偒姺偊偰傒傞偲壓偺夞楬偵側傝傑偡丅

俹們倛俵俷俽俥俤俿傪俉屄偲俶們倛俵俷俽俥俤俿傪俉屄巊偄傑偡丅

偨偐偑僎乕僩侾偮偵偟偰偼戝曄側夞楬偱偡丅

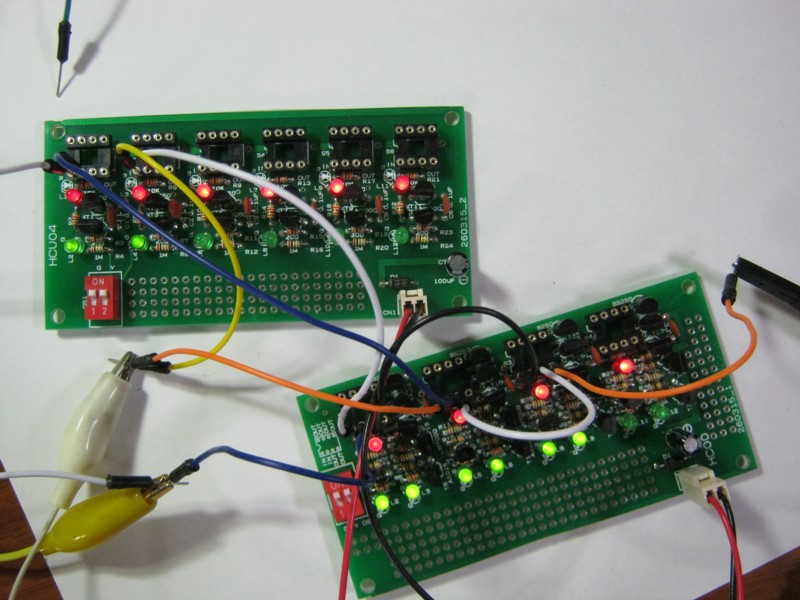

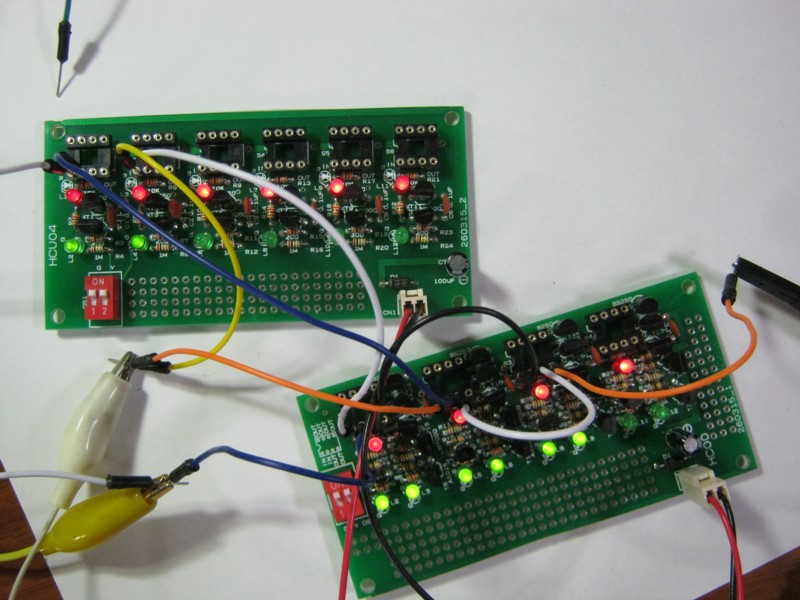

乵戞俆係夞乶偱徯夘偟傑偟偨僩儔儞僕僗僞儘僕僢僋夞楬慻棫僉僢僩偺婎斅傪巊偭偰忋偺夞楬傪慻傫偱傒傑偟偨丅

俶俙俶俢偩偗偱慻傕偆偲偡傞偲俆僎乕僩昁梫偱偡偐傜乽俫俠侽侽乿婎斅侾枃偱偼嶌傟傑偣傫丅

偙偆偄偆偲偒偵乽俫俠倀侽係乿婎斅偑栶偵棫偪傑偡丅

忋偑俫俠倀侽係婎斅偱壓偑俫俠侽侽婎斅偱偡丅

俫俠倀侽係婎斅偐傜俶俷俿僎乕僩傪俀夞楬丄俫俠侽侽婎斅偐傜俶俙俶俢僎乕僩傪俁夞楬巊偄傑偟偨丅

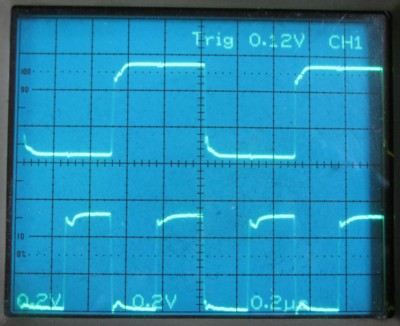

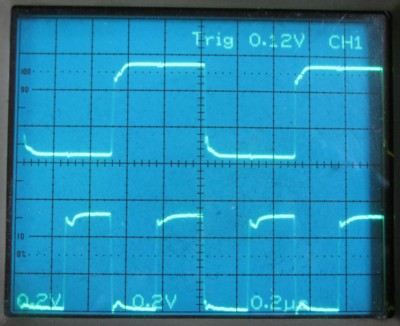

壓偼忋偺幨恀偺夞楬偵擖椡偟偨怣崋偱偡丅

俀偮偺怣崋傪嵍偐傜尒傞偲丄乵侽丆侽乶丄乵侽丆侾乶丄乵侾丆侽乶丄乵侾丆侾乶偲偄偆擖椡怣崋偵側偭偰偄傑偡丅

壓偺幨恀偼壓懁乮俠俫俀乯偵忋偺夞楬偺弌椡怣崋偑弌偰偄傑偡丅

弌椡怣崋乮壓懁丄俠俫俀乯偼嵍偐傜侽丄侾丄侾丄侽偵側偭偰偄傑偡丅

娫堘偄側偔倃俷俼偺弌椡偱偡丅

弌椡怣崋偼擖椡怣崋乮忋懁丄俠俫侾乯偵懳偟偰彮偟抶傟偑尒偊傑偡丅

俫弌椡偺搑拞偵愗傟栚偑尒偊傞偺偼偦偺抶傟偑尨場偱丄偙偺傛偆側夞楬偵崱夞偺傛偆側僋儘僢僋宆偺怣崋傪擖椡偡傞偲丄夞楬偺抶傟偵傛偭偰偙偺傛偆側僸僎偑敪惗偡傞応崌偑偁傝傑偡丅

偝偰丅

偙傟偱倃俷俼夞楬傕僩儔儞僕僗僞偱嶌傞偙偲偑偱偒偨傢偗偱偡偑丅

柺敀偔側偄偺偱偁傝傑偡偹丅

偨偐偑榑棟僎乕僩侾偮偵僩儔儞僕僗僞侾俇屄両

偟偐傕偄偢傟愢柧傪偟偰偄偒傑偡偑丄倃俷俼偼壛嶼夞楬傪峔惉偡傞僷乕僣偱傕偁傝傑偡丅

偦偆偄偆偙偲偵側傝傑偡偲丄倃俷俼扨懱偱僩儔儞僕僗僞侾俇屄偲偄偆偺偼丄偄偐偵傕懡偄両

側傫偲偐側傜側偄傕偺偐偲偄傠偄傠巚埬偟偨偺偱偡偗傟偳丄俶俙俶俢丄俶俷俿偺儗儀儖偱偼丄偙傟埲忋偼偳偆偟傛偆傕偁傝傑偣傫丅

偟偐偟丅

僩儔儞僕僗僞偺儗儀儖側傜丅

偍偍丅

側傫偲偐側傞偠傖偁傝傑偣傫偐丅

壓偺倃俷俼偺榑棟墘嶼傪偠偭偲側偑傔偰偄傑偟偨傜丅

| 俙 |

俛 |

俠 |

| 侽 |

侽 |

侽 |

| 侽 |

侾 |

侾 |

| 侾 |

侽 |

侾 |

| 侾 |

侾 |

侽 |

柇埬傪巚偄偮偒傑偟偨傛丅

僩儔儞僕僗僞夞楬偩偐傜偙偦偺丄嬛抐偺僂儔媄偱偁傝傑偡丅

敿尭偲傑偱偼偄偒傑偣傫偑僩儔儞僕僗僞侾侽屄偱偱偒傑偟偨偐傜俇屄偺嶍尭偵惉岟偟傑偟偨丅

奆條傕摢偺懱憖偱偡丅

偳偆偄偆夞楬側偺偐峫偊偰傒偰偔偩偝偄丅

師夞傑偱偺偍妝偟傒偱偡丅

僸儞僩偼俶俷俼乮僩儔儞僕僗僞係屄乯亄俶俙俶俢乮僩儔儞僕僗僞係屄乯亄僩儔儞僕僗僞俀屄偱偡丅

僩儔儞僕僗僞偱俠俹倀傪偮偔傠偆両乵戞俆俋夞乶

俀侽侾俆丏俆丏侾係倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞