俹俬俠偱倀俽俛傪両乮抦幆僛儘偐傜偺僗僞乕僩偱偡乯

俹俬俠侾俉俥侾係俲俆侽偺倀俽俛婡擻傪侾侽侽亾帺慜偺僜僼僩偱惂屼偡傞帋傒偱偡丅偟偐傕傾僙儞僽儔偱両

仚俹俬俠侾俉俥侾係俲俆侽

俹俬俠侾俉俥俀俆俆侽偱偼戝偒偡偓偰丄寁夋拞偺俿俲俉侽屳姺儅僀僐儞儃乕僪俶俢俉侽倅嘨偵偼慻傒崬傔偦偆偵側偄偙偲偑傢偐傝傑偟偨丅

倀俽俛婡擻撪憼偺俹俬俠偵偼俹俬俠侾俉俥係俆俆侽丄俹俬俠侾俉俥俀俆俆侽偺傎偐偵俀侽倫倝値偺俹俬俠侾俉俥侾係俲俆侽偑偁傞偙偲偼偪傚偭偲慜偐傜抦偭偰偄傑偟偨丅偟偐偟倀俽俛偵娭偡傞晹暘偑俹俬俠侾俉俥俀俆俆侽偲偼偐側傝堎側偭偰偄傞傛偆偱偡丅

埬偺掕偟偭偐傝揇徖偵偼傑偭偰偟傑偄傑偟偨丅 |

乵戞俈俇夞乶

仠俹俬俠侾俉俥俀俆俆侽僥僗僩夞楬恾偱偡

慜夞偼帪娫偑側偔側偭偰偟傑偄傑偟偨偺偱丄夞楬恾傪偍尒偣偡傞偙偲偑偱偒傑偣傫偱偟偨丅

夞楬恾偲尵偄傑偟偰傕偨偭偨偙傟偩偗偺娙扨側傕偺偱偡丅

乵戞俆俋夞乶偱巊偭偨夞楬偵丄俵俠俴俼偺僾儖傾僢僾掞峈偲丄係俵俫倸僋儕僗僞儖傪捛壛偟偨偩偗偱偡丅

仠俠俹倀僋儘僢僋傪曄峏偟偰僥僗僩偟偰傒傑偟偨乮俁俀俵俫倸乯

慜夞偼俠俹倀僋儘僢僋傪係俉俵俫倸偵愝掕偟偰摦嶌僥僗僩傪峴偄傑偟偨丅

慜夞乮乵戞俈俆夞乶乯愢柧偟傑偟偨傛偆偵俹俬俠侾俉俥俀俆俆侽偼丄俹俴俴夞楬傪巊偆応崌偼丄倀俽俛傪巊偆丄巊傢側偄偵偐偐傢傜偢丄俠俷俶俥俬俧偺愝掕偵傛偭偰丄侾俇丄俀係丄俁俀丄係俉俵俫倸偺偄偢傟偐偺俠俹倀僋儘僢僋傪慖戰偡傞偙偲偵側傝傑偡丅

側偍偙偺応崌偵偼奜晹偐傜嫙媼偡傞僋儘僢僋偐丄傑偨偼奜晅偗僋儕僗僞儖偺抣偼丄係丄俉丄侾俀丄侾俇丄俀侽丄俀係俵俫倸偵尷傜傟傑偡丅

傑偨奜晹偐傜嫙媼偡傞応崌偵尷偭偰係俉俵俫倸傕梌偊傞偙偲偑偱偒傑偡丅

嶲峫傑偱偵丄慜夞僥僗僩偟偨係俉俵俫倸埲奜偺僋儘僢僋傕愝掕偟偰僥僗僩傪偟偰傒傑偟偨丅

傑偢嵟弶偼俁俀俵俫倸偱偡丅

慜夞偺僾儘僌儔儉偐傜曄峏偡傞偺偼丄俠俷俶俥俬俧偺晹暘偩偗偱偡偐傜丄偦偺晹暘偩偗傪偍尒偣偡傞偙偲偵偄偨偟傑偡丅

偄傑偺偲偙傠娙扨側摦嶌僥僗僩傪偡傞偩偗偱丄傑偩倀俽俛偼巊偄傑偣傫偐傜丄倀俽俛偺偨傔偺僋儘僢僋偺愝掕偼側偔偰傕峔偄傑偣傫丅

偦偙偱慜夞偺僾儘僌儔儉偺俠俷俶俥俬俧偺愝掕偐傜倀俽俛俢俬倁亖俀偼奜偟傑偟偨乮倀俽俛傪巊傢側偄側傜丄偙偺愝掕偼偁偭偰傕柍偔偰傕摦嶌偵曄傢傝偼偁傝傑偣傫乯丅

;

CONFIG PLLDIV=1,CPUDIV=OSC2_PLL3,FOSC = XTPLL_XT,WDT=OFF,LVP=OFF

;

|

側偍丄倀俽俛傪巊傢側偄偺偱偡偐傜丄俥俷俽俠亖倃俿俹俴俴偵偟偰傕傛偄偼偢偱偼側偄偐丄偲巚偆偺偱偡偑丄俥俷俽俠亖倃俿俹俴俴偵偡傞偲丄傾僙儞僽儖僄儔乕偑昞帵偝傟偰偟傑偄傑偡丅

倀俽俛偼巊傢側偄偗傟偳傕丄倀俽俛偱倃俿傪巊偆丄偲偄偆愝掕晹暘傪奜偡偙偲偼偱偒傑偣傫乮屻傠偺丵倃俿偑偦偺晹暘偱偡乯丅

俠俹倀僋儘僢僋傪曄峏偡傞偨傔偵丄彂偒姺偊偨偺偼丄俠俹倀俢俬倁偱偡丅

慜夞偼丄俠俹倀俢俬倁亖俷俽俠侾丵俷俽俠俀偱偟偨丅偙偺愝掕偱偼俹俴俴夞楬偐傜弌椡偝傟傞俋俇俵俫倸偺侾乛俀偺係俉俵俫倸偑俠俹倀僋儘僢僋偵側傝傑偡丅

慜夞傕偍尒偣偟傑偟偨偑丄俹侾俉倖俀俆俆侽丏倝値們偺偦偺愝掕偵娭偡傞晹暘傪嶲峫傑偱偵壓偵嵞宖偄偨偟傑偡丅

; CPU System Clock Postscaler:

; CPUDIV = OSC1_PLL2 [OSC1/OSC2 Src: /1][96 MHz PLL Src: /2]

; CPUDIV = OSC2_PLL3 [OSC1/OSC2 Src: /2][96 MHz PLL Src: /3]

; CPUDIV = OSC3_PLL4 [OSC1/OSC2 Src: /3][96 MHz PLL Src: /4]

; CPUDIV = OSC4_PLL6 [OSC1/OSC2 Src: /4][96 MHz PLL Src: /6]

|

崱夞偼丄偦偙傪俠俹倀俢俬倁亖俷俽俠俀丵俷俽俠俁偵偟傑偟偨偐傜丄俋俇俵俫倸乛俁亖俁俀俵俫倸偑俠俹倀僋儘僢僋偵側傝傑偡丅

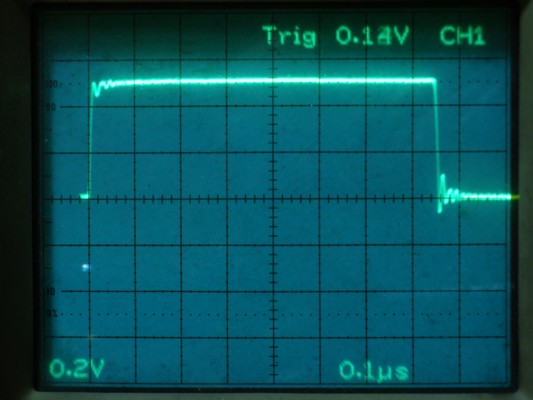

壓偼偦偺傛偆偵曄峏偟偨僥僗僩僾儘僌儔儉傪幚峴拞偺俼俙侽乮俹俷俼俿俙偺價僢僩侽乯偐傜偺弌椡攇宍偱偡丅

慜夞傕愢柧偟傑偟偨偑丄俹俬俠侾俉俥俀俆俆侽偼丄俠俹倀僋儘僢僋偺係僋儘僢僋暘偑丄柦椷偺侾儅僔儞僋儘僢僋偵側傝傑偡丅

俹俬俠偺柦椷偼侾傑偨偼俀儅僔儞僋儘僢僋偱幚峴偝傟傑偡丅

崱夞偼俠俹倀僋儘僢僋偑俁俀俵俫倸偵側偭偨偼偢偱偡偐傜丄侾俠俹倀僋儘僢僋偼侾乛俁俀兪倱倕們偱偡丅

侾儅僔儞僋儘僢僋偼偦偺係攞偱偡偐傜侾乛俉兪倱倕們偱偡丅

崱夞偺僾儘僌儔儉偱偼丄俼俙侽偺弌椡偼俁儅僔儞僋儘僢僋偛偲偵侾偲侽偑岎屳偵斀揮偟偰弌椡偝傟傑偡丅

偡傞偲俫傑偨偼俴偺婜娫偼丄俁乛俉亖侽丏俁俈俆兪倱倕們偵側傝傑偡丅

俁俈俆値倱倕們偱偡丅

寁嶼捠傝偺弌椡寢壥偵側偭偰偄傑偡丅

仠俠俹倀僋儘僢僋傪曄峏偟偰僥僗僩偟偰傒傑偟偨乮俀係俵俫倸乯

摨條偵偟偰丄崱搙偼丄俠俷俶俥俬俧偺俠俹倀俢俬倁偺愝掕傪丄俠俹倀俢俬倁亖俷俽俠俁丵俷俽俠係偵曄峏偟傑偟偨丅

;

CONFIG PLLDIV=1,CPUDIV=OSC3_PLL4,FOSC = XTPLL_XT,WDT=OFF,LVP=OFF

;

|

俋俇俵俫倸乛係亖俀係俵俫倸偑俠俹倀僋儘僢僋偵側傝傑偡丅

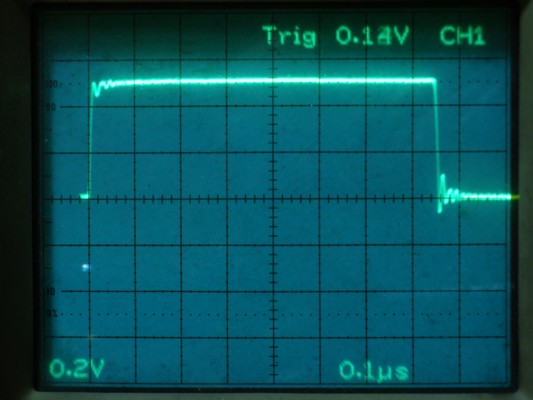

壓偼偦偺傛偆偵曄峏偟偨僥僗僩僾儘僌儔儉傪幚峴拞偺俼俙侽乮俹俷俼俿俙偺價僢僩侽乯偐傜偺弌椡攇宍偱偡丅

崱夞偼俠俹倀僋儘僢僋偑俀係俵俫倸偵側偭偨偼偢偱偡偐傜丄侾俠俹倀僋儘僢僋偼侾乛俀係兪倱倕們偱偡丅

侾儅僔儞僋儘僢僋偼偦偺係攞偱偡偐傜侾乛俇兪倱倕們偱偡丅

俼俙侽偺弌椡偼俁儅僔儞僋儘僢僋偛偲偵侾偲侽偑岎屳偵斀揮偟偰弌椡偝傟傑偡偐傜丄俫傑偨偼俴偺婜娫偼丄俁乛俇亖侽丏俆兪倱倕們偵側傝傑偡丅

崱夞傕寁嶼捠傝偺弌椡寢壥偵側傝傑偟偨丅

仠俠俹倀僋儘僢僋傪曄峏偟偰僥僗僩偟偰傒傑偟偨乮侾俇俵俫倸乯

崱搙偼丄俠俹倀俢俬倁亖俷俽俠係丵俷俽俠俇偵曄峏偟傑偟偨丅

;

CONFIG PLLDIV=1,CPUDIV=OSC4_PLL6,FOSC = XTPLL_XT,WDT=OFF,LVP=OFF

;

|

俋俇俵俫倸乛俇亖侾俇俵俫倸偑俠俹倀僋儘僢僋偵側傝傑偡丅

壓偼偦偺傛偆偵曄峏偟偨僥僗僩僾儘僌儔儉傪幚峴拞偺俼俙侽乮俹俷俼俿俙偺價僢僩侽乯偐傜偺弌椡攇宍偱偡丅

俠俹倀僋儘僢僋偼侾俇俵俫倸偵側偭偨偼偢偱偡偐傜丄侾俠俹倀僋儘僢僋偼侾乛侾俇兪倱倕們偱偡丅

侾儅僔儞僋儘僢僋偼偦偺係攞偱偡偐傜侾乛係兪倱倕們偱偡丅

俼俙侽偺弌椡偼俁儅僔儞僋儘僢僋偛偲偵侾偲侽偑岎屳偵斀揮偟偰弌椡偝傟傑偡偐傜丄俫傑偨偼俴偺婜娫偼丄俁乛係亖侽丏俈俆兪倱倕們偵側傝傑偡丅

崱夞傕寁嶼捠傝偺弌椡寢壥偵側傝傑偟偨丅

俠俹倀傪偮偔傠偆両戞俆侽俁夞乮俀侽侾侽丏俆丏俀侽倳倫倢倧倎倓乯傪嵞曇廤

俹俬俠偱倀俽俛傪両乵戞俈俇夞乶

俀侽侾侾丏俈丏侾俀倳倫倢倧倎倓

慜傊

師傊

栚師傊栠傞

儂乕儉儁乕僕僩僢僾傊栠傞