〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

いつか使うことになるだろうと思ってはいたのですが。

何を今頃になって、というようなものですが。

ようやく本気で、CPLDと四つに取り組みます。

〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜〜

[第47回]

●CPLD版VGAIFボード

ものを書くというのはなかなかにつらい作業です。

自分ではわかっていても、それを人に伝えるために文章にしようとすると、なかなか要領を得ません。

そこへもってきて、作業が思うように進まず、理解できないトラブルに遭遇したりしますと、もうホームページどころではなくなってしまいます。

そんなこんなでどうしても記事の進行は思わしくありません。

記事のほうがもたもたしているうちに、実作業のほうが先行していきます。

当記事もやっとCPLD版VGAインターフェースの回路図の説明ができたところなのですが、実作業のほうはとりあえずの試作基板もできていて、VHDLプログラムもできてしまいました。

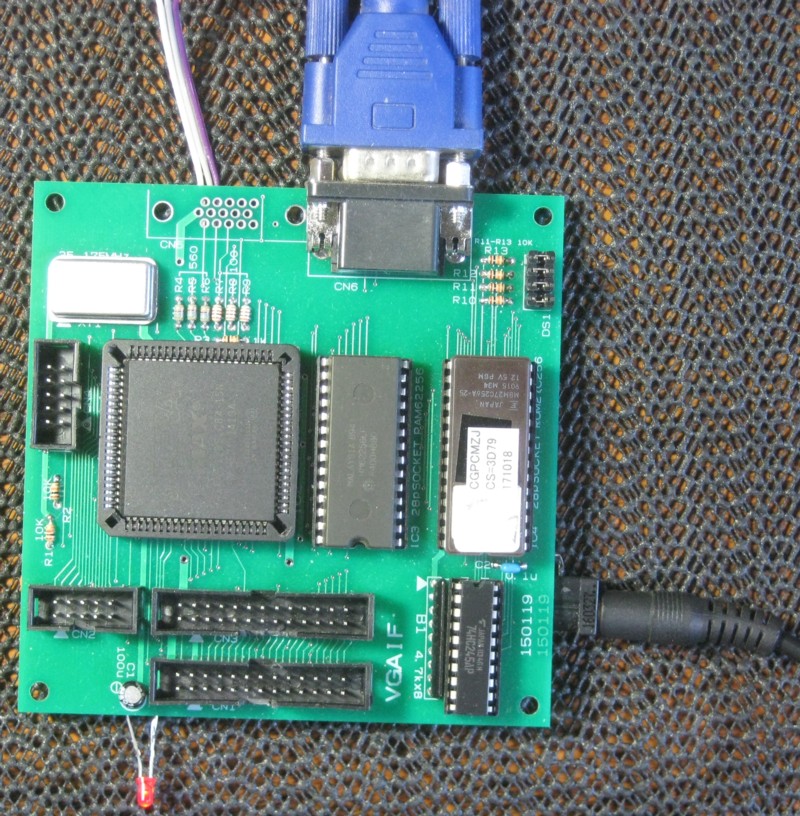

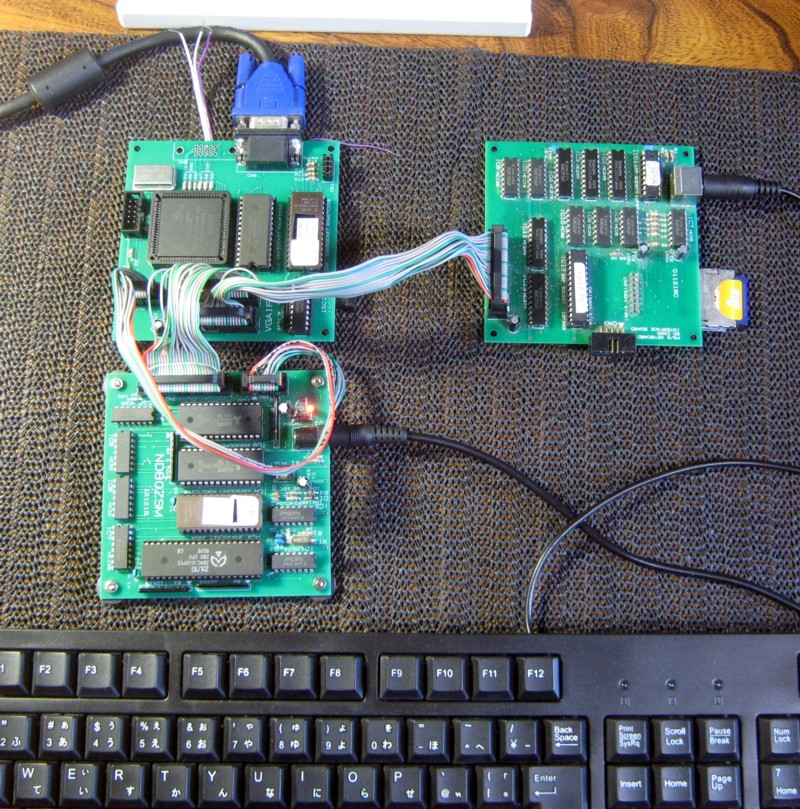

下は試作基板に必要なパーツを実装した写真です。

前回の最後にお見せしたCPLD版VGAインターフェース回路を実際に基板にしたものです。

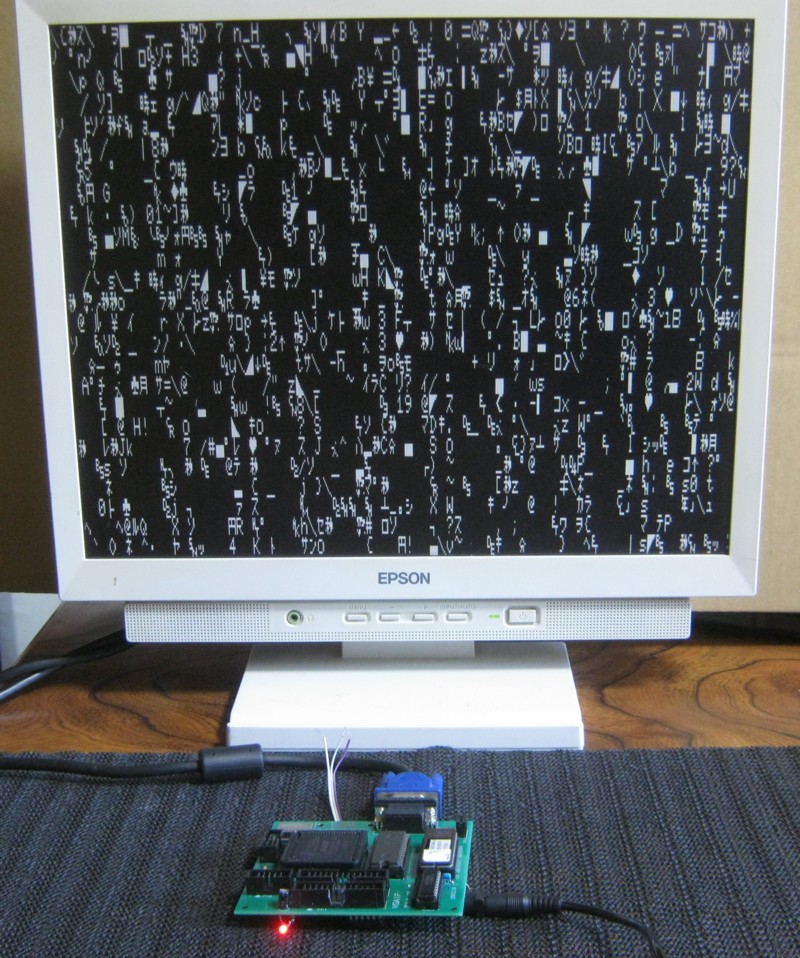

VHDLプログラムもできていますので、この通りディスプレイに接続して電源を入れるとランダムな文字が表示されます。

CPLD版VGAインターフェース基板だけで表示が行なわれています。

CPUボードはまだつないでいません。

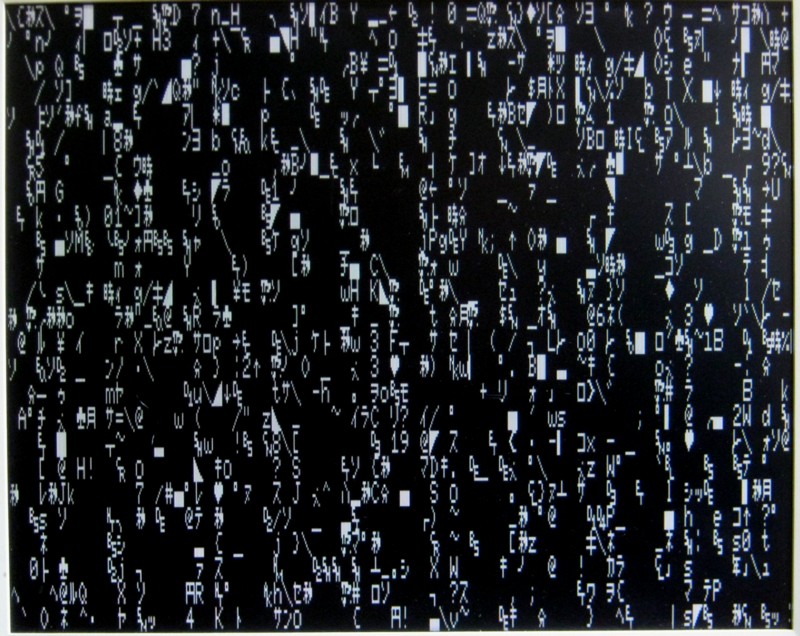

ディスプレイ画面を正面から撮りました。

●ND80ZSMに接続しました

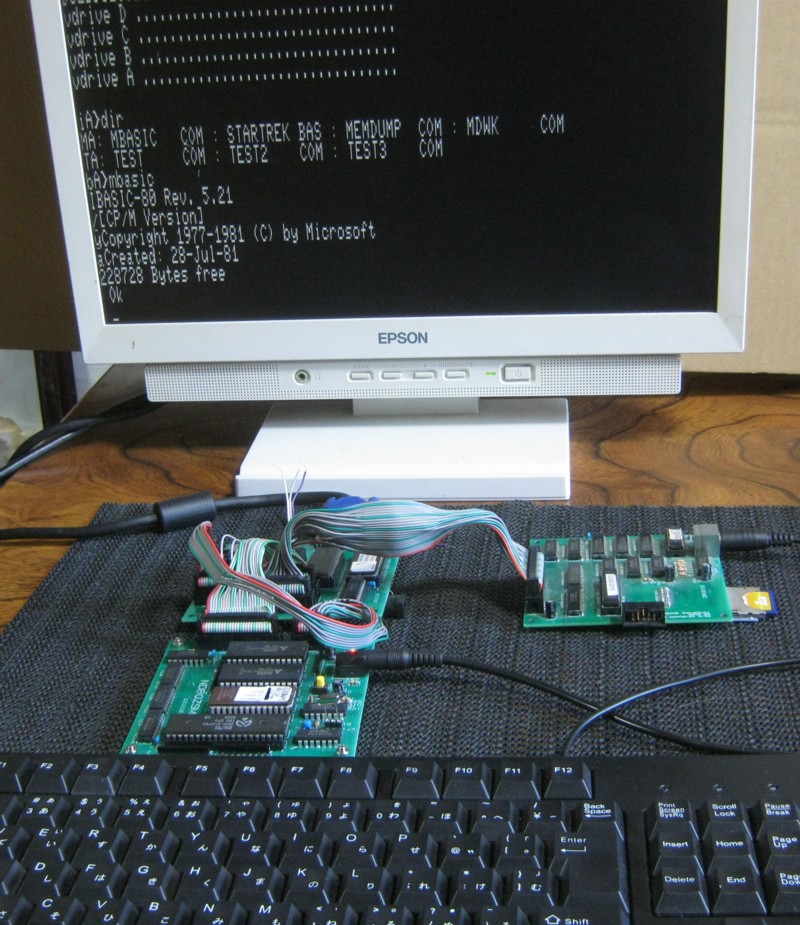

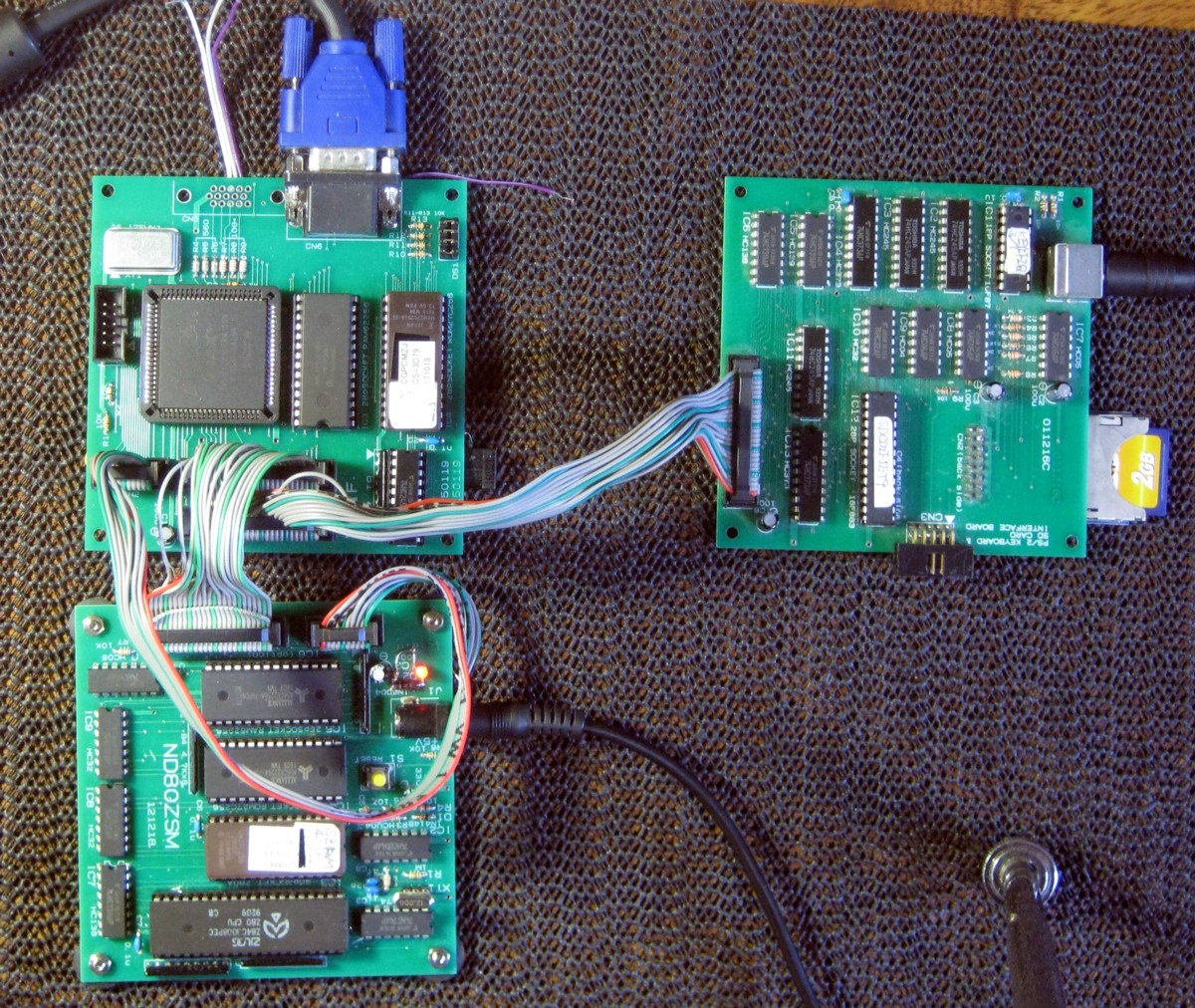

CPUボード、キーボードを接続して、本番テストです。

手前はND80ZSMで右側はJISフルキーボードIF+SDカードIFボードです。

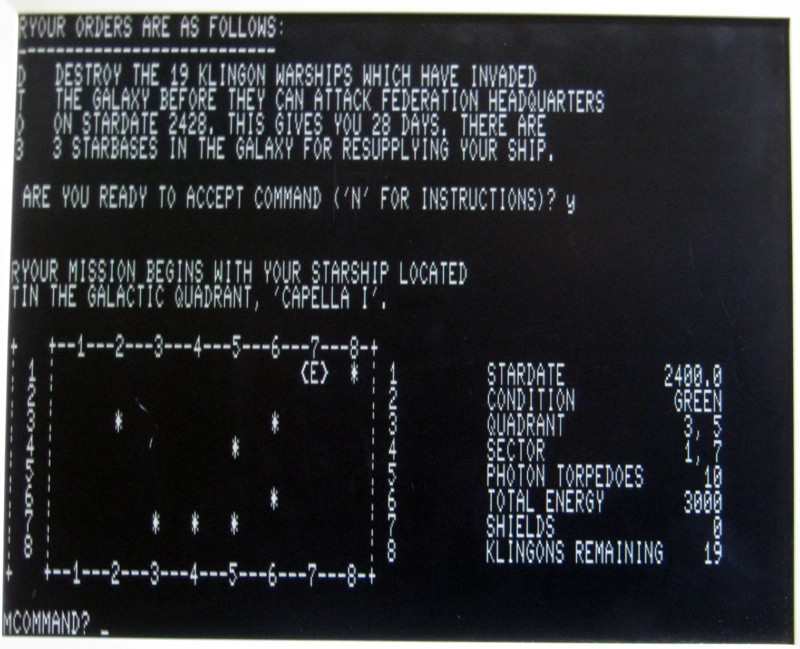

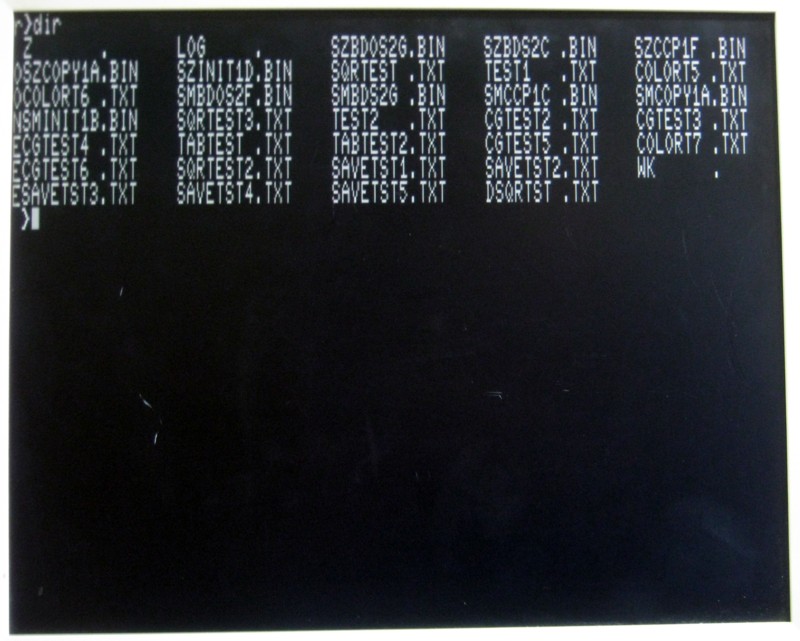

独立版のZB3DOS(CP/M互換DOS)を起動して、MBASICを起動しています。

ボードを接続しているところを上から撮影しました。

もう少し接近して撮りました。

一見すると大成功のように見えますが。

ちょいとまずいところがみつかりました。

実はVHDLプログラムを書いていて、いいのかなあというところがあったのですが。

やっぱりよくはありませんでした。

下の2枚の写真をご覧いただいて、どこかがおかしいことにお気付きになりませんでしょうか?

CPLD入門![第47回]

2019.5.12upload

前へ

次へ

ホームページトップへ戻る