倛倐倢値倠倵倠俀偼侾暥帤偺昞帵偺抶傟傪挷惍偡傞偨傔偺怣崋偱偡乮乵戞係俉夞乶嶲徠乯丅

偩偲偡傞偲偙偺倕倢倱倝倖暥偼昁梫側暥偺偼偢偱偡偑乧丅

乵戞俆侽夞乶偵彂偄偰偄傑偡傛偆偵丄偙偺倕倢倱倝倖暥傪僐儊儞僩暥偱偼側偔偡傞偲丄偍偐偟側摦嶌偵側傝傑偡丅

悈暯曽岦偼俉侽帤昞帵偺偼偢側偺偵丄嵍抂偺侾暥帤偟偐昞帵偝傟側偔側偭偰偟傑偄傑偡丅

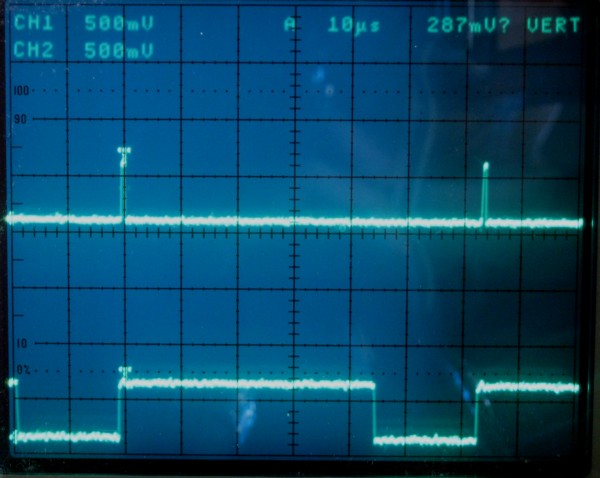

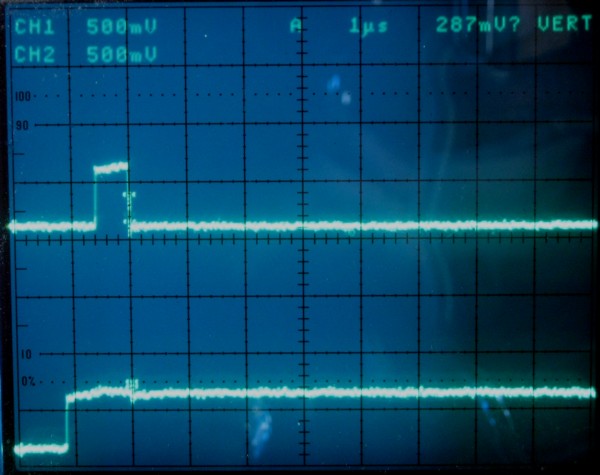

僆僔儘偱妋擣偟偰傒傑偡偲丄倛倐倢値倠倵倠俀偑棫偪忋偑偭偰偐傜偡偖偵棊偪偰偟傑偆偙偲偑傢偐傝傑偟偨丅

忋懁乮俠俫侾乯偑倛倐倢値倠倵倠俀偱壓懁乮俠俫俀乯偑倛倐倢値倠倵倠偱偡丅

悈暯幉傪侾侽攞偵偟偰傒傑偟偨丅

妋偐偵偍偐偟偄偱偡丅

倛倐倢値倠倵倠俀偑倛倐倢値倠倵倠偵侾暥帤暘抶傟偰棫偪忋偑偭偰偄傞偲偙傠偼僾儘僌儔儉捠傝側偺偱偡偑丄偦偺偁偲侾暥帤昞帵婜娫屻偵偡偖偵棊偪偰偟傑偭偰偄傑偡丅

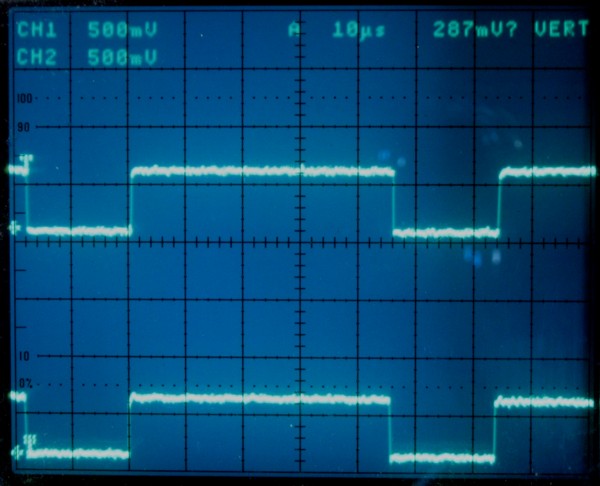

偦偙偱偝偒傎偳偺倕倢倱倝倖暥傪僐儊儞僩暥偵偡傞偲丄傑偲傕側怣崋偵側傝傑偡丅

側偤偙偺傛偆側偍偐偟側偙偲偵側偭偰偟傑偆偺偐丄偦偺帪揰偱偼慡偔尒摉傕偮偒傑偣傫偱偟偨丅

偙傟偵偼擸傒傑偟偨丅

偲偵偐偔倕倢倱倝倖暥傪僐儊儞僩暥偵偡傟偽丄惓忢偵昞帵偡傞傛偆偵側傞偺偱偡偑丄偦偺傑傑偱偼堦斣嵍偵昞帵偝傟偰偄傞乽僑儈乿偑徚偊偰偔傟傑偣傫丅

巇曽偑側偄偺偱悈暯摨婜怣崋傪侾暥帤暘偢傜偟偨偲偙傠丄嵍懁偺僑儈昞帵偺侾暥帤暘偑夋柺偺嵍抂偵塀傟偰尒偊側偔側傝傑偟偨丅

傑偁丄偛傑偐偟偱偡偑丄偙偺帪揰偱偼偦偺曽朄偟偐巚偄偮偐側偐偭偨偺偱丄偦偆偄偆偙偲偵偟傑偟偨丅

崱夞偺俠俼俿俬俥梡偺倁俫俢俴僾儘僌儔儉偱傕慡偔摨偠忬懺偩偭偨偺偱偡偑丄偙偺傑傑偵偟偰偍偔偺偼偳偆偵傕婥偑恑傒傑偣傫丅

偙傫側偽偐側偙偲偼側偄偼偢丄偲偄偆偙偲偱偁傟偙傟帋峴嶖岆傪廳偹傑偟偨丅

摨偠傛偆側偙偲傪孞傝曉偟帋偟偰偍傛偦俁擔傎偳傪旓傗偟偰偟傑偭偨偲巚偄傑偡丅

偙傟偼挿偄娫偺宱尡偐傜摼偨傎偲傫偳妋怣偺傛偆側傕偺側偺偱偡偑丅

孞傝曉偟帋偟偰傕椙偄寢壥偑摼傜傟偢丄傕偆掹傔偰偟傑偍偆丄偲巚偭偰傕偦偙偱搳偘偰偟傑偭偰偼偄偗傑偣傫丅

傕偆懯栚偩丄偲巚偭偨偲偒偵偙偦丄傕偆堦夞僩儔僀偟偰傒傞偲丄堄奜偵傕偦傟傑偱栚偺慜偵棫偪偼偩偐偭偰偄偨偳偆偵傕側傜側偄暻偑姠夝偟偰偁偭偗側偔夝寛偟偰偟傑偄傑偡丅

崱夞傕偦偆偄偆偙偲偱偟偨丅

慜夞彂偒傑偟偨俠俼俿俬俥梡偺僾儘僌儔儉偑偦偺夝寛嶔偱偟偨丅

暋悢偺暿乆偺怣崋偑偁偭偰丄偦傟傜偼偦傟偧傟暿乆偺僞僀儈儞僌偱摦嶌偡傞偗傟偳丄偄偢傟偺怣崋傕摨偠侾偮偺怣崋偵傛偭偰摦嶌偡傞傛偆側応崌偵丄巹偼偦偆偄偆怣崋偼侾偮偺俹俼俷俠俤俽俽暥偵傑偲傔偰婰弎偟偰偟傑偭偰傕傛偄丄偲峫偊偰偄傑偟偨丅

偨偲偊偽崱夞偺倛倐倢値倠倵倠丄倛倐倢値倠倵倠俀丄倛倱倷値們倵倠偼偄偢傟傕們値倲倰俀偵傛偭偰摦嶌偟傑偡丅

偦偆偄偆働乕僗偱偡丅

偲偙傠偑偦傟偱偼傑偢偄応崌偑偁傞傛偆偱偡丅

摨偠侾偮偺怣崋偵傛偭偰摦嶌偡傞怣崋夞楬偱傕丄偦傟偧傟暿屄偺俹俼俷俠俤俽俽暥偱婰弎偟側偄偲岆摦嶌偵偮側偑傞応崌偑偁傞傛偆偱偡丅

夞楬恾偺応崌偵偼摉慠偺偙偲偲偟偰丄摨偠侾偮偺怣崋傪傕偲偵偟偰丄偦偙偵暋悢偺夞楬傪偮側偘偨傝偟傑偡丅

倁俫俢俴僾儘僌儔儉偺応崌偵侾偮偺俹俼俷俠俤俽俽暥偱暋悢偺怣崋偺摦嶌傪婰弎偡傞偲丄側傫偱偟傚偆偐傛偔傢偐傝傑偣傫偑丄堦庬偺婑惗夞楬偺傛偆側傕偺偑惗惉偝傟偰偟傑偭偰丄偦傟偑巚傢偸岆摦嶌傪堷偒婲偙偟偰偟傑偆偙偲偑偁傞傛偆偱偡丅

偙偺偙偲偑俵俙倃俈侽侽侽俽偵屌桳偺僋僙偺傛偆側傕偺側偺偐丄偁傞偄偼堦斒揑偵倁俫俢俴偱婰弎偡傞応崌偺埫栙偺僞僽乕側偺偐偼傛偔傢偐傝傑偣傫丅

僀儞僞乕僱僢僩偱偞偭偲挷傋偰傒偨偺偱偡偑丄偦偆偄偆偙偲傪柧帵偟偰偄傞偲偙傠偵偼峴偒摉偨傝傑偣傫偱偟偨丅

偲偵偐偔丅

偳偆傗傜偦偆偄偆偙偲傜偟偄丄偲偄偆寢榑偑摼傜傟傑偟偨偺偱丄慜夞偍尒偣偟傑偟偨傛偆偵丄俠俼俿俬俥梡偺倁俫俢俴僾儘僌儔儉偱偼偦偺傛偆偵彂偔偙偲偱惓偟偄寢壥偑摼傜傟傑偟偨丅

偦偺寢壥傪庴偗偰丄倁俧俙俬俥梡偺倁俫俢俴僾儘僌儔儉傕摨偠傛偆偵丄倛倐倢値倠倵倠丄倛倐倢値倠倵倠俀丄倛倱倷値們倵倠傪偦傟偧傟暿偺俹俼俷俠俤俽俽暥偵暘偗偰婰弎偟偨偲偙傠丄倕倢倱倝倖暥傪僐儊儞僩峴偵偡傞偙偲側偔惓忢偵昞帵偝傟傞傛偆偵側傝傑偟偨丅

偙傟偵偰傛偆傗偔堦審棊拝偱偡丅

俠俹俴俢擖栧両乵戞俆俆夞乶

俀侽侾俋丏俇丏俀倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞