仠俤俹俵俈侾俀俉俽俴俠俉係斉倁俧俙俬俥亄俠俼俿俬俥夞楬恾

俤俹俵俈侾俀俉俽俴俠俉係斉倁俧俙俬俥亄俠俼俿俬俥乮俉侽帤昞帵乛係侽帤昞帵愗姺乯偺夞楬恾偱偡丅

夞楬恾偼乵戞係俇夞乶偱傕偍尒偣偟傑偟偨偑偦傟偼倁俧俙俬俥偺傒偺夞楬恾偱偟偨丅

偦偺屻偵俠俼俿俬俥傕娷傔偨婎斅傪嶌傝捈偟傑偟偨丅

壓偼俠俼俿俬俥夞楬傕捛壛偟偨嵟廔揑側夞楬恾偱偡丅

傕偲偼俫俠俵俷俽偺儘僕僢僋俬俠係侽屄傎偳偱峔惉偟偰偄偨夞楬偑俤俹俵俈侾俀俉俽俴俠俉係偵抲偒姺傢偭偰偟傑偄傑偟偨丅

偙傟偼側偐側偐偵偡偛偄傕偺偩偲巚偄傑偡丅

岺晇師戞偱傕偭偲偄傠偄傠側夞楬偵巊偊偦偆偱偡丅

俠俹俴俢偵嫽枴偼偁偭偨偺偱偡偑懡朲偵偐傑偗偰丄挿偄娫庤傪弌偣偢偵棃偰偟傑偄傑偟偨丅

幚嵺偵杮婥偱庢傝慻傫偱傒傑偡偲丄妋偐偵曋棙側傕偺偩偲巚偄傑偡丅

偙傟傪婡夛偵偄傠偄傠側夞楬偵墳梡偟偰傒偨偄偲巚偄傑偡丅

仠昞帵夋柺偺幨恀

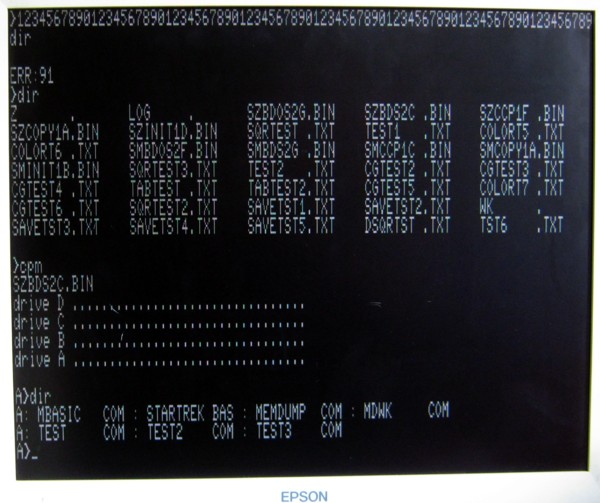

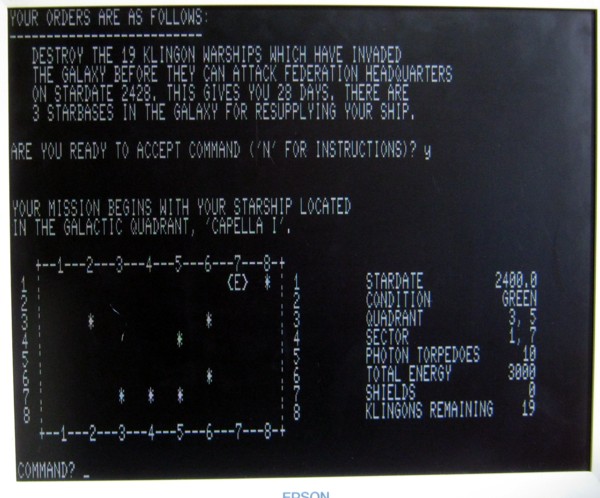

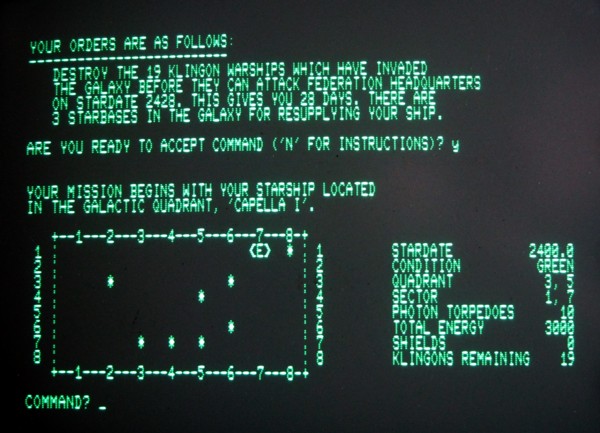

枅夞摨偠傛偆側幨恀傪偍尒偣偟偰偄傑偡偑丄倁俧俙俬俥夞楬傕娷傔偰倁俫俢俴僾儘僌儔儉傪廋惓偟傑偟偨偺偱丄擮偺偨傔偵昞帵僥僗僩傪偟傑偟偨丅

壓偼倁俧俙僨傿僗僾儗僀偱偺昞帵偱偡丅

抂偐傜抂傑偱偒偭偪傝俉侽帤偑惓偟偔昞帵偝傟偰偄傑偡丅

摿偵栤戣偼側偄傛偆偱偡丅

壓偼掕斣偱偡偗傟偳丄撈棫宆偺倅俛俁俢俷俽乮俠俹乛俵屳姺俢俷俽乯傪婲摦偟傑偟偨丅

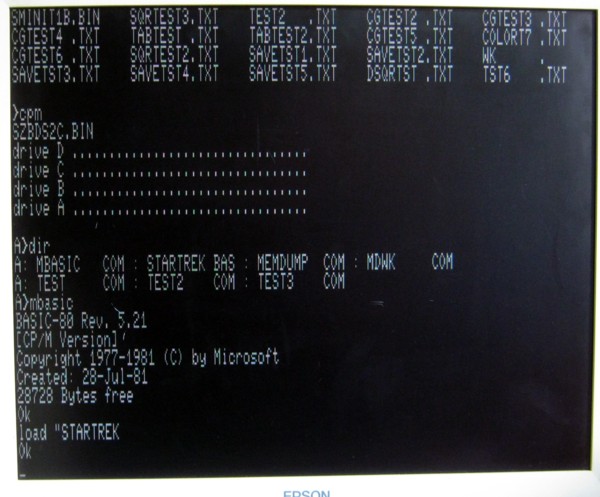

懕偄偰俵俛俙俽俬俠傪婲摦偟偰丄俽俿俙俼俿俼俤俲傪儘乕僪偟傑偟偨丅

俽俿俙俼俿俼俤俲偺幚峴夋柺偱偡丅

俠俼俿僨傿僗僾儗僀偺昞帵偵愗傝姺偊傑偟偨丅

搑拞偮傑偯偒側偑傜偱偡偑丄偙傟偱傗偭偲俠俹俴俢斉偺倁俧俙俬俥亄俠俼俿俬俥偑弌棃忋偑傝傑偟偨丅

俠俹俴俢擖栧両乵戞俇俇夞乶

俀侽侾俋丏俇丏侾俁倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞