乵怴楢嵹乶俠俹俴俢擖栧両

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

偄偮偐巊偆偙偲偵側傞偩傠偆偲巚偭偰偼偄偨偺偱偡偑丅

壗傪崱崰偵側偭偰丄偲偄偆傛偆側傕偺偱偡偑丅

傛偆傗偔杮婥偱丄俠俹俴俢偲巐偮偵庢傝慻傒傑偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞俉俆夞乶

仠俹倝値丂俹倢倎値値倕倰

僐儞僷僀儖偑嵪傫偩偁偲丄嵟屻偺巇忋偘偲偟偰傗傜側偔偰偼偄偗側偄偺偼丄抂巕柤傪幚嵺偺奜晹抂巕偵寢傃偮偗傞嶌嬈偱偡丅

俻倳倎倰倲倳倱嘦偺応崌倁俫俢俴僜乕僗僾儘僌儔儉偵偼抂巕斣崋偼婰弎偟傑偣傫丅

抂巕柤偺傒傪婰弎偟傑偡偐傜丄偦偺傑傑偱偼幚嵺偵俠俹俴俢偵僾儘僌儔儉傪幚峴偝偣傞偙偲偼偱偒傑偣傫丅

抂巕柤傪抂巕斣崋偵寢傃偮偗傞偵偼俹倝値丂俹倢倎値値倕倰傪巊偄傑偡丅

俹倝値丂俹倢倎値値倕倰偼帇妎揑偱娙曋側偺偱偡偑丄僺儞悢偑懡偄俠俹俴俢偵側偭偰偔傞偲丄侾杮侾杮偮側偄偱偄偔庤娫偼側偐側偐偵柺搢側嶌嬈偵側偭偰偒傑偡丅

偍傑偗偵偨偲偊偽偁傞僜乕僗僾儘僌儔儉傪傕偲偵偟偰丄暿偺僜乕僗僾儘僌儔儉傪嶌偭偨応崌側偳偱傕丄俹倝値丂俹倢倎値値倕倰偺嶌嬈偼嵟弶偐傜傗傝捈偟傪偟側偗傟偽側傝傑偣傫丅

側傫偲偐側傜側偄偐側偁丄偲偄偆婥帩偪偵側傝傑偡丅

幚偼偡偱偵嶌嬈嵪傒偺抂巕愙懕傪傕偲偵偟偰丄怴偟偄倁俫俢俴僾儘僌儔儉梡偵堦晹乮傑偨偼慡晹乯傪偦偺傑傑棙梡偡傞棤媄偑偁傝傑偡丅

偦偺棤媄偵偮偄偰傕愢柧偑恑傫偱偒傑偟偨傜丄偍嫵偊偄偨偟傑偡丅

崱夞偼嵟弶偱偡偺偱丄俹倝値丂俹倢倎値値倕倰傪偼偠傔偐傜巊偆偲偙傠偐傜愢柧傪偟傑偡丅

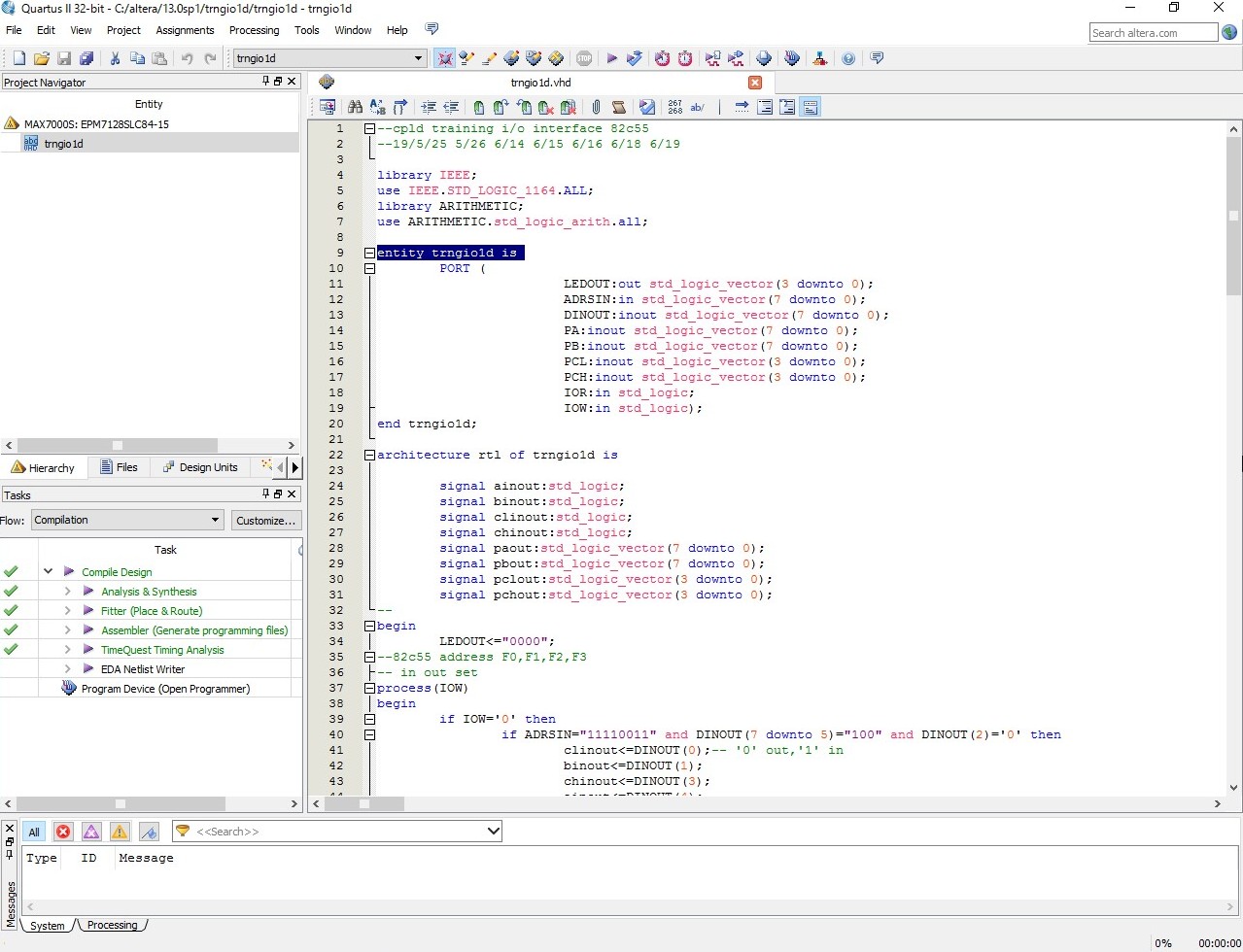

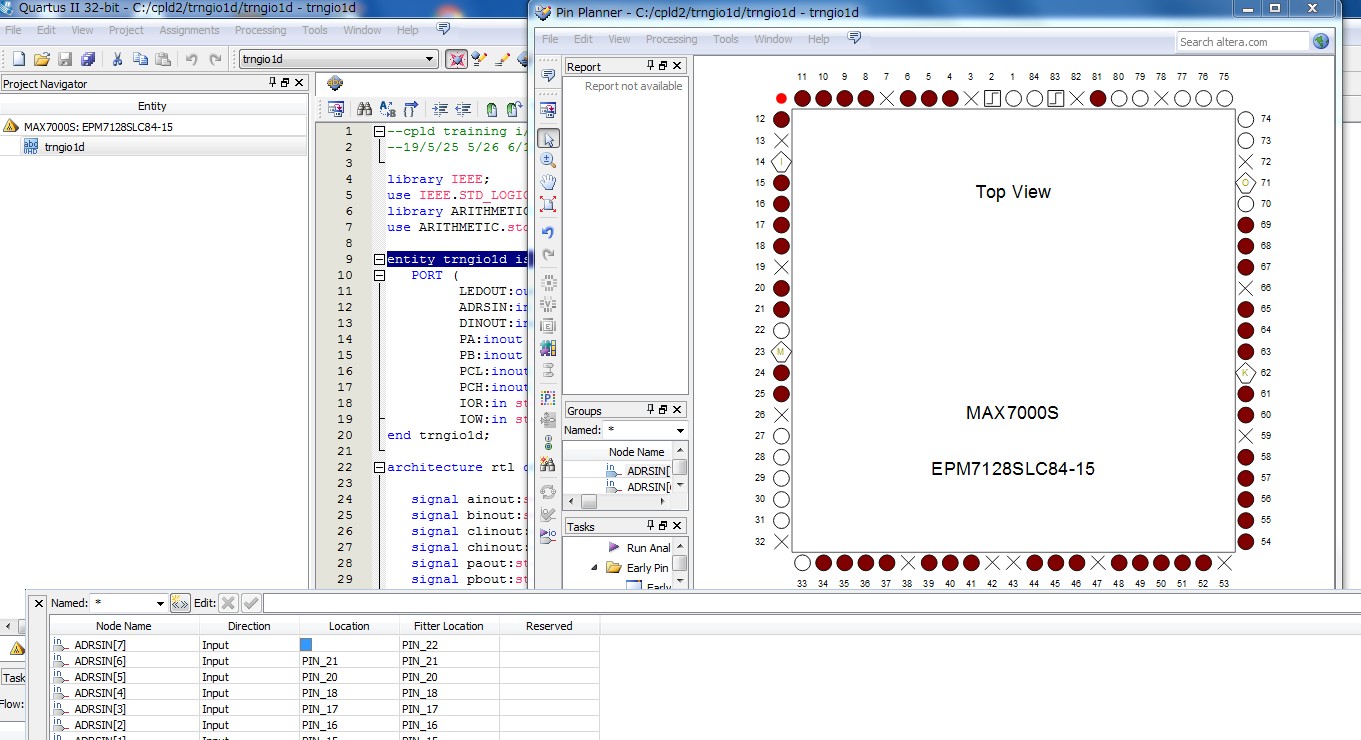

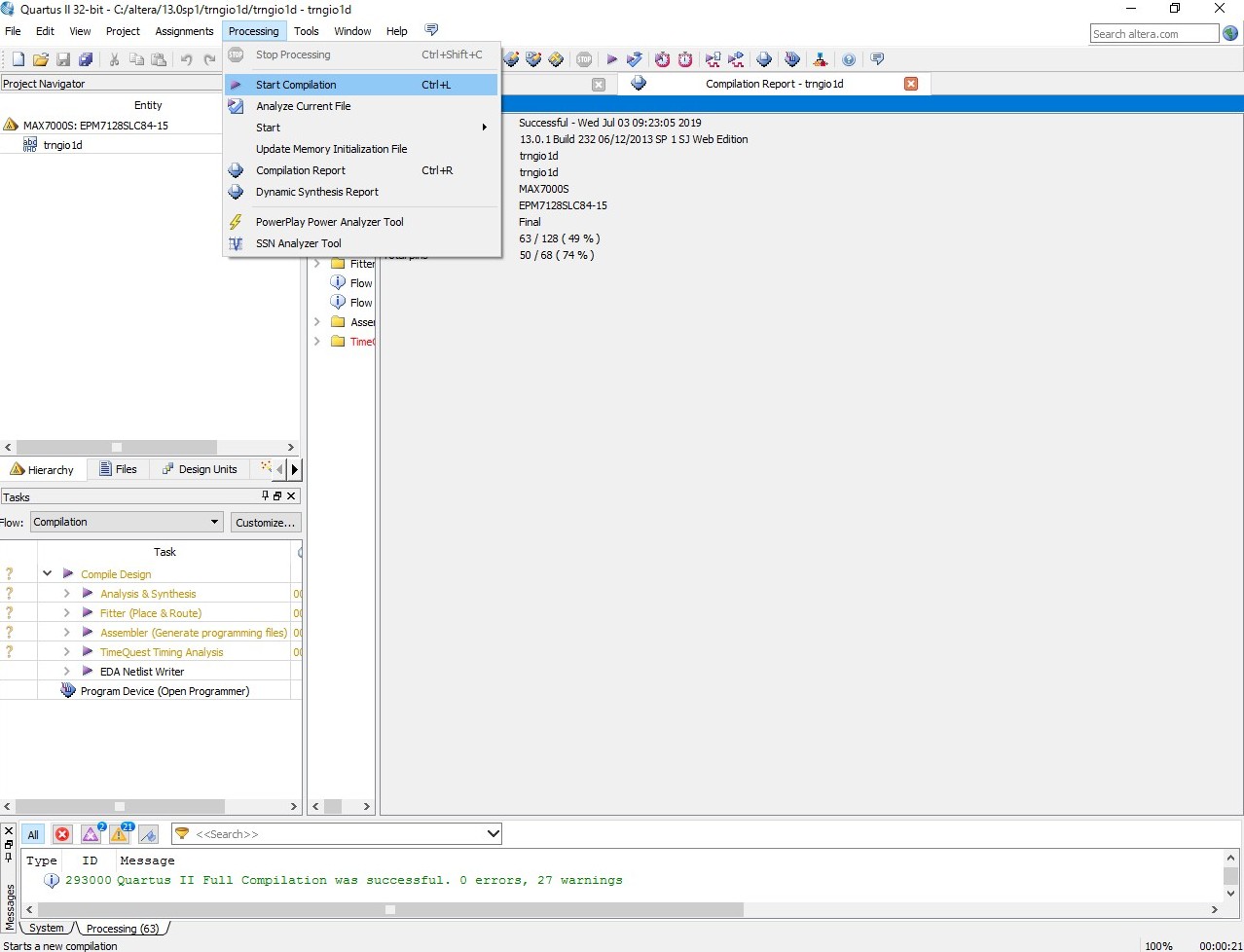

慜夞偲摨偠傛偆偵偟偰俻倳倎倰倲倳倱嘦倁侾俁丏侽倱倫侾傪婲摦偟偰丄倲倰値倗倝倧侾倓丏倴倛倓僜乕僗僾儘僌儔儉偑昞帵偝傟偰偄傞忬懺偺偲偙傠傑偱恑傫偱偔偩偝偄丅

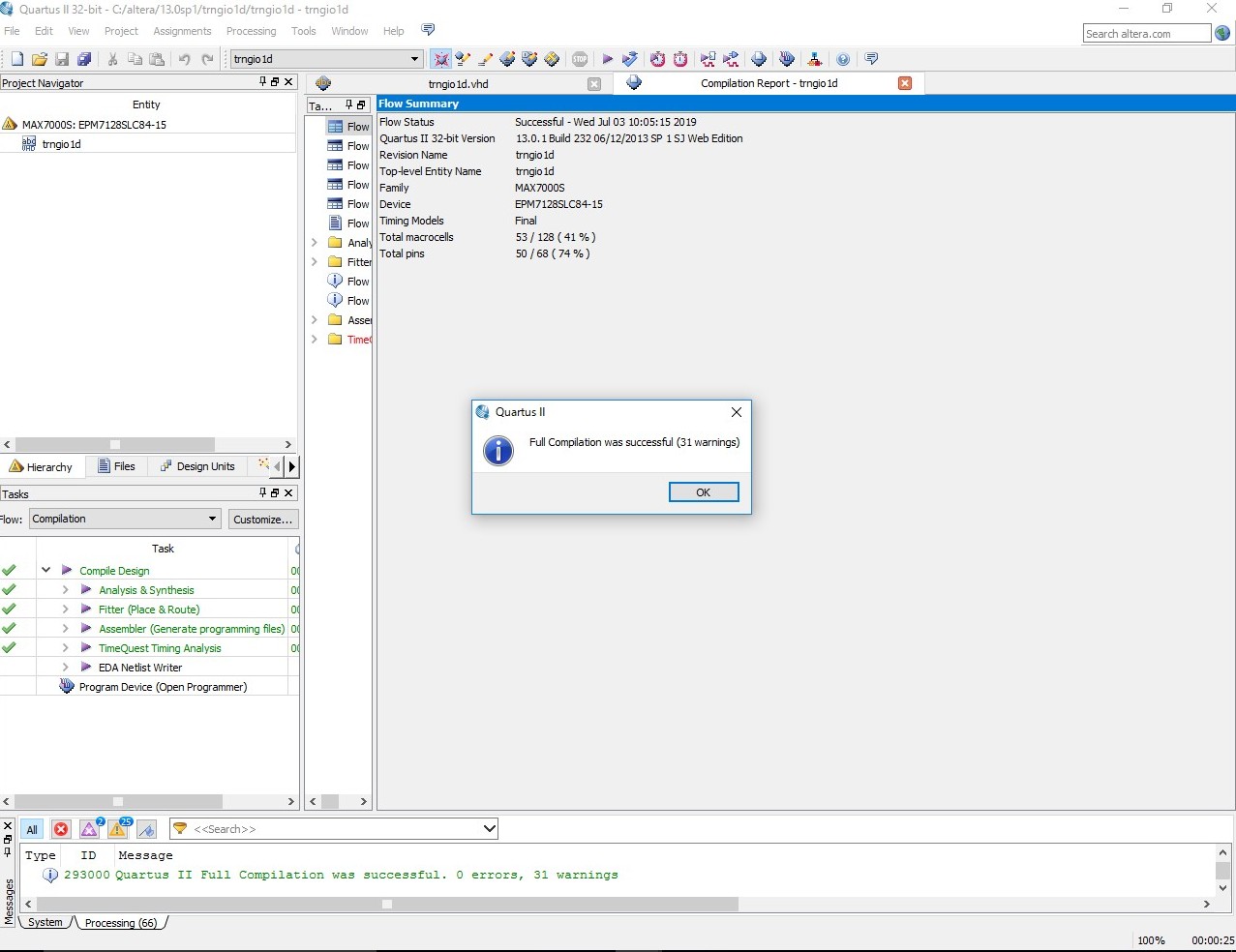

慜夞偺僐儞僷僀儖嶌嬈偵偐偐傞捈慜偺忬懺偱偡丅

壓偺夋柺偺忬懺偱偡丅

俹倝値丂俹倢倎値値倕倰偼僐儞僷僀儖偺偁偲偱幚峴偟傑偡丅

僜乕僗僾儘僌儔儉傪庤捈偟偡傞側偳偟偰丄抂巕柤偑曄傢偭偨傝丄捛壛嶍彍傪峴側偭偨傝偟偨偲偒傕丄傕偪傠傫嵞僐儞僷僀儖偟傑偡偑丄偦偺偲偒傕俹倝値丂俹倢倎値値倕倰偱怴偟偄抂巕柤偺忣曬傪斀塮偝偣傞昁梫偑偁傝傑偡丅

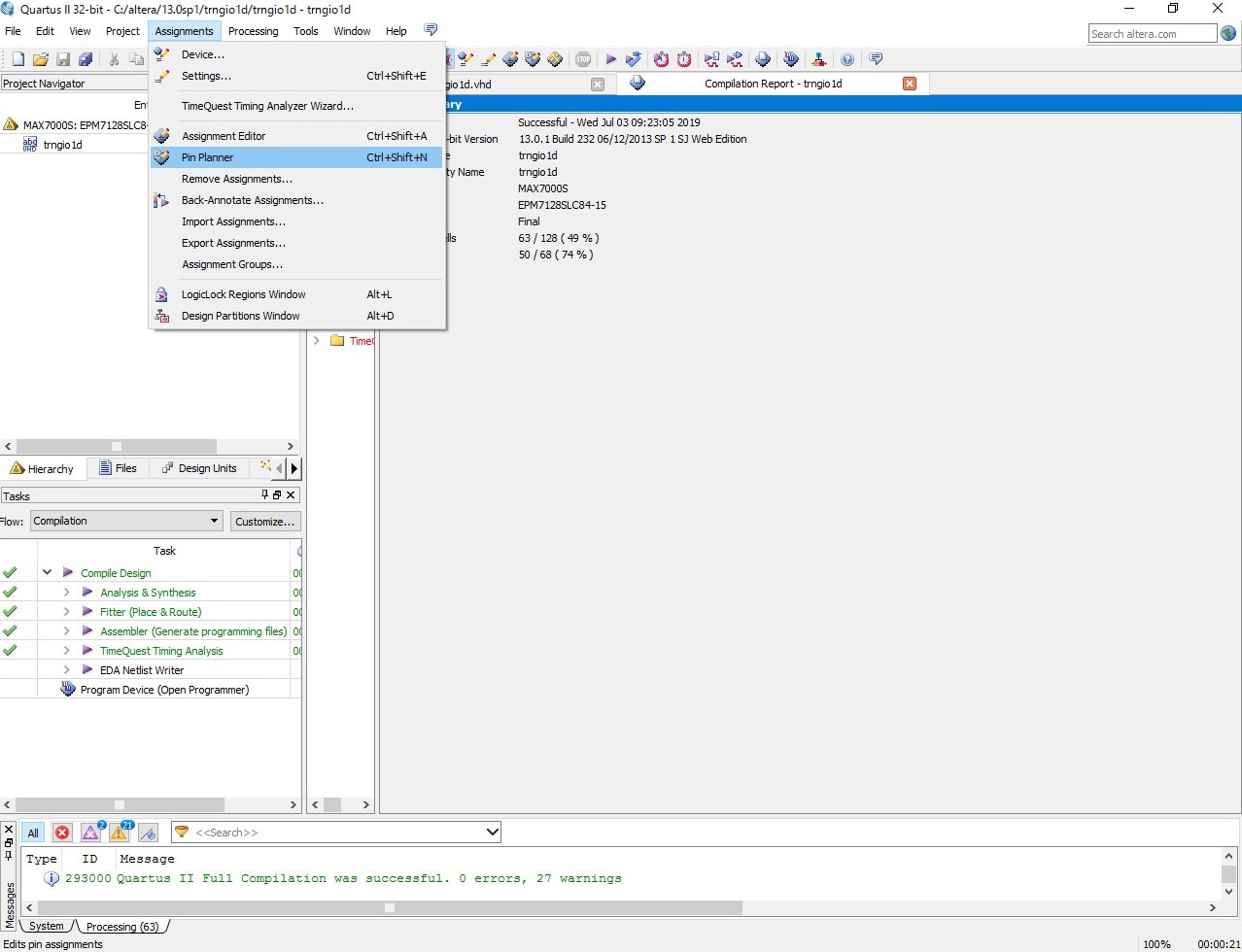

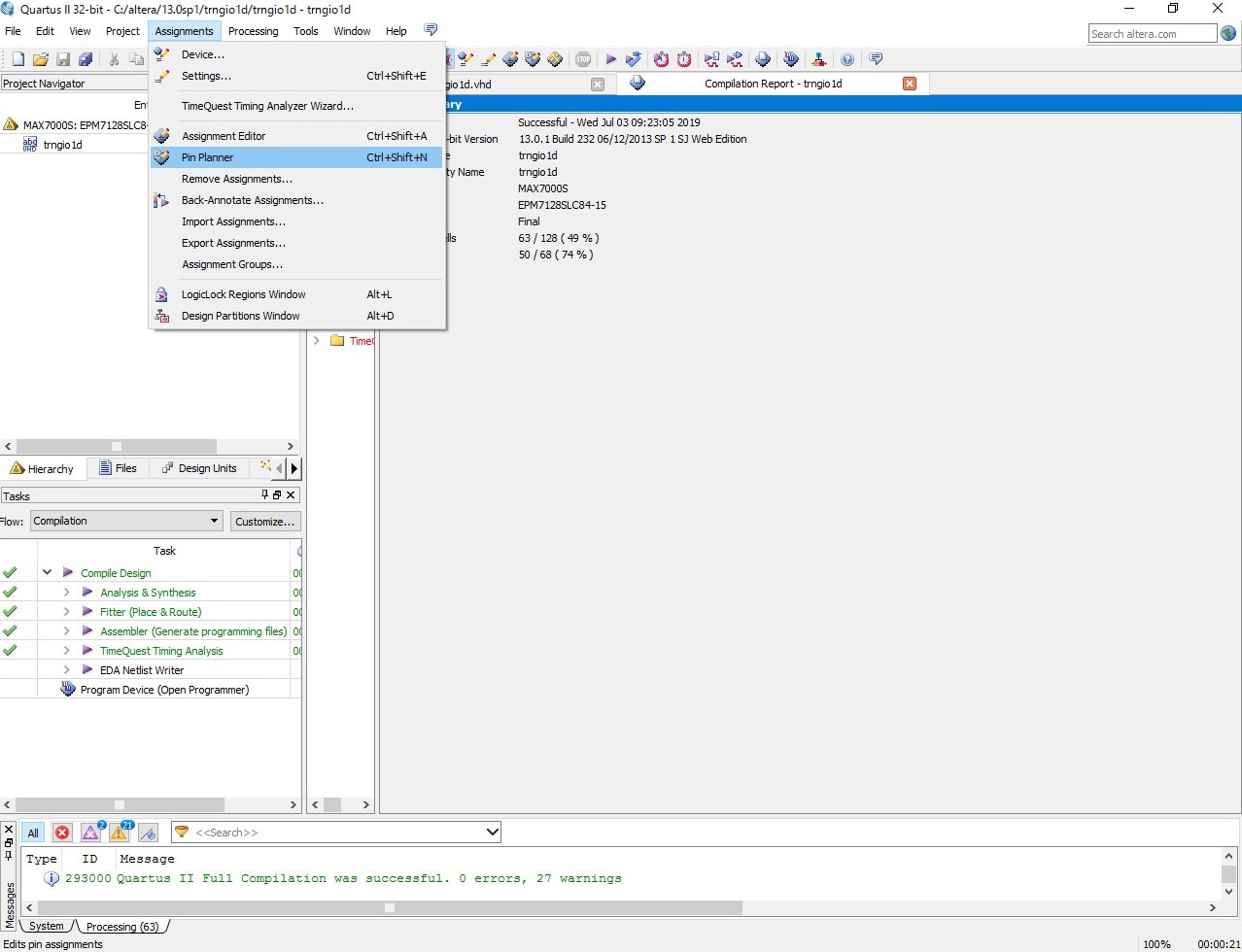

偝偰丄偦傟偱偼俹倝値丂俹倢倎値値倕倰傪婲摦偟傑偡丅

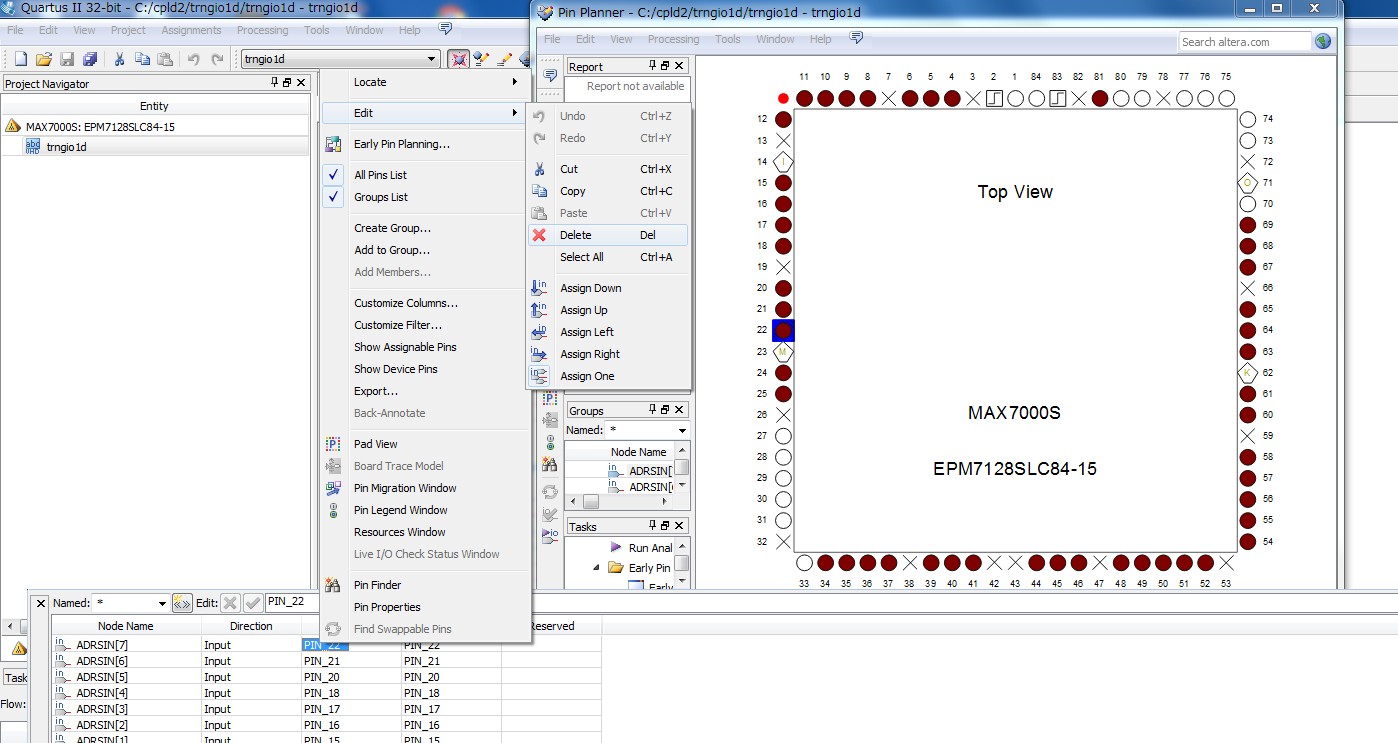

乽俙倱倱倝倗値倣倕値倲倱乿傪僋儕僢僋偟傑偡丅

奐偔儊僯儏乕偺乽俹倝値丂俹倢倎値値倕倰乿傪僋儕僢僋偟傑偡丅

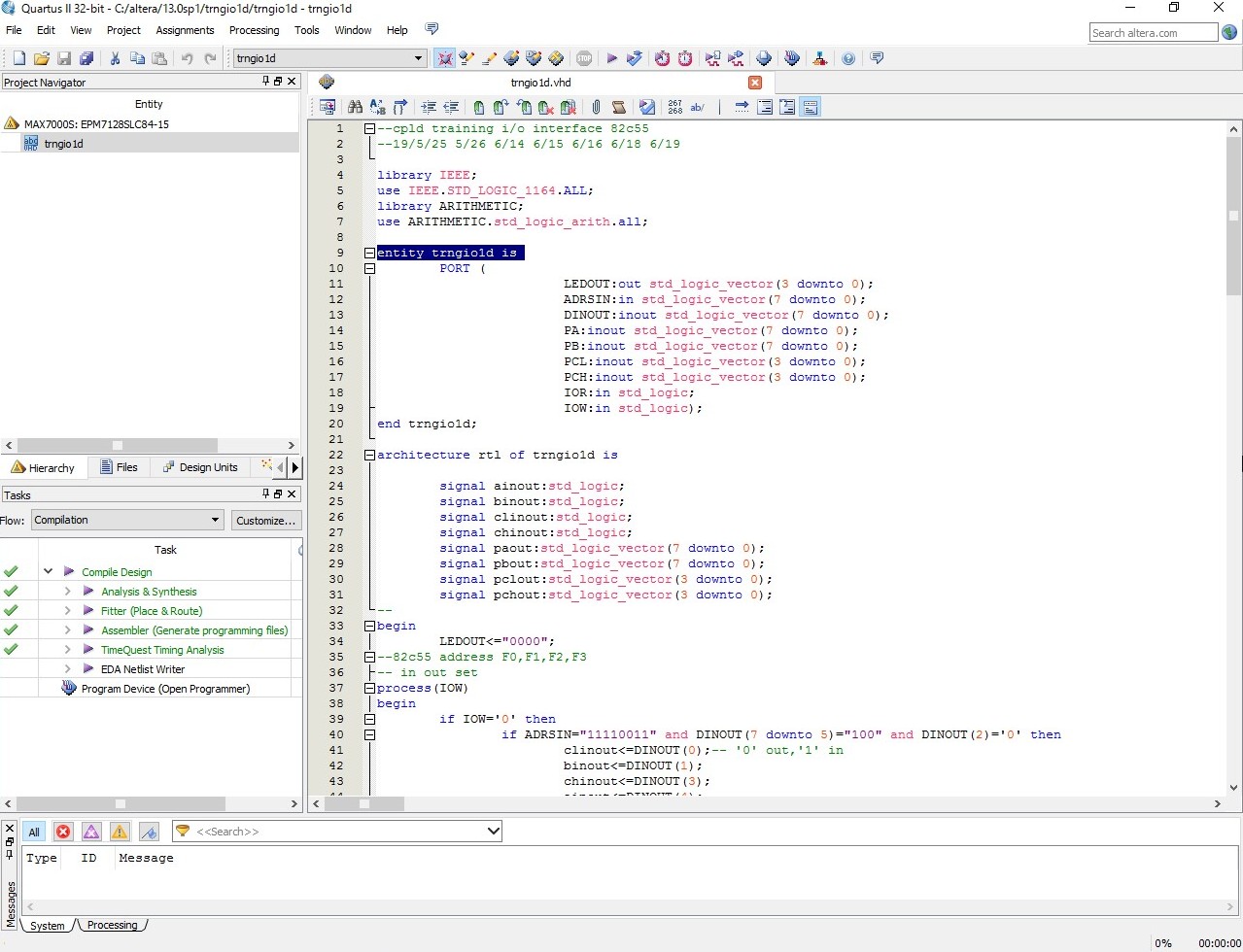

偙偺夋柺偼慜夞偺僐儞僷僀儖廔椆屻偵偦偺傑傑偡偖偵俹倝値丂俹倢倎値値倕倰傪婲摦偟偨偲偒偺夋柺偵側偭偰偄傑偡偑丄崱夞偺愢柧偺傛偆偵僐儞僷僀儖偑廔偭偨偲偙傠偱俻倳倎倰倲倳倱嘦傪廔椆偟偰丄偺偪傎偳嵞傃俻倳倎倰倲倳倱嘦傪婲摦偟偰丄俹倝値丂俹倢倎値値倕倰傪幚峴偡傞偲偄偆偙偲偱傕慡偔巟忈偼偁傝傑偣傫丅

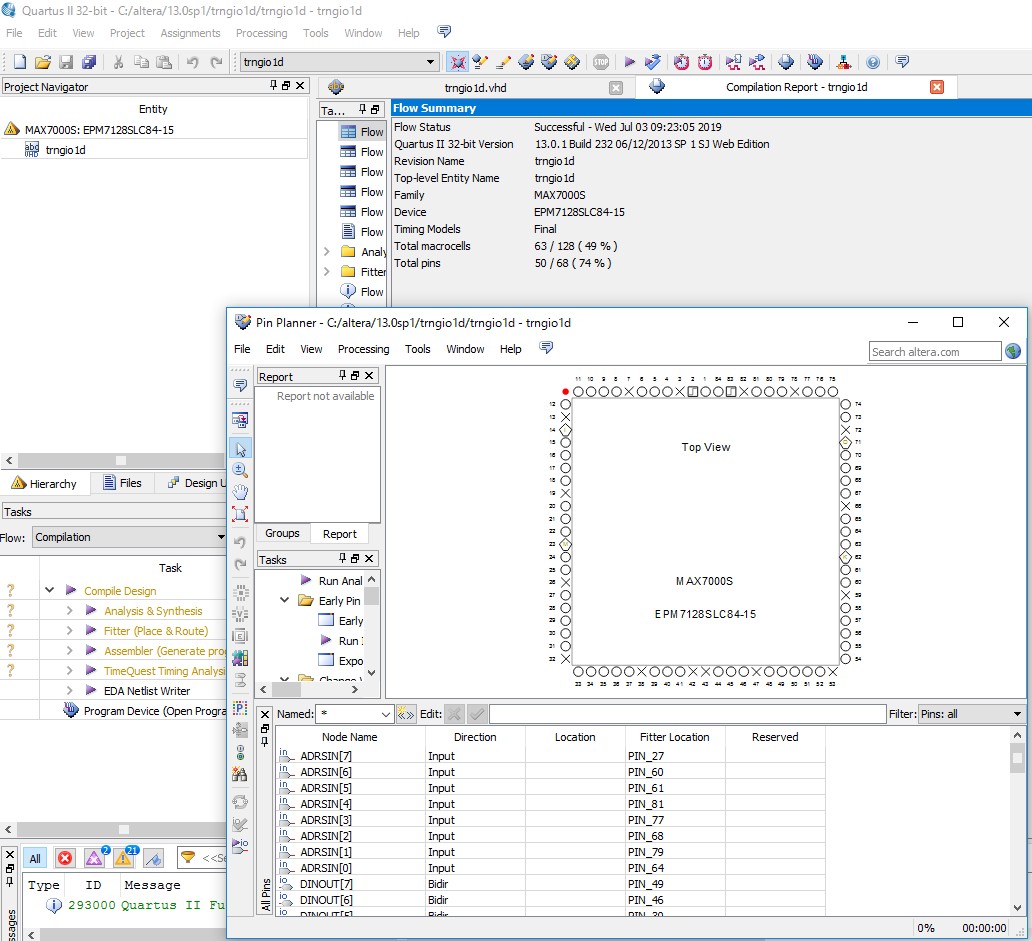

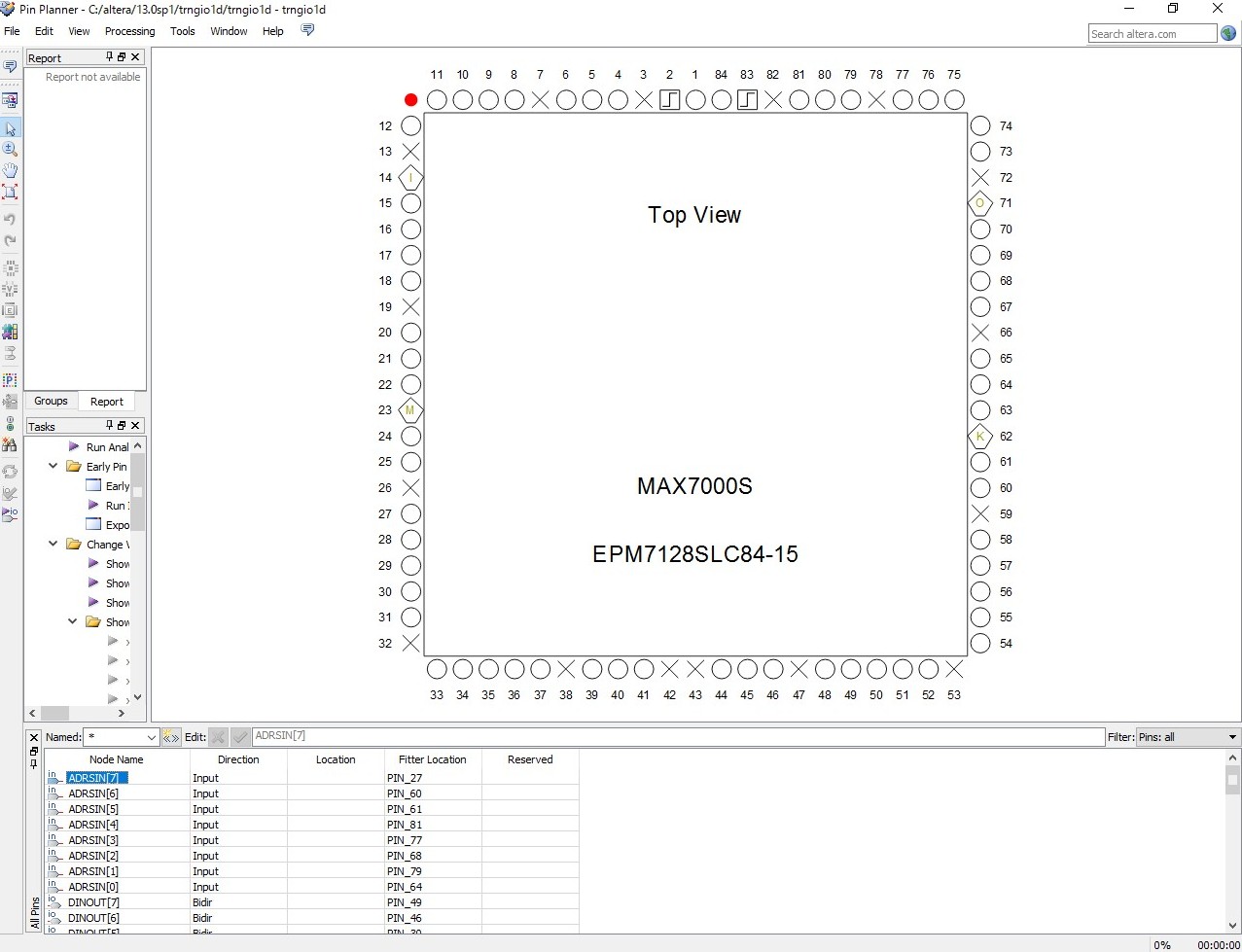

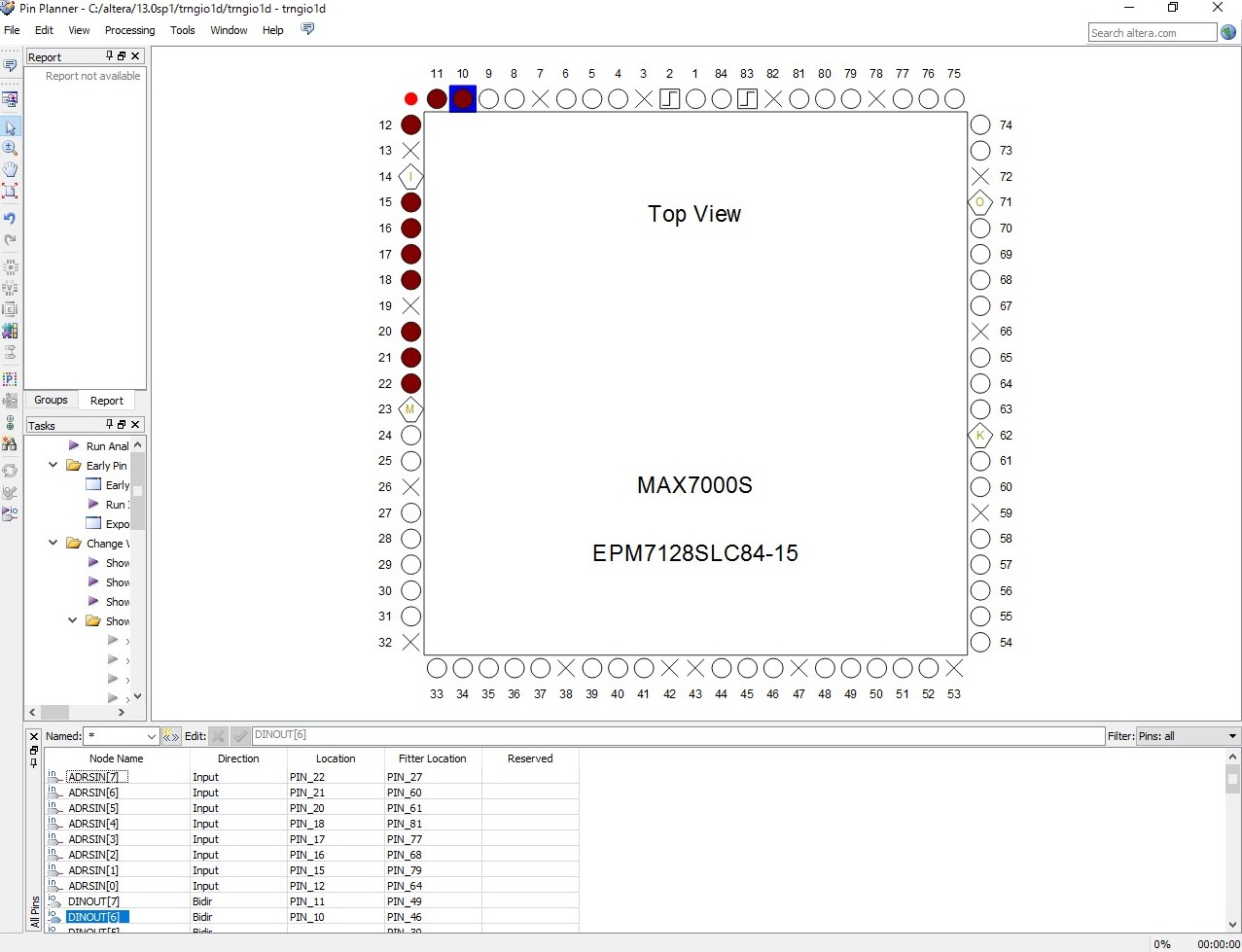

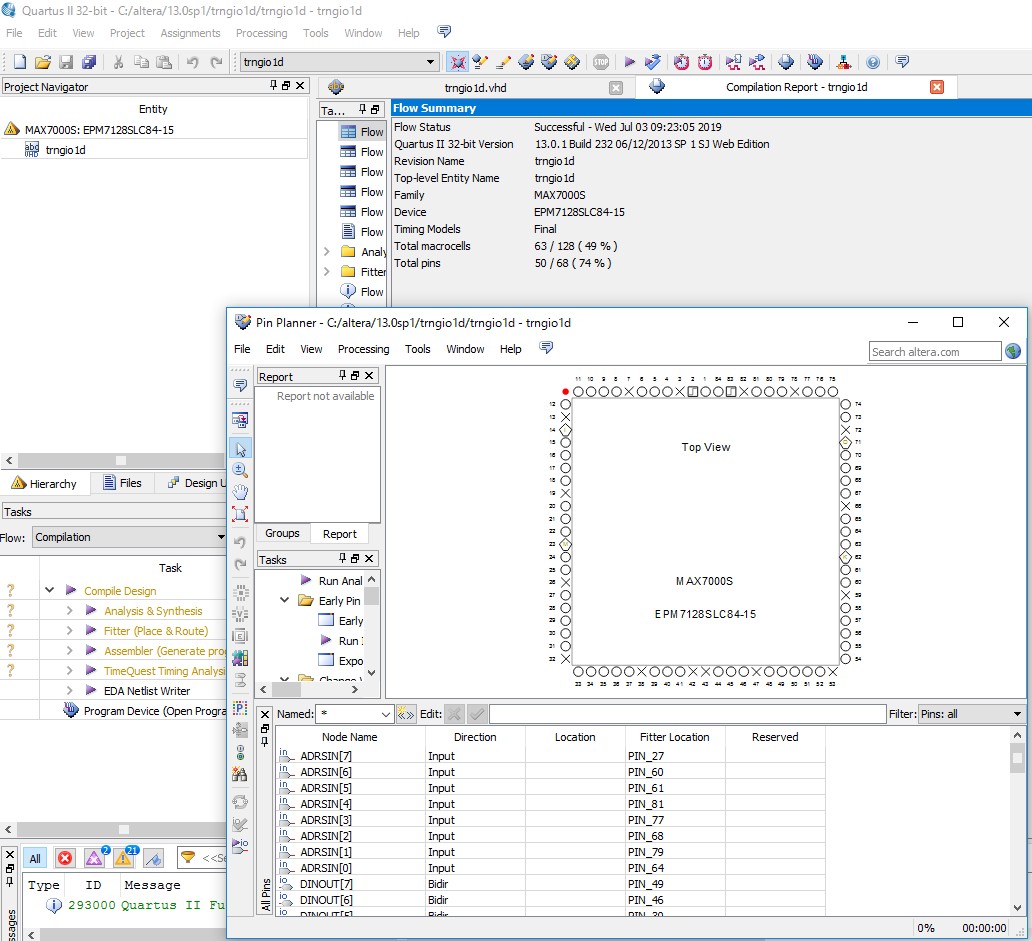

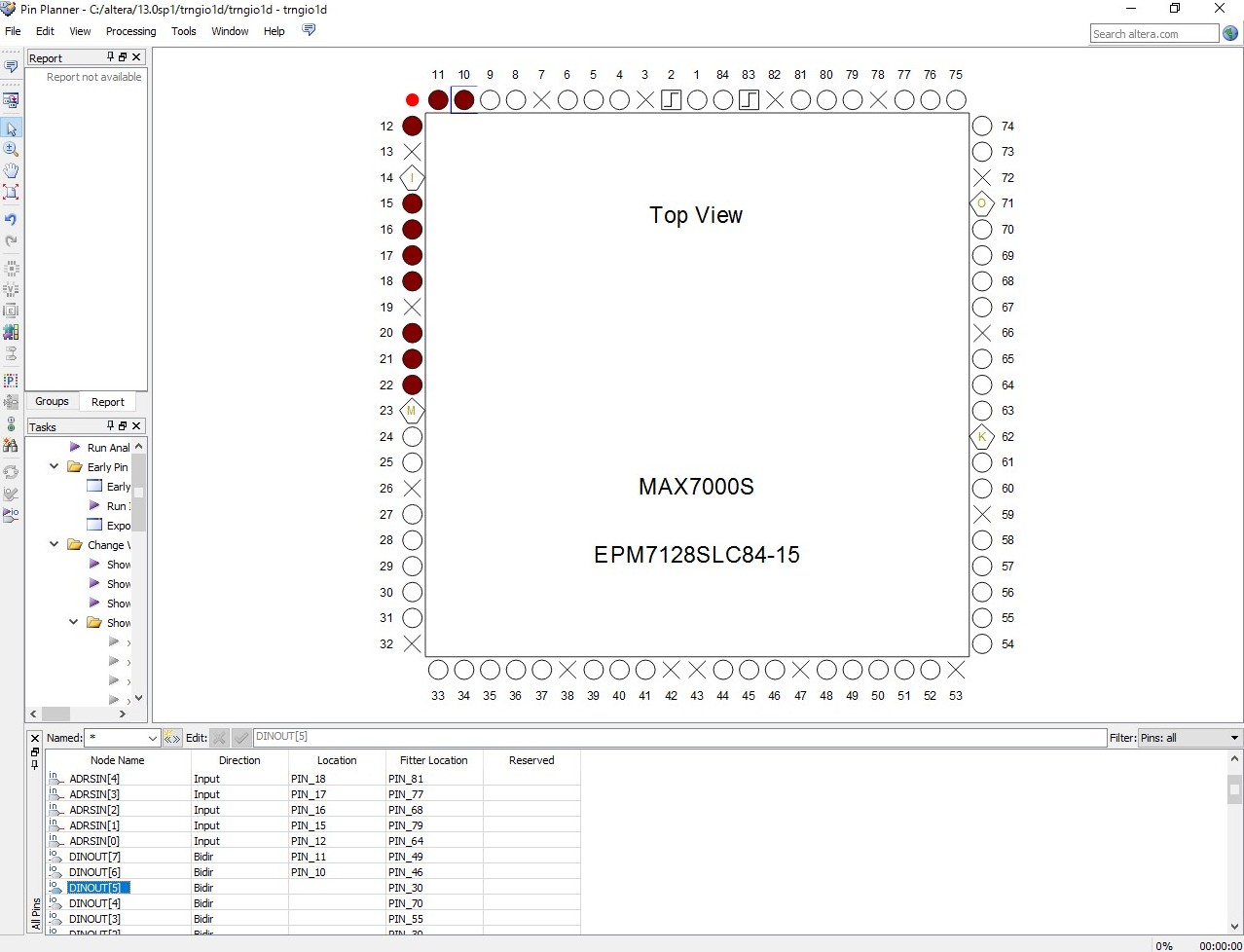

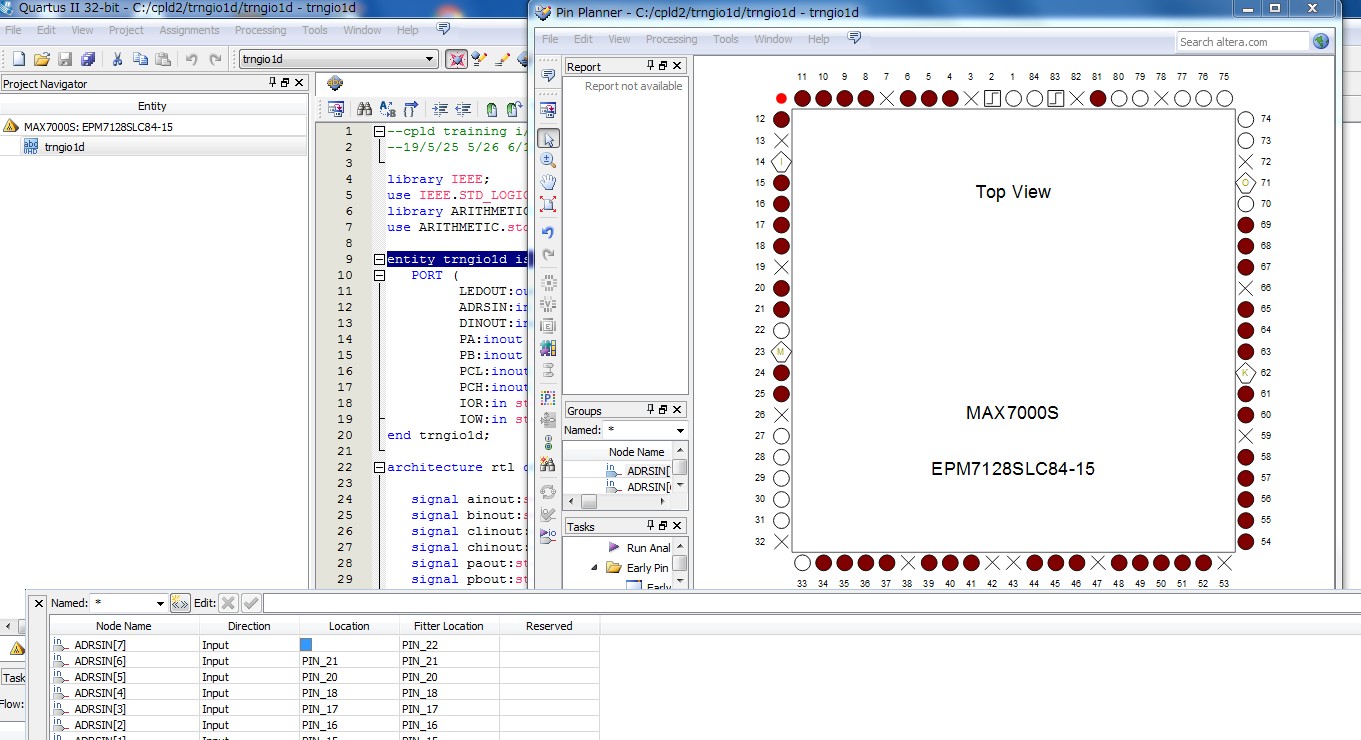

俹倝値丂俹倢倎値値倕倰偑婲摦偟傑偟偨丅

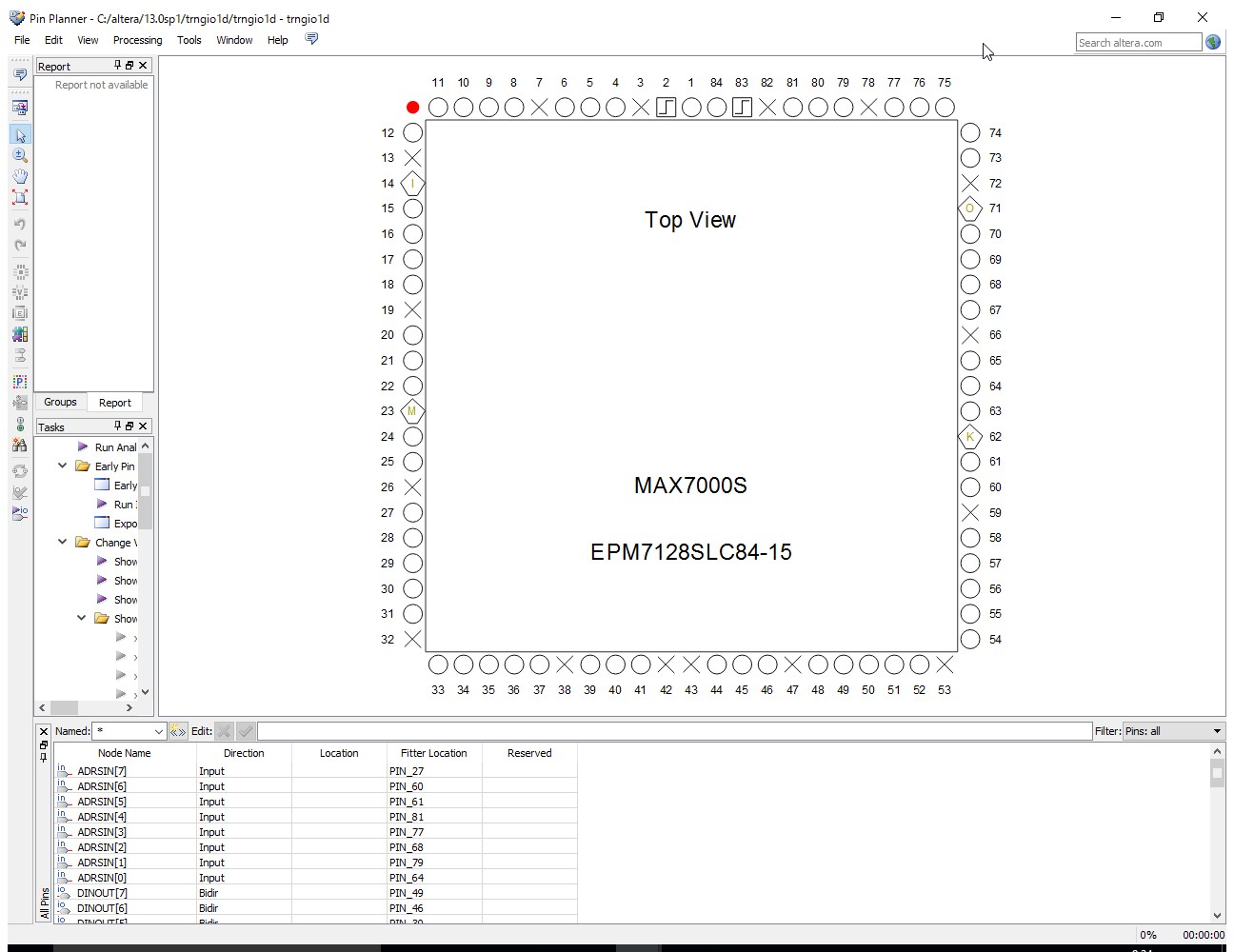

偪傚偭偲昞帵偑彫偝偄偺偱丄塃忋偺乽嵟戝壔乿乮仩儅乕僋乯傪僋儕僢僋偟偰昞帵夋柺傪嵟戝偵偟傑偡丅

夋柺偑戝偒偔側傝傑偟偨丅

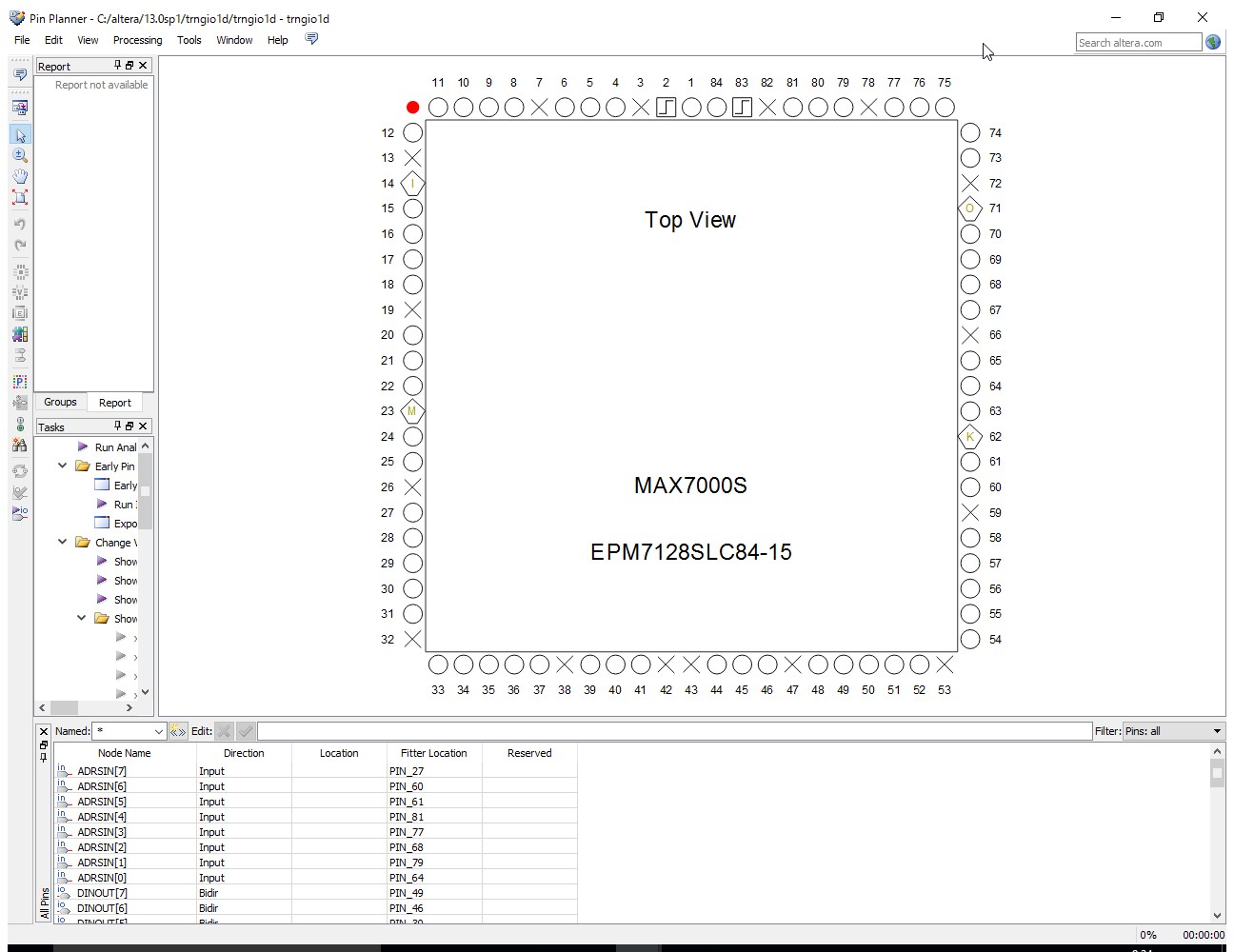

夋柺忋晹偵抂巕柤偲抂巕斣崋傪寢崌偡傞慜偺傑偭偝傜側抂巕恾偑昞帵偝傟傑偡丅

夋柺壓晹偵偼倁俫俢俴僜乕僗僾儘僌儔儉偱掕媊偟偨抂巕柤偺儕僗僩偑昞帵偝傟傑偡丅

榞偑嫹偄偺偱堦晹偟偐昞帵偝傟偰偄傑偣傫丅

塀傟偰偄傞偲偙傠偼僗僋儘乕儖偟偰昞帵偝偣傞偙偲偑偱偒傑偡丅

昞偱偼僐儞僷僀儔偑壖偵揬傝晅偗偨抂巕斣崋偑昞帵偝傟偰偄傑偡偑丄傕偪傠傫偙偺傑傑偱偼巊偊傑偣傫丅

幚嵺偵俹倝値丂俹倢倎値値倕倰偱抂巕柤偲抂巕斣崋傪偮側偖偲嬻敀偵側偭偰偄傞俴倧們倎倲倝倧値偺偲偙傠偵丄妱傝摉偰偨抂巕斣崋偑昞帵偝傟傑偡丅

偲偙傠偱丅

偳偺抂巕柤傪偳偺抂巕斣崋偵妱傝摉偰傞偐偲偄偆偙偲偼丄倁俫俢俴僾儘僌儔儉偑偱偒偁偑傞偲偒傑偱偵寛偭偰偄傞偼偢偱偡丅

怣崋偵傛偭偰偼嬻偄偰偄傞抂巕偵揔摉偵妱傝摉偰偰偟傑偭偰傕傛偄傕偺傕弌偰偔傞偐傕偟傟傑偣傫偑丄晛捠偼僴乕僪夞楬偺攝慄偑寛偭偰偄傑偡偐傜丄傎偲傫偳偺怣崋偼丄偳偺怣崋偑偳偺抂巕偵丄偲偄偆妱傝摉偰偑嵟弶偐傜寛偭偰偄傑偡丅

崱愢柧傪偟偰偍傝傑偡俠俹俴俢僩儗乕僯儞僌儃乕僪偺応崌偱傕丄傎偲傫偳偺怣崋偼偦傟偧傟摿掕偺抂巕斣崋偵妱傝摉偰嵪傒偱偡丅

崱夞偺俉俀俠俆俆僾儘僌儔儉偱巊偆怣崋偺抂巕斣崋傊偺妱傝摉偰昞傪壓偵帵偟傑偡丅

偙偺昞傪尒側偑傜俹倝値丂俹倢倎値値倕倰傪憖嶌偟偰偄偒傑偡丅

幚嵺偺嶌嬈傪巒傔傞慜偵壓偺榞偱埻偭偨晹暘傪僐僺乕偟偰乮儊儌挔偐俿倕倰倎俹倎倓側偳偵揬傝晅偗偰乯僾儕儞僩傾僂僩偟偰偔偩偝偄丅

偦傟傪尒側偑傜嶌嬈偡傞傎偆偑妝偩偲巚偄傑偡丅

set_location_assignment PIN_22 -to ADRSIN[7]

set_location_assignment PIN_21 -to ADRSIN[6]

set_location_assignment PIN_20 -to ADRSIN[5]

set_location_assignment PIN_18 -to ADRSIN[4]

set_location_assignment PIN_17 -to ADRSIN[3]

set_location_assignment PIN_16 -to ADRSIN[2]

set_location_assignment PIN_15 -to ADRSIN[1]

set_location_assignment PIN_12 -to ADRSIN[0]

set_location_assignment PIN_11 -to DINOUT[7]

set_location_assignment PIN_10 -to DINOUT[6]

set_location_assignment PIN_9 -to DINOUT[5]

set_location_assignment PIN_8 -to DINOUT[4]

set_location_assignment PIN_6 -to DINOUT[3]

set_location_assignment PIN_5 -to DINOUT[2]

set_location_assignment PIN_4 -to DINOUT[1]

set_location_assignment PIN_81 -to DINOUT[0]

set_location_assignment PIN_65 -to LEDOUT[3]

set_location_assignment PIN_67 -to LEDOUT[2]

set_location_assignment PIN_68 -to LEDOUT[1]

set_location_assignment PIN_69 -to LEDOUT[0]

set_location_assignment PIN_24 -to IOR

set_location_assignment PIN_25 -to IOW

set_location_assignment PIN_64 -to PA[7]

set_location_assignment PIN_63 -to PA[6]

set_location_assignment PIN_61 -to PA[5]

set_location_assignment PIN_60 -to PA[4]

set_location_assignment PIN_58 -to PA[3]

set_location_assignment PIN_56 -to PA[2]

set_location_assignment PIN_57 -to PA[1]

set_location_assignment PIN_54 -to PA[0]

set_location_assignment PIN_55 -to PB[7]

set_location_assignment PIN_52 -to PB[6]

set_location_assignment PIN_51 -to PB[5]

set_location_assignment PIN_50 -to PB[4]

set_location_assignment PIN_49 -to PB[3]

set_location_assignment PIN_48 -to PB[2]

set_location_assignment PIN_46 -to PB[1]

set_location_assignment PIN_45 -to PB[0]

set_location_assignment PIN_34 -to PCH[3]

set_location_assignment PIN_35 -to PCH[2]

set_location_assignment PIN_36 -to PCH[1]

set_location_assignment PIN_37 -to PCH[0]

set_location_assignment PIN_40 -to PCL[3]

set_location_assignment PIN_39 -to PCL[2]

set_location_assignment PIN_41 -to PCL[1]

set_location_assignment PIN_44 -to PCL[0]

|

偙偺昞偼幚嵺偺嶌嬈偺岦偒偲偼媡偺彂偒曽偵側偭偰偄傑偡丅

堦斣忋偺乽俹俬俶丵俀俀丂亅倲倧丂俙俢俼俽俬俶乵俈乶乿偼

乽俙俢俼俽俬俶乵俈乶偼俹俬俶丵俀俀偵妱傝摉偰傞乿

偲偄偆傛偆偵撉傫偱偔偩偝偄丅

偦傟偱偼昞傪尒側偑傜幚嵺偺嶌嬈傪奐巒偟傑偡丅

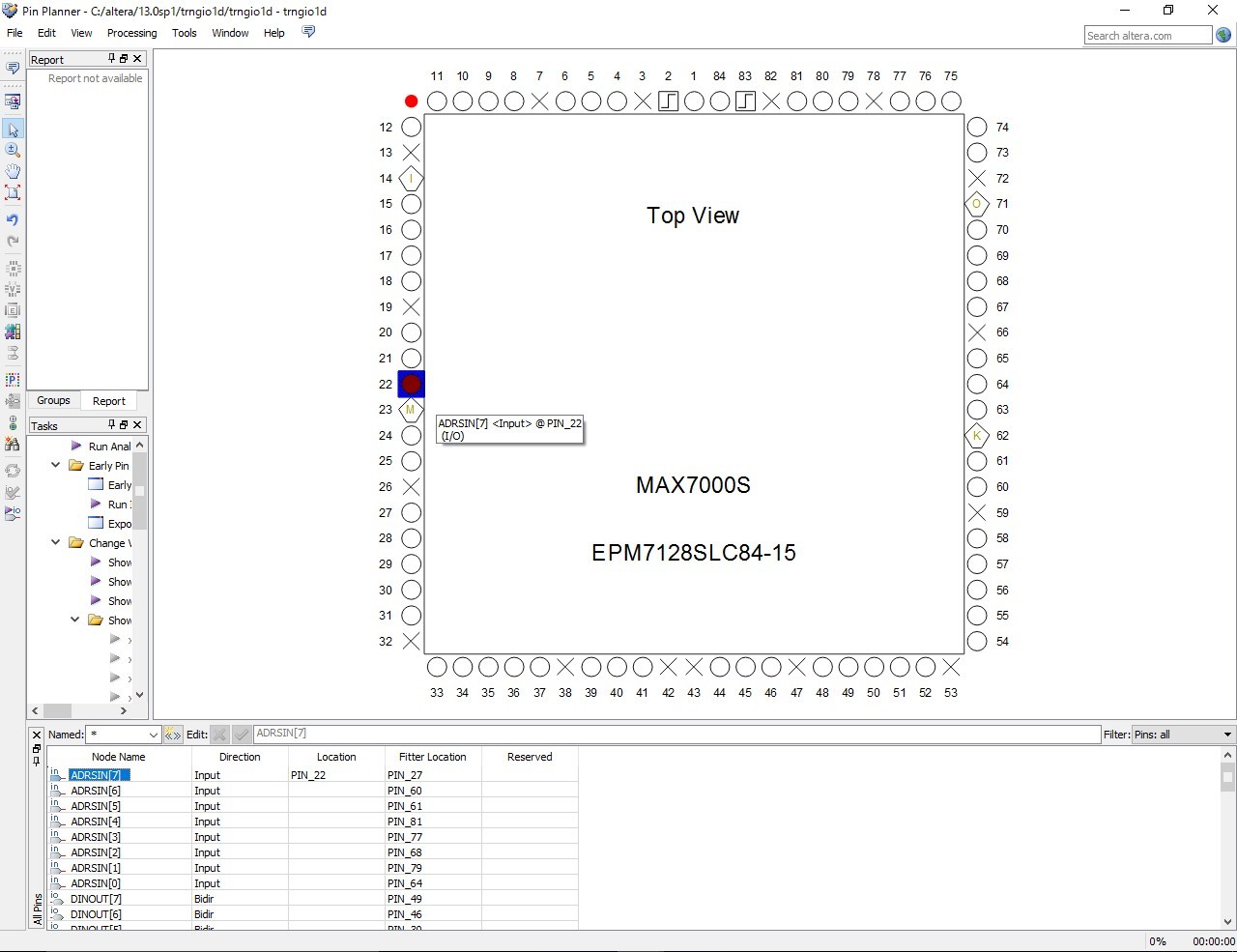

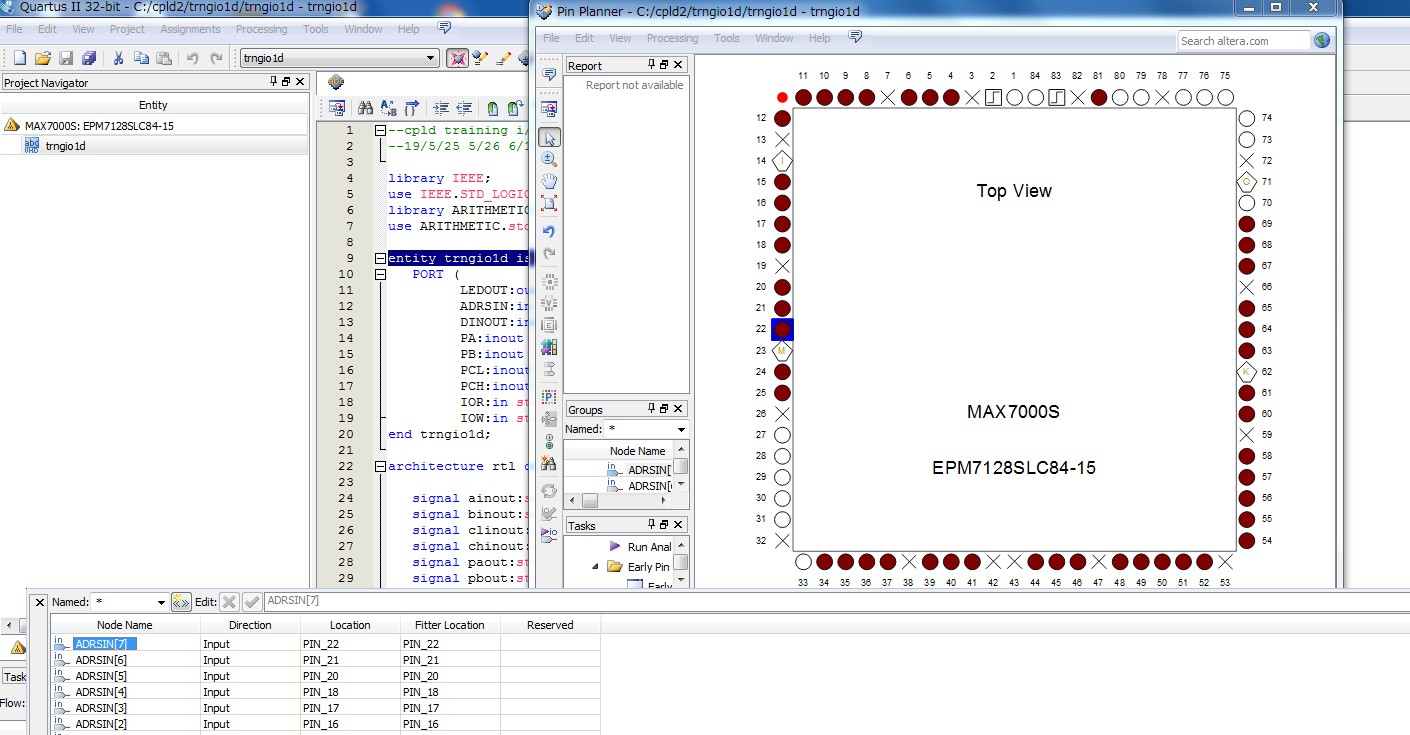

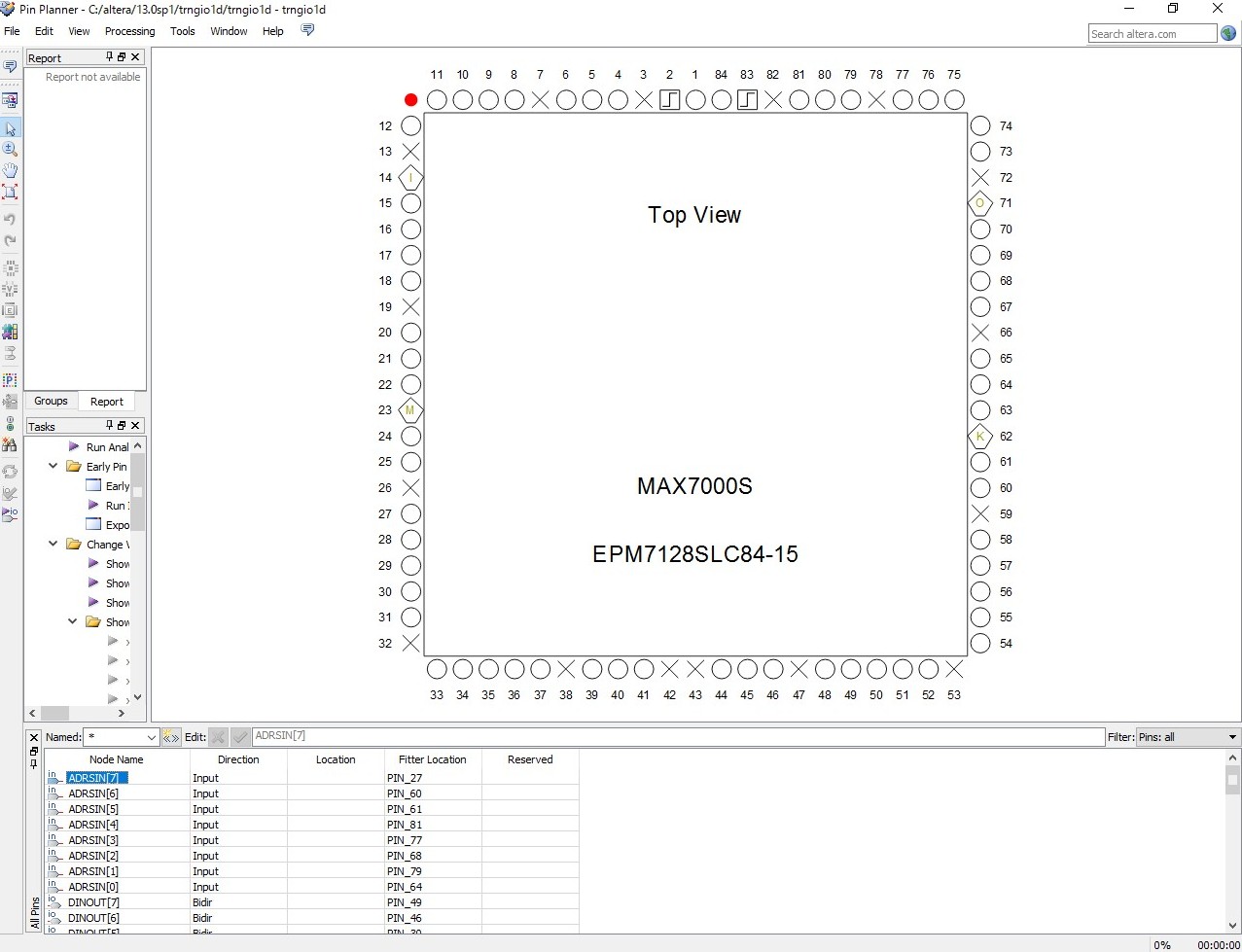

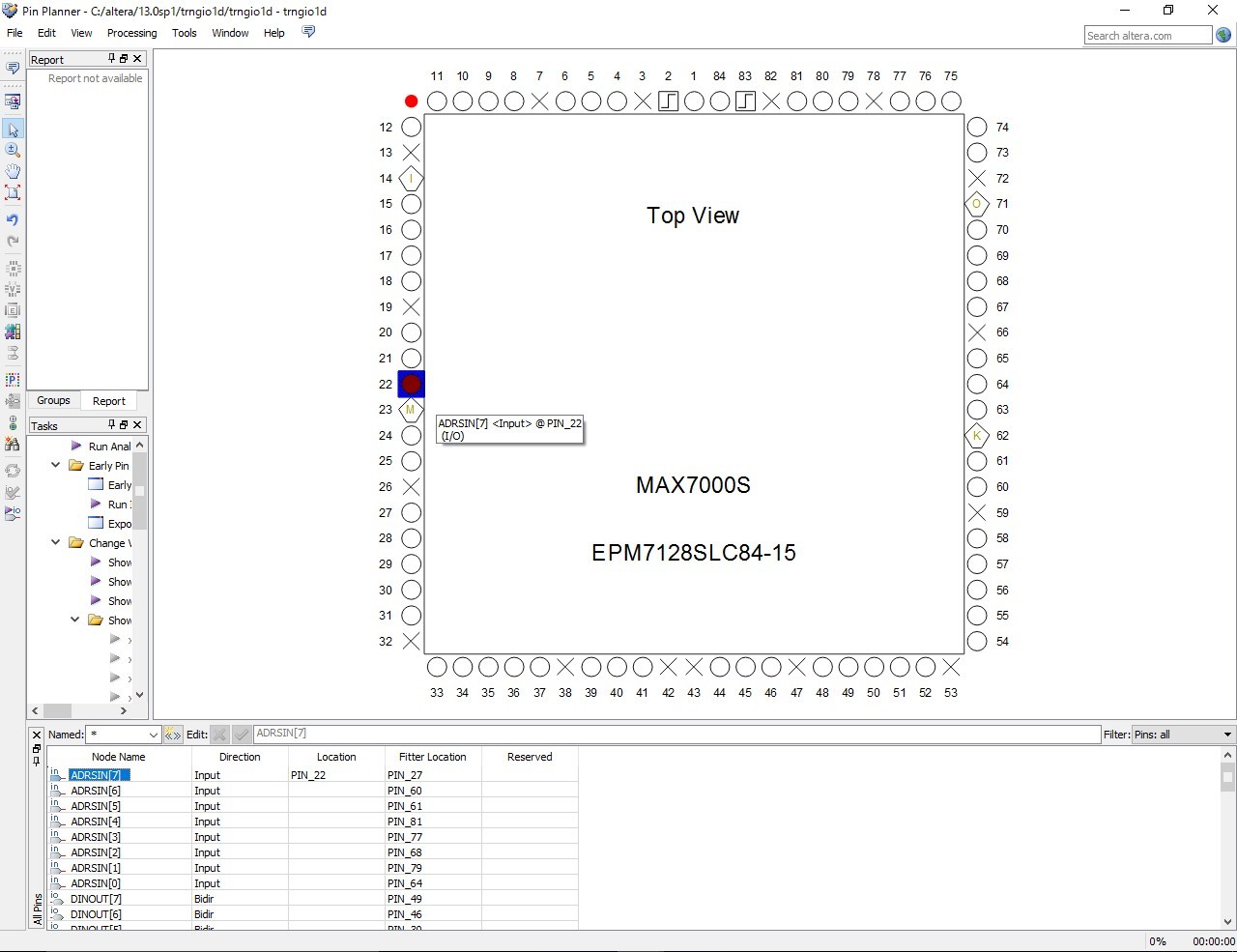

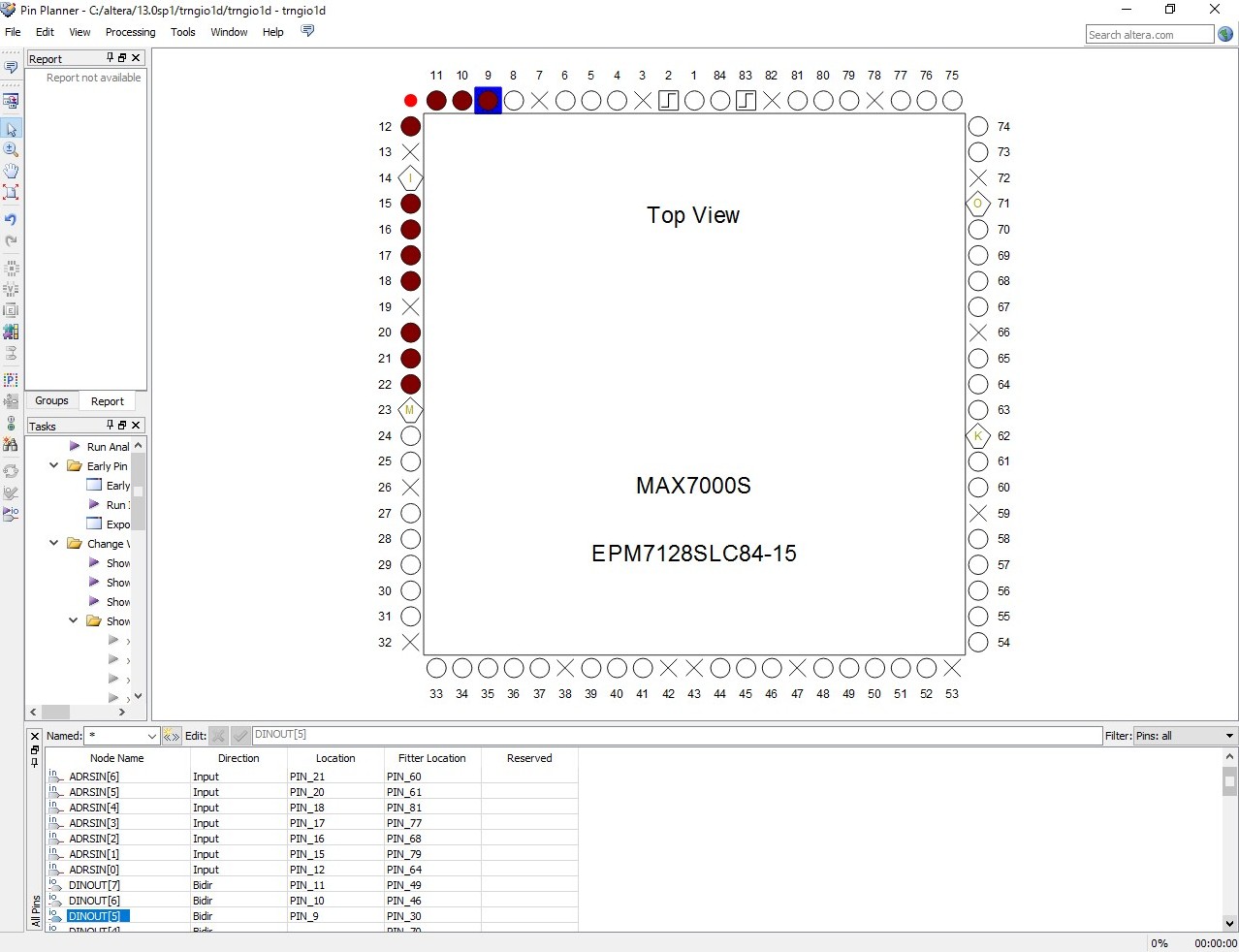

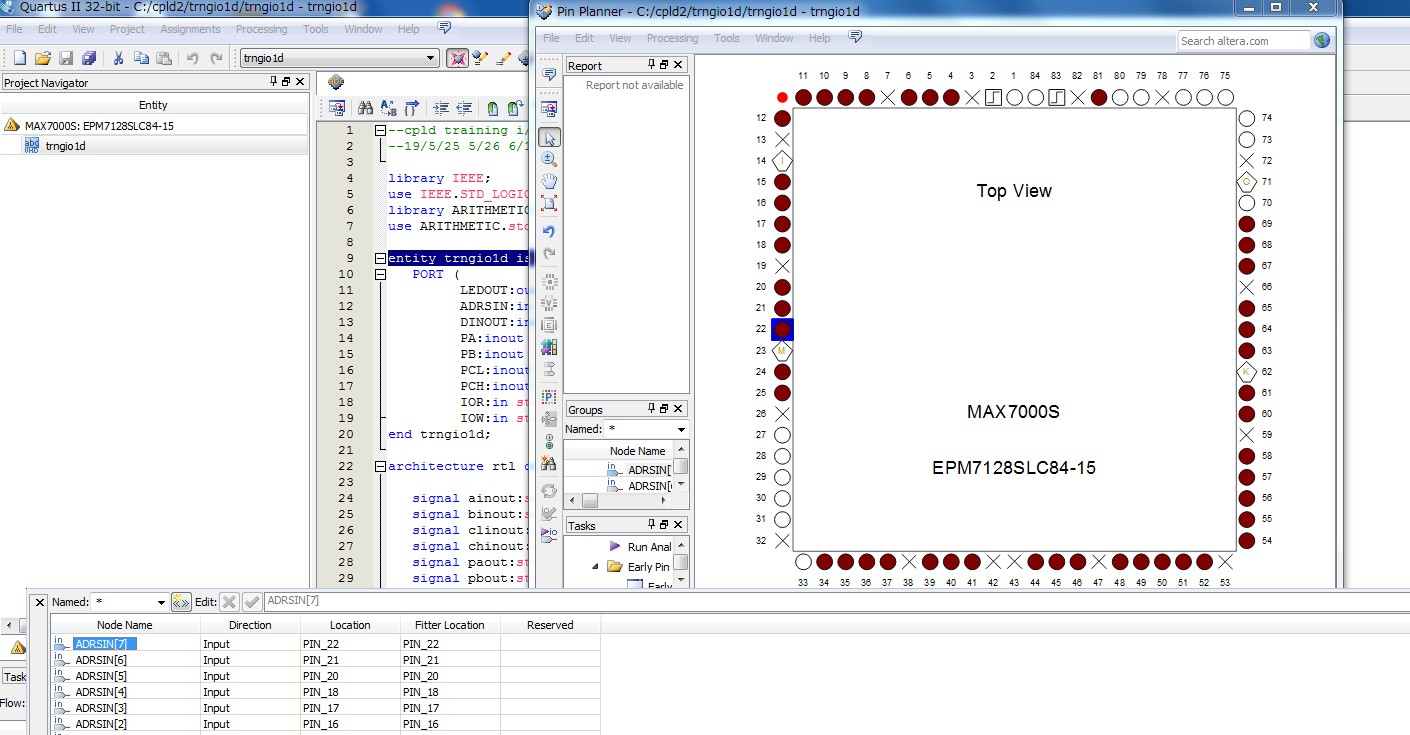

夋柺壓晹偵昞帵偝傟偰偄傞儕僗僩偺堦斣忋偺乽俙俢俼俽俬俶乵俈乶乿傪儅僂僗偱慖戰偟偰丄偦偺傑傑夋柺忋晹偺抂巕恾偺偲偙傠傑偱僪儔僢僌偟偰偄偒傑偡丅

抂巕斣崋俀俀偺仜偺偲偙傠傑偱僪儔僢僌偟偰偄偭偰丄偦偙偱棧偡偲俙俢俼俽俬俶乵俈乶偑俹俬俶俀俀偵揬傝晅偗傜傟偰仜偑擹偄愒怓偵拝怓偝傟傑偡丅

壓偺儕僗僩偺俴倧們倎倲倝倧値偺偲偙傠偵傕俹俬俶丵俀俀偑昞帵偝傟傑偟偨丅

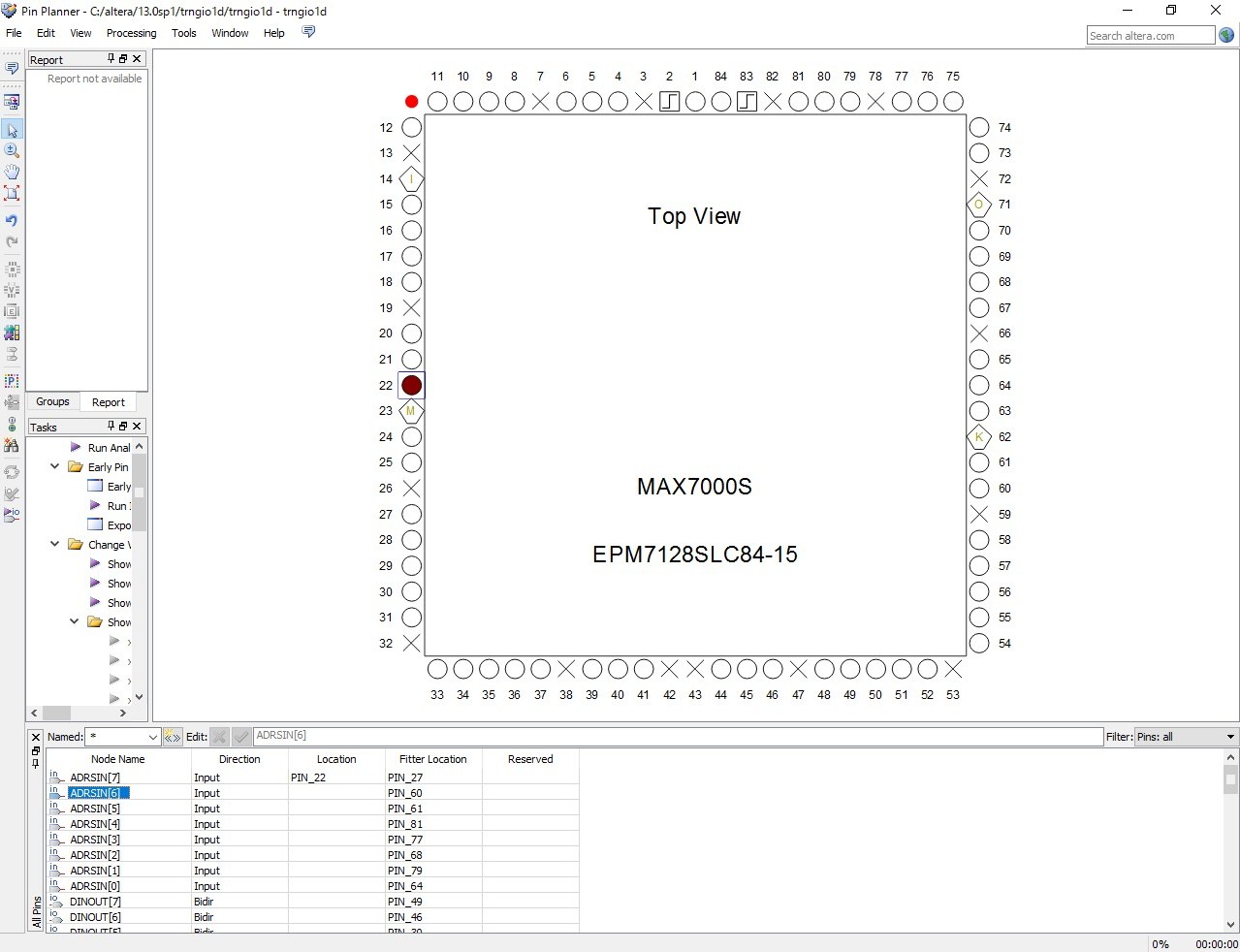

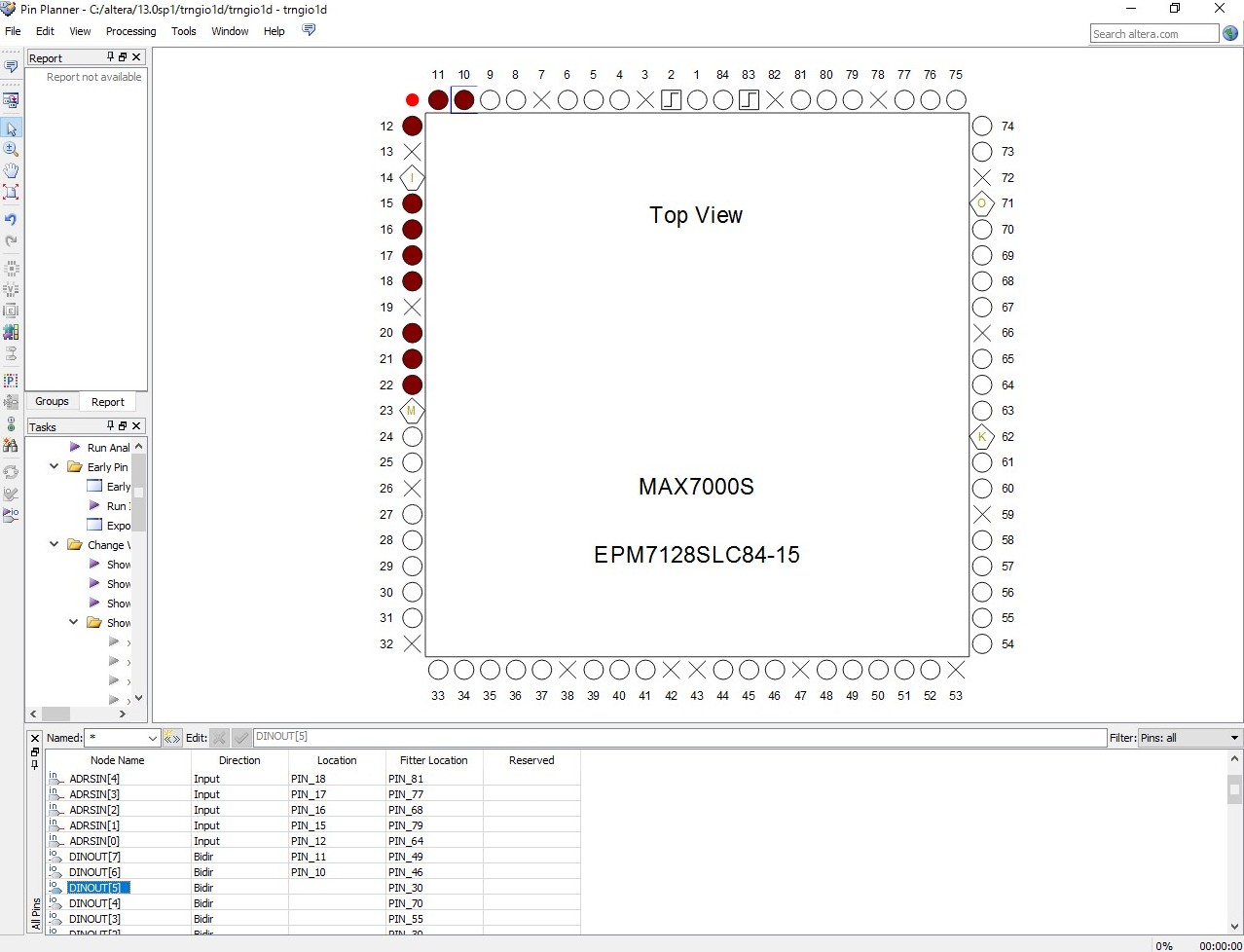

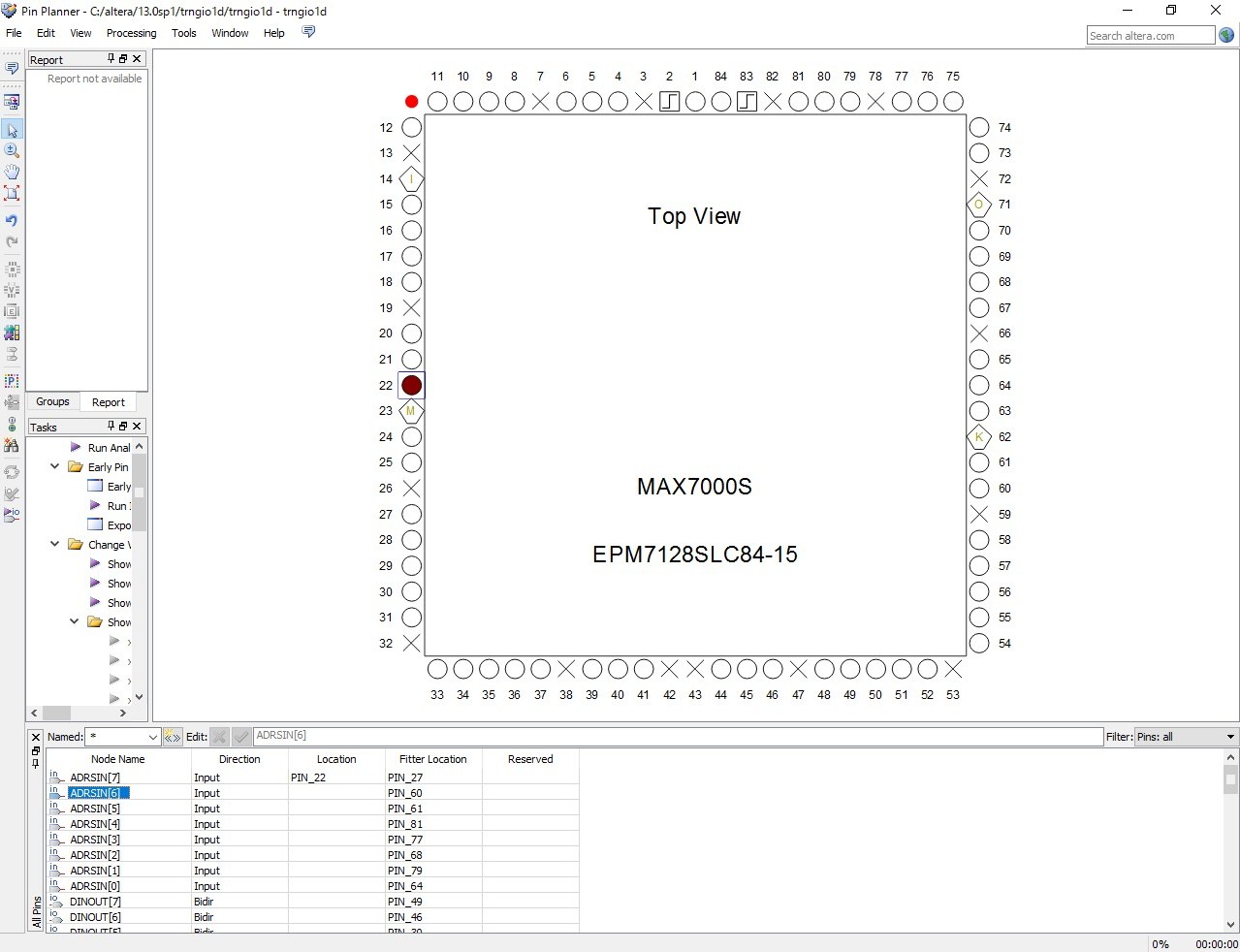

師偼俙俢俼俽俬俶乵俇乶偱偡丅

嶌嬈偼忋偐傜弴偵偟側偗傟偽側傜側偄丄偲偄偆偙偲偼偁傝傑偣傫丅

搑拞偱偆偭偐傝旘偽偟偰偟傑偭偨傝偟偨偲偒偼丄偦偺旘偽偟偨偲偙傠傑偱峴偭偰丄偦偺抂巕偵偮偄偰偺嶌嬈傪偡傞偙偲偑偱偒傑偡丅

娫堘偭偰暿偺抂巕斣崋偵揬傝晅偗偰偟傑偭偨応崌傕丄傢偞傢偞庢傝徚偝側偔偰傕丄峔傢偢偵偦偺偁偲偱惓偟偄抂巕斣崋偺偲偙傠偵僪儔僢僌偟偰偄偭偰揬傝晅偗傟偽丄惓偟偄寢壥偵捈偝傟傑偡丅

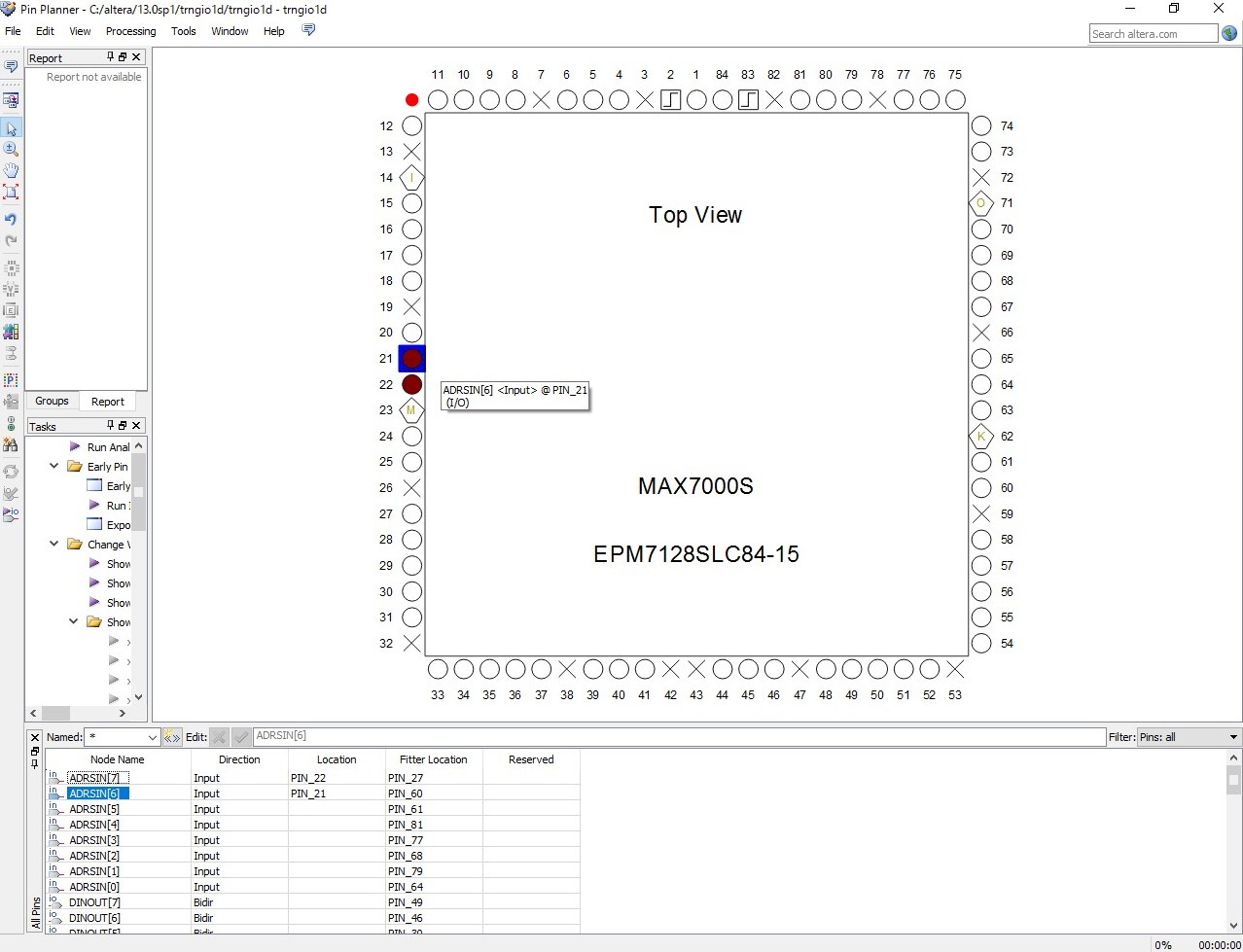

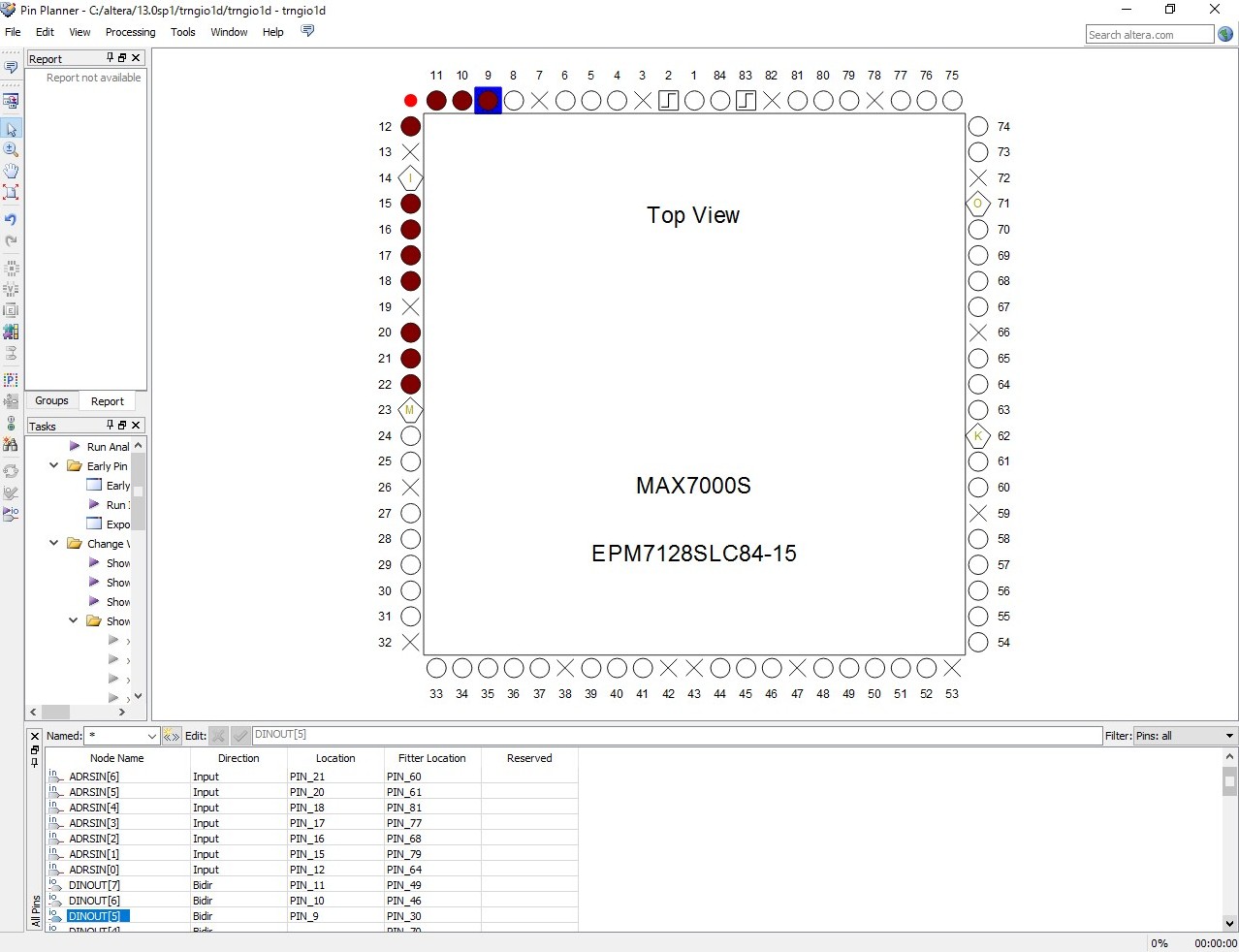

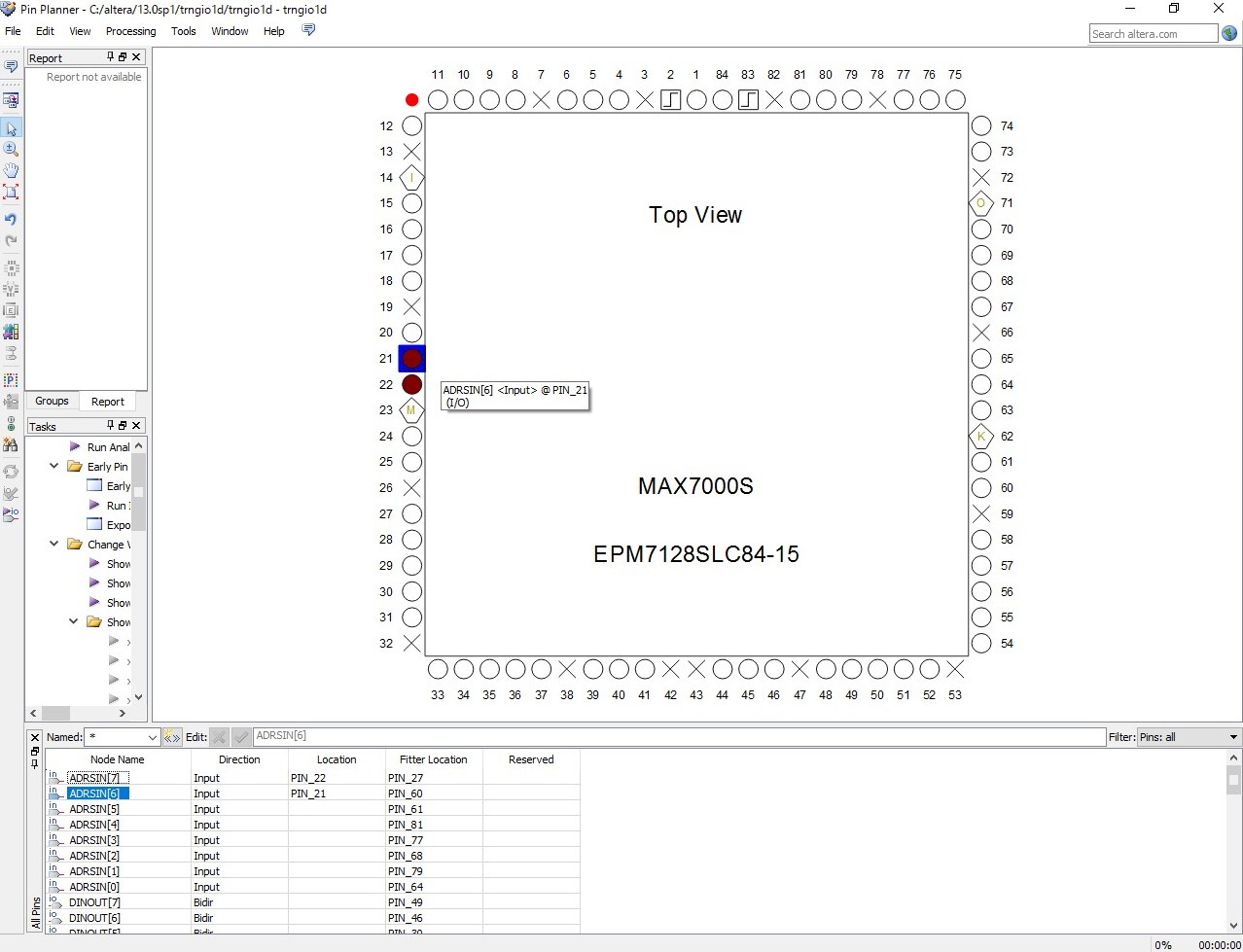

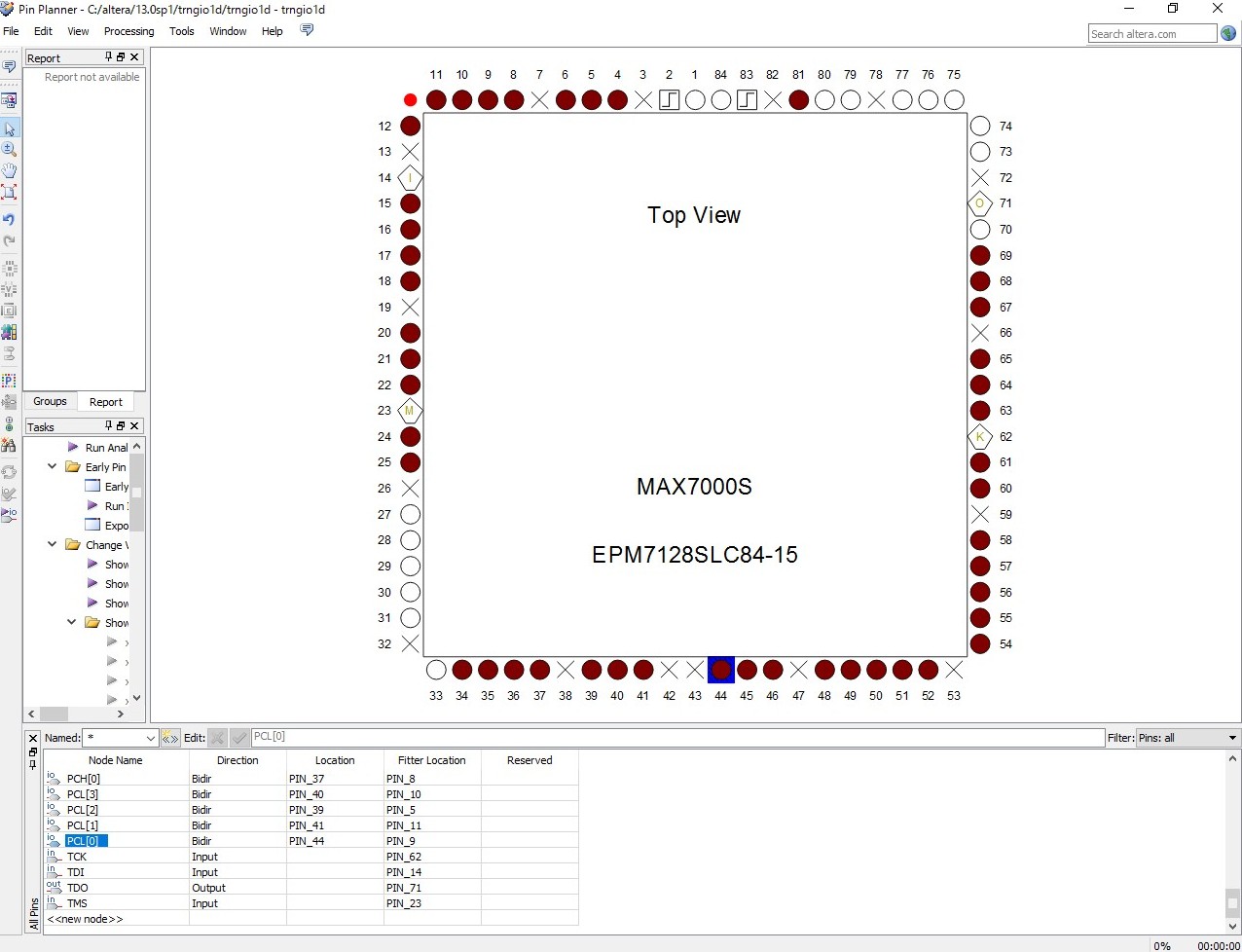

摨偠憖嶌傪峴側偭偰丄俙俢俼俽俬俶乵俇乶偑俹俬俶丵俀侾偵揬傝晅偗傜傟傑偟偨丅

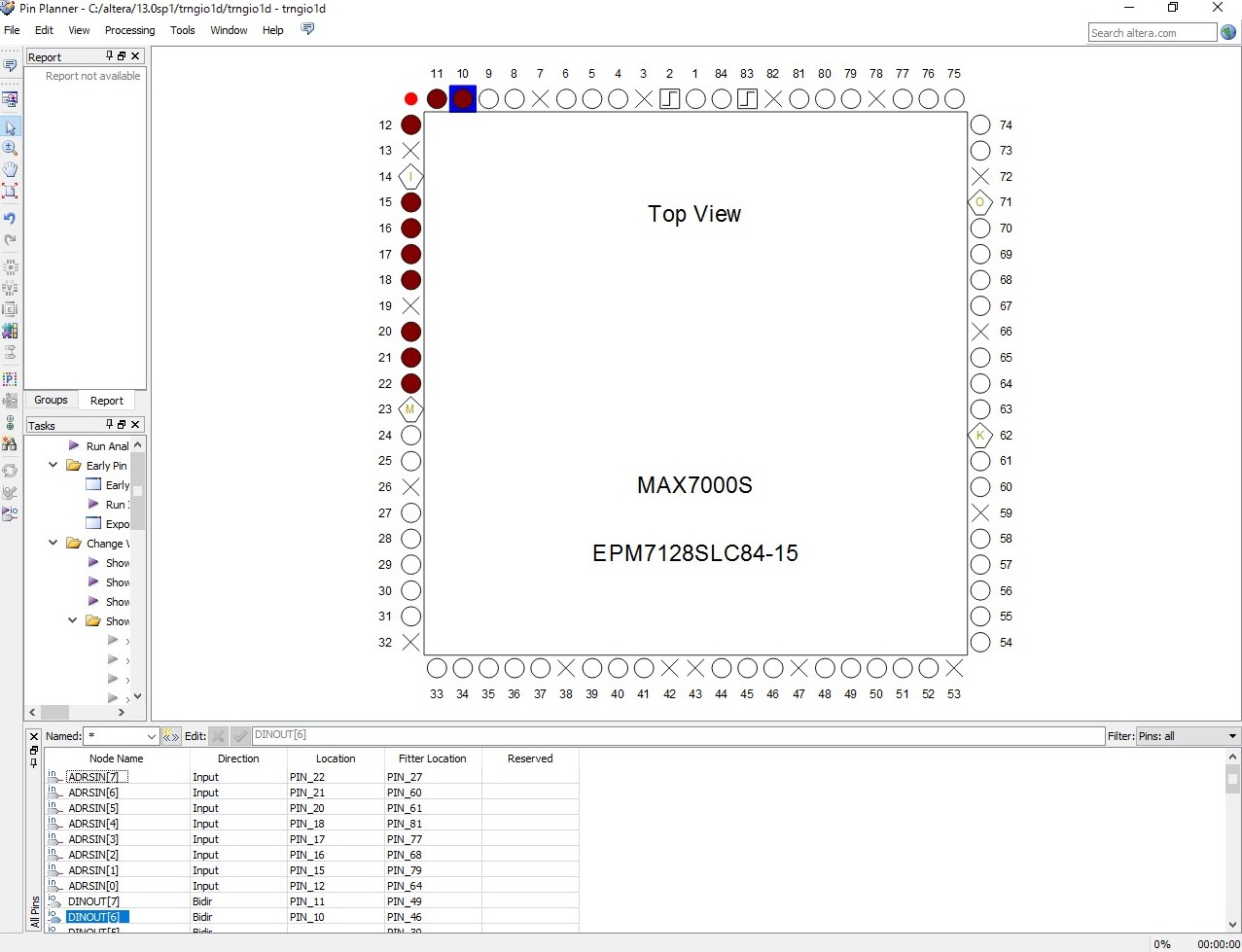

偦偺傛偆偵偟偰俢俬俶俷倀俿乵俇乶傑偱揬傝晅偗傑偟偨丅

儕僗僩偺壓偵塀傟偰偄傞偲偙傠偼塃偺僗僋儘乕儖僶乕傪憖嶌偟偰昞帵偝偣傞偙偲偑偱偒傑偡丅

俢俬俶俷倀俿乵俆乶傪俹俬俶丵俋偵妱傝摉偰傑偟偨丅

儕僗僩偺昞帵偼妱傝摉偰偑姰椆偟偨偲偙傠傑偱栠偭偰偟傑偄傑偡丅

偆乕傫丅

偣傔偰偦偺壓偺堦峴偩偗偱傕偟偭偐傝昞帵偟偰偔傟傞偲妝側偺偱偡偗傟偳乮敿暘偟偐昞帵偟偰偔傟傑偣傫乯丅

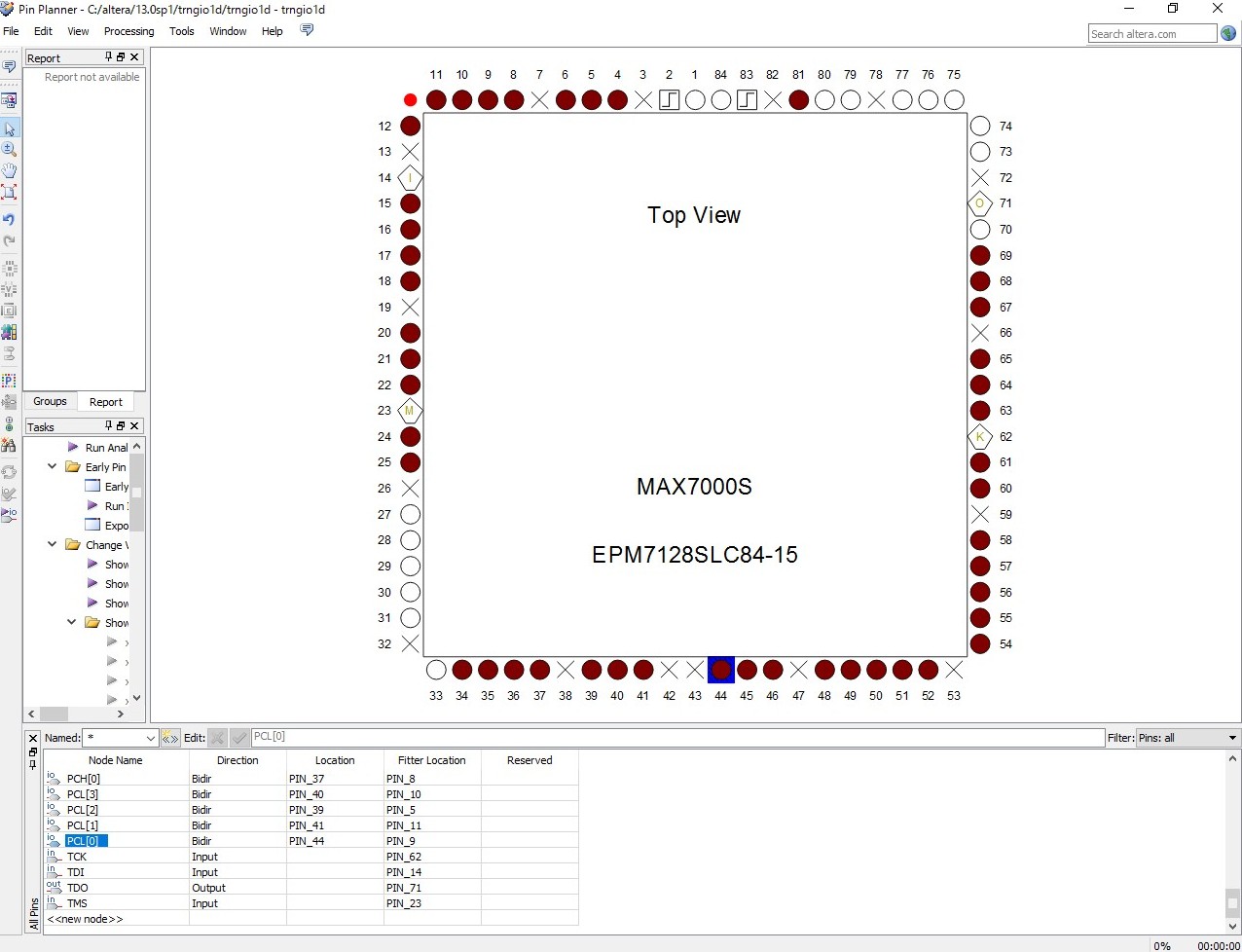

嵟屻傑偱妱傝摉偰偑嵪傒傑偟偨丅

堦斣壓偵昞帵偝傟偰偄傞俿俠俲乣俿俵俽偼俰俿俙俧抂巕側偺偱丄偙偺傑傑偵偟偰偍偒傑偡丅

俰俿俙俧抂巕偼抂巕恾偱偼屲妏宍偱昞帵偝傟偰偄傑偡丅

側偍揹尮抂巕偼倃報偵側偭偰偄傑偡乮倁俢俢丄俧俼俢偺暿偼恾帵偝傟傑偣傫乯丅

枹妱傝摉偰偺抂巕偼仜偺傑傑巆傝傑偡丅

夞楬偑枹攝慄偺傑傑偺忬懺偱丄仜偺傑傑巆偡偲偦偙偐傜僲僀僘偑擖偭偰岆摦嶌偺尨場偵側傝傑偡偐傜傛偔偁傝傑偣傫丅

俠俹俴俢僩儗乕僯儞僌儃乕僪偺夞楬偱偼仜偺抂巕偼俉俀俠俆俆夞楬偲偟偰偼巊偄傑偣傫偑丄偡傋偰僾儖傾僢僾偟偰偁傝傑偡偐傜丄偙偺傑傑巆偟偰偍偄偰傕巟忈偼偁傝傑偣傫丅

儕僗僩傪傕偆堦搙傛偔尒偰丄俴倧們倎倲倝倧値偑嬻敀偵側偭偨傑傑偺偲偙傠偑側偄偐偳偆偐妋擣偟偰偔偩偝偄丅

傑偨擮偺偨傔忋偱僾儕儞僩偟偨妱摉昞偲徠崌偟偰娫堘偭偰偄側偄偐偳偆偐妋擣偟偰偔偩偝偄丅

娫堘偄傪敪尒偟偨偲偒偺捈偟曽偱偡丅

偁傞抂巕柤傪娫堘偭偨抂巕斣崋偵揬傝晅偗偰偟傑偭偰偄偨偙偲偑傢偐偭偨偲偒丄偨傑偨傑惓偟偄妱傝摉偰傪峴側偆抂巕偑仜偵側偭偰偄偨傜丄偦偺抂巕柤傪惓偟偄抂巕偺仜偺偲偙傠傑偱僪儔僢僌偟偰偄偭偰丄偦偙偱棧偣偽惓偟偄仜偑拝怓偝傟偰丄戙傢傝偵娫堘偭偰偄偨抂巕偺偲偙傠偑仜偵曄傢傝傑偡丅

惓偟偄抂巕斣崋偺偲偙傠偑偡偱偵暿偺抂巕柤偵妱傝摉偰傜傟偰仜偑拝怓偝傟偰偄偨応崌乮偙偺応崌偵偼偦偙偵妱傝摉偰傜傟偰偄傞抂巕柤傕娫堘偭偰妱傝摉偰傜傟偰偄傞偼偢偱偡乯丄愭偵偦偺拝怓偝傟偰偄傞抂巕傪仜偵偟側偗傟偽側傝傑偣傫丅

偨傑偨傑愭偵娫堘偭偰妱傝摉偰偰偄偨抂巕柤偺惓偟偄妱摉愭偑仜側傜偽丄愭偵偦偺抂巕柤偺妱傝摉偰傪偟捈偡偙偲偱弴師嬻偒抂巕偺忬懺偵偡傞偙偲偑偱偒傑偡偐傜丄摨偠梫椞偱弴師捈偟偰偄偔偙偲偑偱偒傑偡丅

栤戣偼抂巕柤俙偲抂巕柤俛偑偦傟偧傟憡庤偺抂巕斣崋偺偲偙傠偵妱傝摉偰傜傟偰偟傑偭偰偄偨応崌偱偡丅

偙偺応崌偵偼偳偪傜偐傪愭偵庢傝徚偝側偗傟偽嶌嬈偑偱偒傑偣傫丅

娙曋側曽朄偲偟偰偼丄傕偲傕偲嬻偄偰偄傞仜偵堦扷抂巕柤俙偐俛傪堏摦偟偰偍偄偰丄巆偭偨傎偆偺抂巕柤傪惓偟偄抂巕偵揬傝晅偗偨偁偲丄壖偵堏摦偟偰偍偄偨抂巕柤傪惓偟偄抂巕偵揬傝晅偗傞偲偄偆曽朄偑偁傝傑偡丅

惓峌朄偲偟偰偼堦扷娫堘偭偰揬傝晅偗偰偟傑偭偨抂巕偺妱傝摉偰傪嶍彍偟傑偡丅

憖嶌椺偲偟偰嵟弶偵俙俢俼俽俬俶乵俈乶傪俹俬俶丵俀俀偵寢傃晅偗傑偟偨偑偦傟偑娫堘偭偰偄偨偲偟傑偡丅

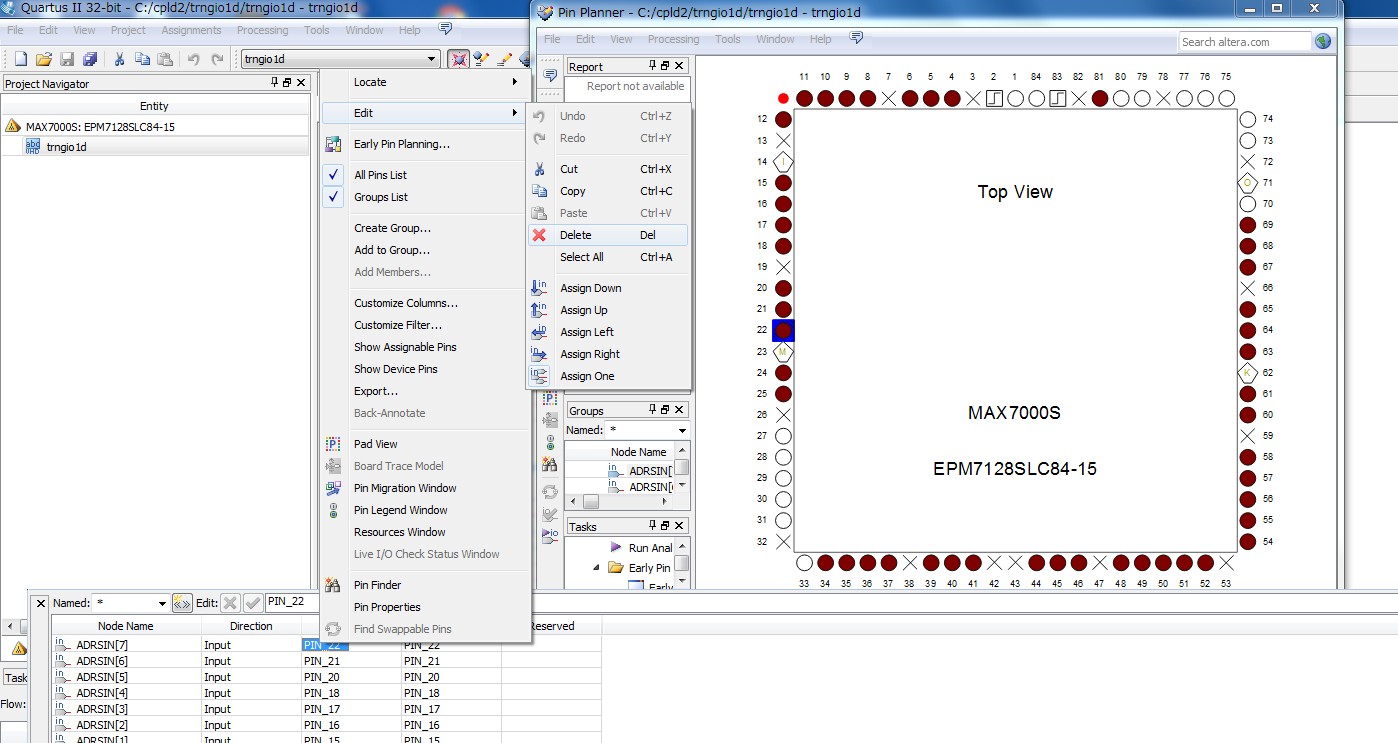

儕僗僩偺俹俬俶丵俀俀偺偲偙傠偵儅僂僗傪傕偭偰偄偭偰塃僋儕僢僋偡傞偲儊僯儏乕偑奐偒傑偡丅

偦偺儊僯儏乕偺拞偺乽俤倓倝倲乿偵儅僂僗傪傕偭偰偄偔偲丄偝傜偵儊僯儏乕偑奐偒傑偡丅

偦偺拞偺乽俢倕倢倕倲倕乿傪僋儕僢僋偡傞偲搊榐偑庢傝徚偝傟傑偡丅

抂巕攝抲恾偺俹俬俶俀俀偑仜偵側偭偰丄儕僗僩偺俙俢俼俽俬俶乵俈乶偺峴偺俴倧們倎倲倝倧値偑嬻敀偵側傝傑偟偨丅

忋偺椺偼尒杮偲偟偰壖偵峴側偭偨偩偗偱偡偐傜丄傕偟摨偠偙偲傪帋偟偵傗偭偰傒偨曽偼俹倝値丂俹倢倎値値倕倰傪廔椆偡傞慜偵丄偪傖傫偲尦捠傝偵捈偟偰偍偐側偗傟偽側傝傑偣傫丅

俻倳倎倰倲倳倱嘦偼嶌嬈傪偡傋偰儕傾儖僞僀儉偱婰榐偟偰偄傞傜偟偄偺偱丄忋偺忬懺偺傑傑俻倳倎倰倲倳倱嘦傪廔椆偡傞偲岆偭偨忣曬偑搊榐偝傟偨傑傑偵側傝傑偡丅

俙俢俼俽俬俶乵俈乶傪尦偺捠傝偵栠偟傑偟偨丅

塃忋偺乵倃乶傪僋儕僢僋偟偰俹倝値丂俹倢倎値値倕倰傪廔椆偟傑偡丅

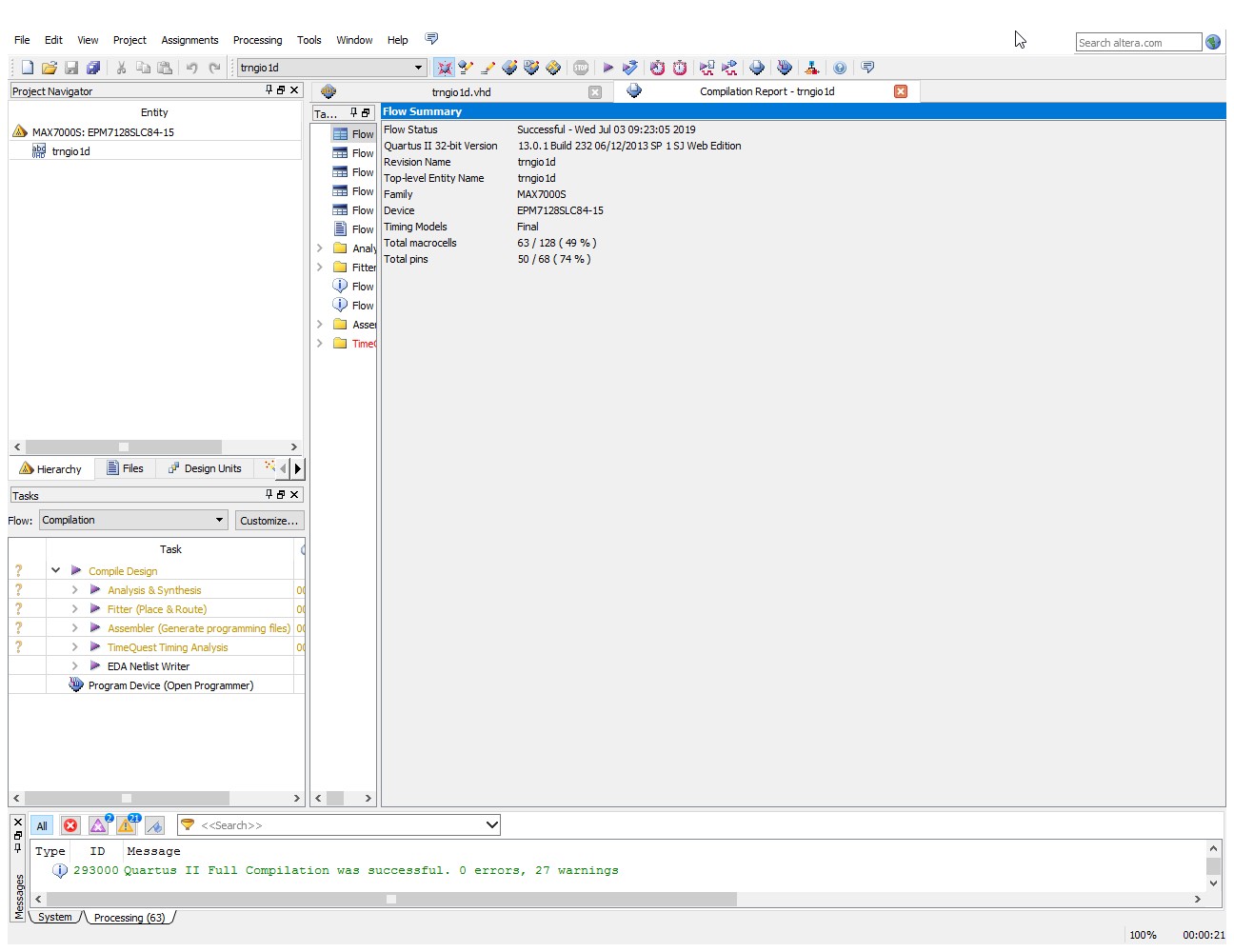

俹倝値丂俹倢倎値値倕倰傪巊偭偨偁偲偼丄傕偆堦搙僐儞僷僀儖傪幚峴偟偰偍偒傑偡丅

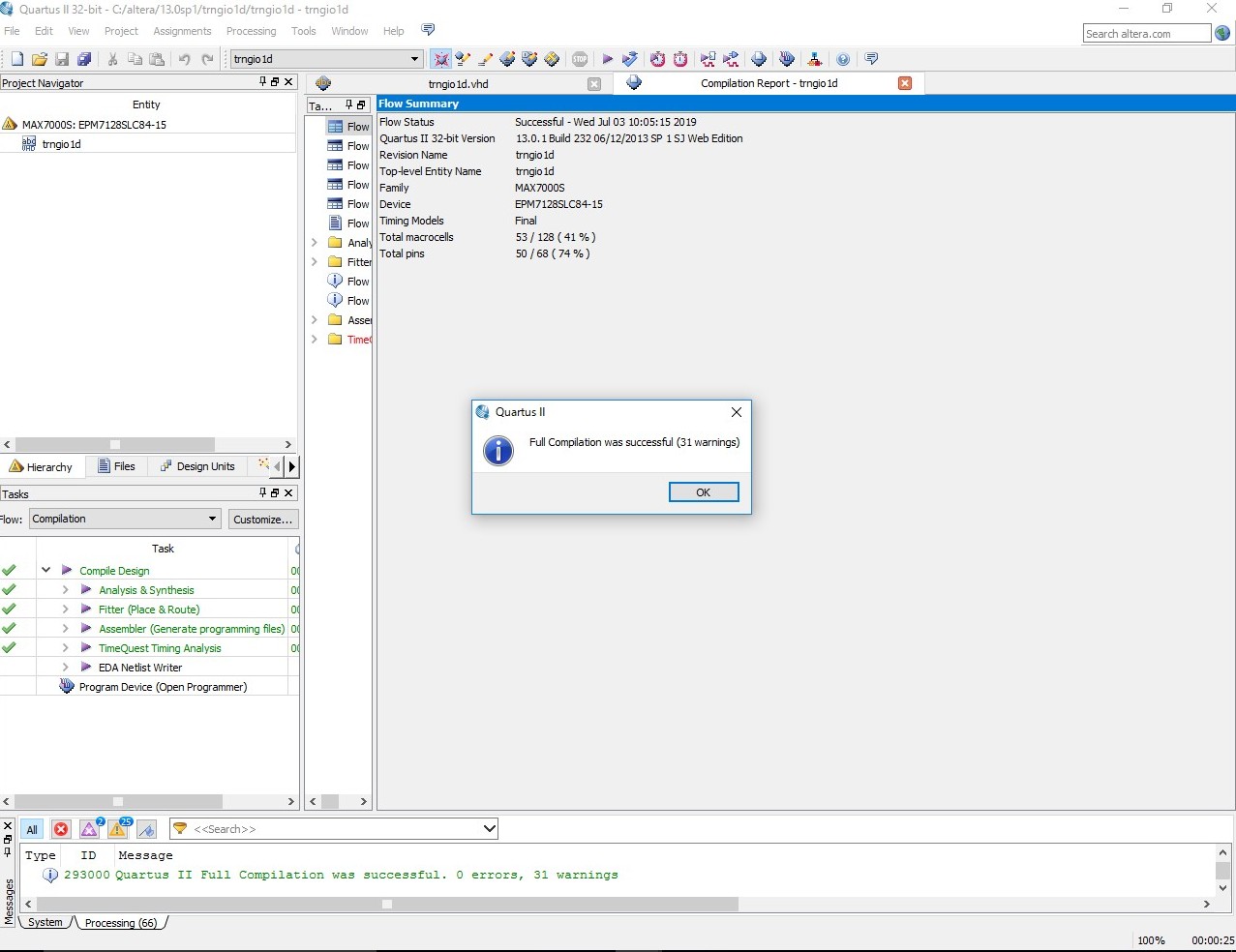

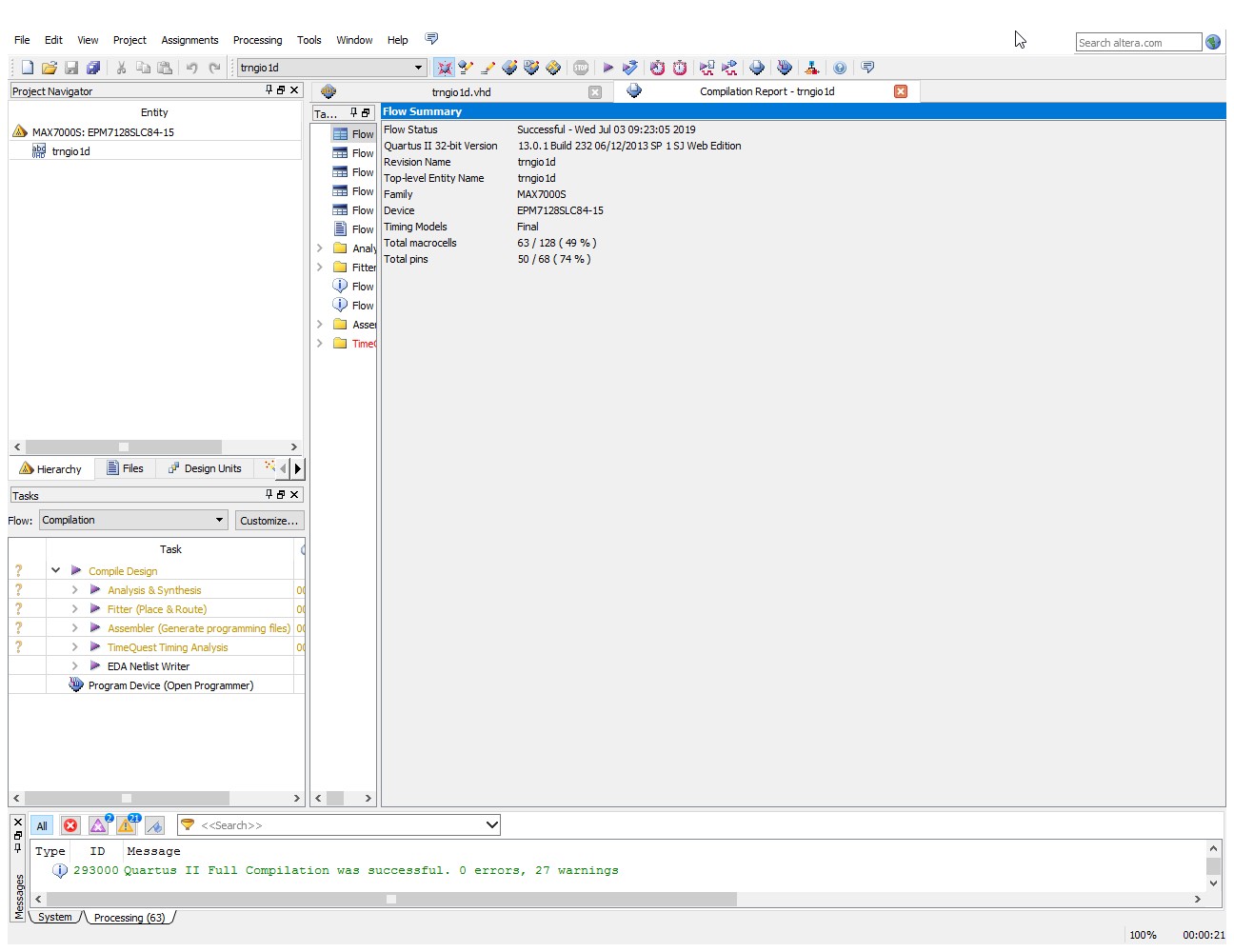

偙偺夋柺偼俹倝値丂俹倢倎値値倕倰傪幚峴偡傞慜偺僐儞僷僀儖廔椆帪偺俥倢倧倵丂俽倎倣倣倎倰倷偱偡丅

偙偙偺俿倧倲倎倢丂倣倎們倰倧們倕倢倢倱偺抣傪妎偊偰偍偄偰偔偩偝偄丅

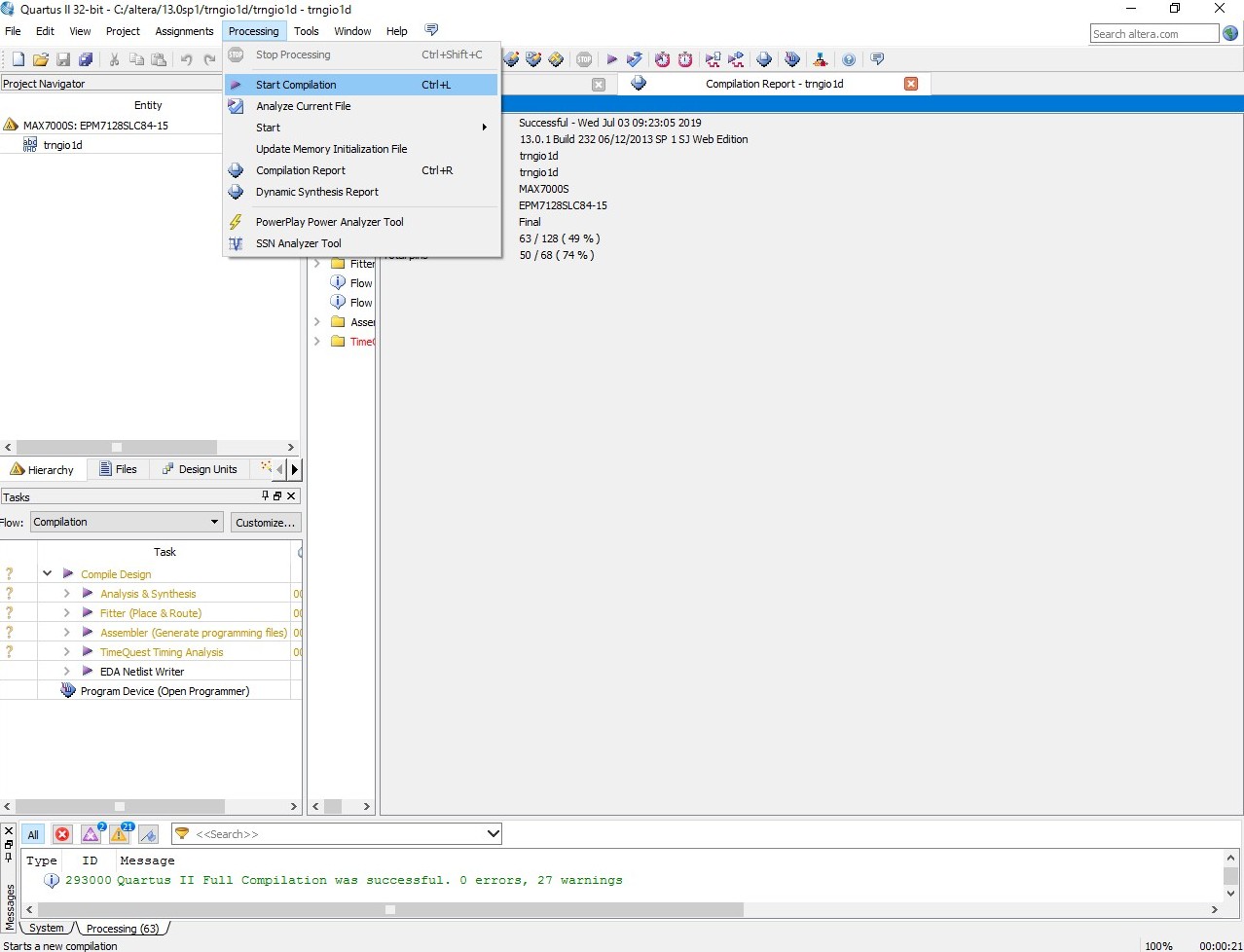

俹倰倧們倕倱倱倝値倗傪僋儕僢僋偟偰丄奐偔儊僯儏乕偺俽倲倎倰倲丂俠倧倣倫倝倢倎倲倝倧値傪僋儕僢僋偟傑偡丅

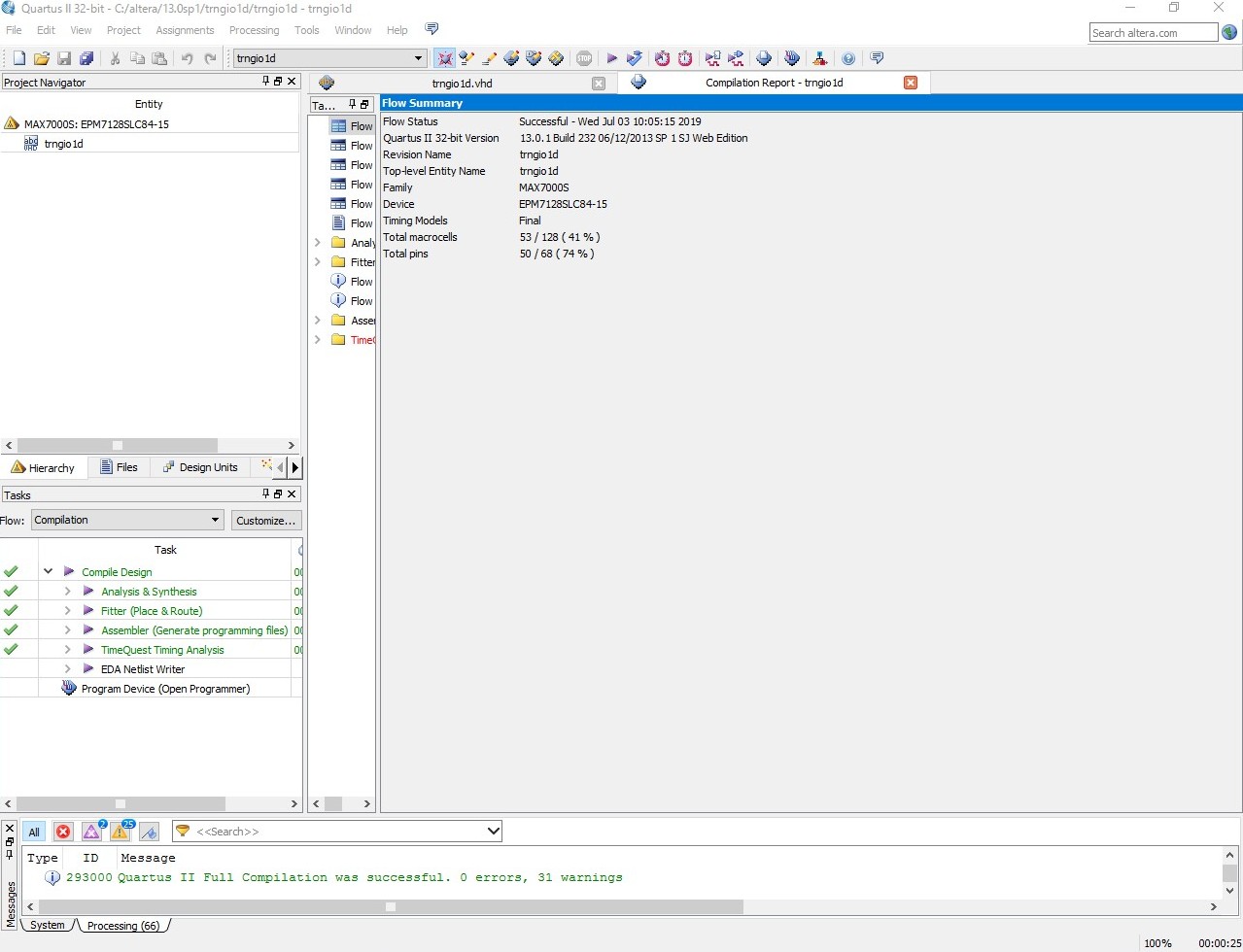

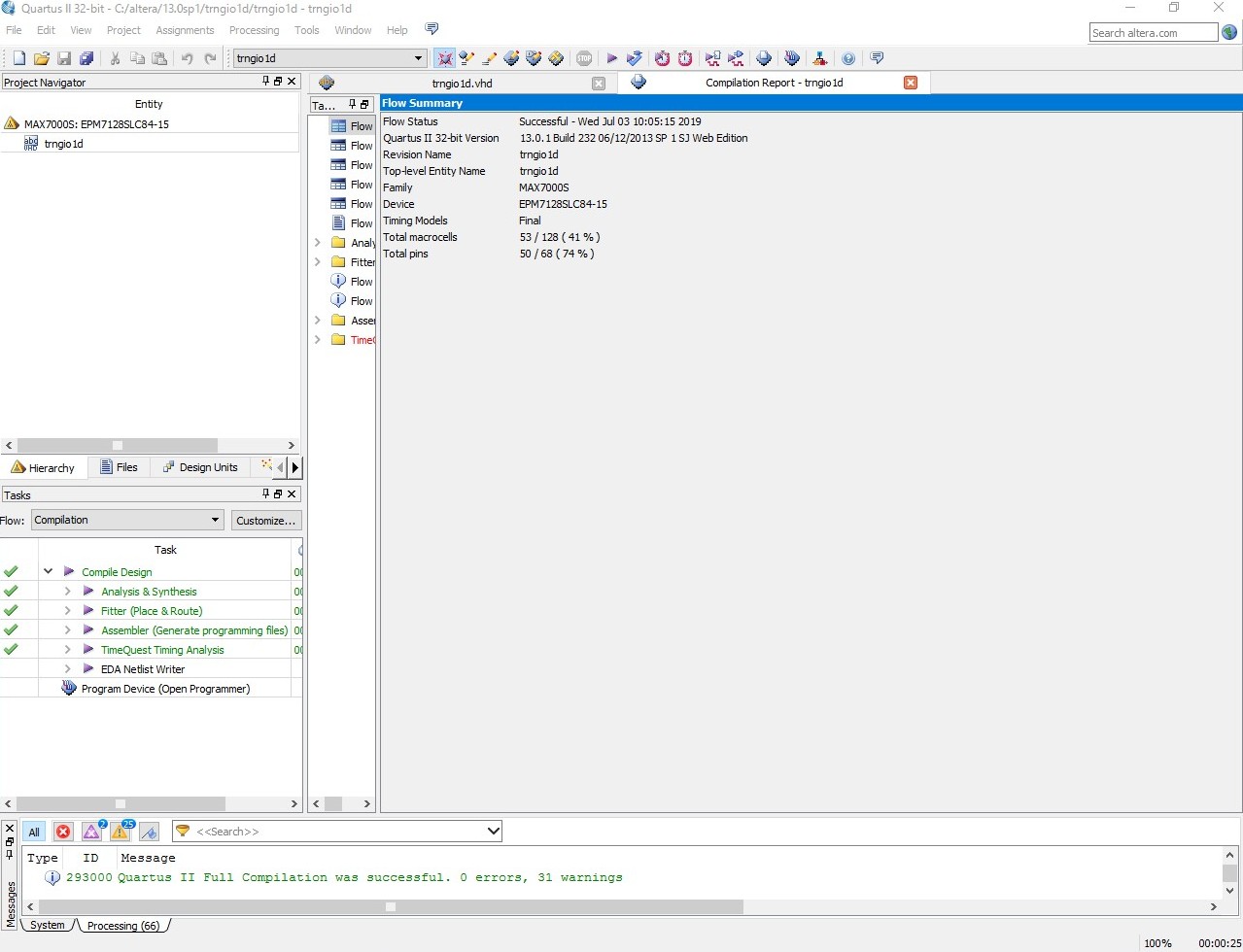

僐儞僷僀儖偑廔傝傑偟偨丅

俿倧倲倎倢丂俵倎們倰倧們倕倢倢倱偺抣偑曄傢傝傑偟偨丅

側偤偱偟傚偆偐丄偹偊丅

壖偺抂巕斣崋偺妱晅偑俹倝値丂俹倢倎値値倕倰偵傛偭偰丄暿偺抂巕斣崋偵妱傝摉偰傜傟偨偙偲偵傛偭偰丄俵倎們倰倧們倕倢倢倱偺慻傒崌傢偣偑曄傢偭偰丄偦偺寢壥巊梡検偑曄傢傞偺偐傕偟傟傑偣傫丅

崱夞偼妱傝摉偰慜偵斾傋偰巊梡検偑尭傝傑偟偨偑丄媡偵憹偊傞偙偲傕偁傞偐傕偟傟傑偣傫丅

偄偢傟偵偣傛丄俹倝値丂俹倢倎値値倕倰傪巊偭偨傜丄偦偺屻偱傕偆堦搙僐儞僷僀儖傪幚峴偟偰偍偐側偗傟偽側傜側偄傛偆偱偡丅

乽俷俲乿傪僋儕僢僋偟偰僐儞僷僀儖傪廔椆偟傑偡丅

僐儞僷僀儖傪廔椆偟傑偟偨丅

塃忋偺乵倃乶傪僋儕僢僋偟偰俻倳倎倰倲倳倱嘦傪廔椆偟傑偡丅

埲忋偱丄奆條偺庤尦偱尰嵼偱偒傞嶌嬈偵偮偄偰偼慡偰廔傝傑偟偨丅

偙偺偁偲偼幚嵺偵俤俹俵俈侾俀俉俽俴俠俉係偵僐儞僷僀儖屻偺僾儘僌儔儉傪彂偒崬傓嶌嬈偵側傝傑偡偑丄偦傟傪幚峴偡傞偵偼俠俹俴俢僩儗乕僯儞僌儃乕僪傪擖庤偟偰偄偨偩偐側偗傟偽側傝傑偣傫丅

尰嵼偦偺偨傔偺弨旛拞偱偡丅

嬤擔拞偵俠俹俴俢僩儗乕僯儞僌儃乕僪偵偮偄偰偺埬撪傪宖嵹梊掕偱偡丅

俠俹俴俢擖栧両乵戞俉俆夞乶

俀侽侾俋丏俈丏俇倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞