昗弨俿俿俴偩偗乮両乯偱CPU傪偮偔傠偆両乮慻棫偰僉僢僩偱偡両乯

(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞係俇俇夞乶

仠俶俵俬乮偦偺俀乯

倅俉侽偺俶俵俬乮俶倧値丂俵倎倱倠倎倐倢倕丂俬値倲倕倰倰倳倫倲乯偵偮偄偰偼乵戞係俁俈夞乶偱愢柧傪偄偨偟傑偟偨丅

愢柧傪偡傞偙偲偼偟偨偺偱偡偗傟偳丄堷梡偟偨倅倝倢倧倗幮偺倅俉侽俠俹倀丂倀倱倕倰丂俵倎値倳倎倢偺愢柧暥偑側傫偲傕偄偄偐偘傫側愢柧暥偱丄娞怱偺偲偙傠偑偄傑傂偲偮偼偭偒傝偟傑偣傫偱偟偨丅

偲偄偆偙偲偱丄乵戞係俁俈夞乶偼偁偄傑偄側愢柧偺傑傑偱廔傢偭偰偟傑偄傑偟偨丅

偦偺帪揰偱偼丄偦偺師偺夞偵堷偒懕偒俶俵俬偵偮偄偰丄傕偆彮偟偼偭偒傝偟偨愢柧傪彂偔偮傕傝偱偍傝傑偟偨丅

偲偙傠偑倅俉侽斉俿俲俉侽儃乕僪偺帋嶌婎斅偑弌棃偰偒偰偟傑偭偨傕偺偱偡偐傜丄偦偺傑傑偦偺愢柧偵擖偭偰偟傑偭偰丄俶俵俬偺懕偒側偳傕偆偳偙偐偵峴偭偰偟傑偄傑偟偨丅

偦偆偄偆偙偲偩偭偨偺偱偡偗傟偳丄傑偁偟偐偟丄俬俶俿偲堘偭偰晛捠偺梡搑偱偼俶俵俬側偳傪巊偆偙偲偼梋傝柍偄偲傕巚傢傟傑偡偟丄帠幚巹帺恎傕壗偐偵俶俵俬傪棙梡偟偨偲偄偆婰壇偼偁傝傑偣傫丅

傕偲傕偲俶俵俬側偳偲偄偆傕偺偼俉侽俉侽偵偼偁傝傑偣傫偱偟偨偟丄摉慠偺偙偲側偑傜俿俲俉侽偺儌僯僞僾儘僌儔儉偵偼娭學偑偁傝傑偣傫丅

俶俵俬偺僄儞僩儕傾僪儗僗偲偄偄傑偡偐丄僗僞乕僩傾僪儗僗偼侽侽俇俇斣抧偵屌掕偝傟偰偄傑偡偐傜丄倅俉侽傪巊偭偰俿俲俉侽屳姺儃乕僪傪嶌傞偙偲傪峫偊傞偲丄偦偺傾僪儗僗偼俿俲俉侽儌僯僞僾儘僌儔儉偑彂偐傟偰偄傞傾僪儗僗偱偡偐傜丄傕偟傕俶俵俬偺婡擻傪棙梡偟傛偆偲偡傟偽丄俿俲俉侽儌僯僞僾儘僌儔儉偺丄偦偺晹暘傪彂偒姺偊側偔偰偼側傝傑偣傫丅

偦傟傑偱偟偰俶俵俬傪巊偆昁梫偼柍偄偲巚偄傑偡偐傜丄偦偆偡傞偲偄傑偝傜俶俵俬側偳帩偪弌偝側偔偰傕傛偄偱偼側偄偐丄偲偄偆偙偲偵側傞偐傕偟傟傑偣傫丅

偟偐偟丄倅俉侽斉俿俲俉侽儃乕僪偺帋嶌婎斅偺愢柧偵堏偭偰偟傑偭偨傕偺偱偡偐傜丄姰慡偵拡偵晜偄偰偟傑偭偨偺偱偡偗傟偳丄幚偼丄師偺夞偁偨傝偱愢柧傪偡傞偮傕傝偱丄俶俵俬偵偮偄偰儘僕傾僫傪巊偭偰摦嶌傪妋擣偟偨帒椏側偳傕弨旛偟偰偄偨偺偱偡丅

偣偭偐偔偦偙傑偱偟偰傕丄傑偨偄偮傕偺偙偲偱丄偦偺傑傑偵偟偰偍偄偨傜偳偆偣偡偭偐傝朰傟偰偟傑偄傑偡丅

偱偡偺偱丄偙傟傕偙偺婡夛偵偙偙偱傑偲傔偰偍偒偨偄偲巚偄傑偡丅

乵戞係俁俈夞乶偺倀倱倕倰丂俵倎値倳倎倢偺俶俵俬偺愢柧偱偼偼偭偒傝偟側偄偲偙傠偑偁傝傑偡偗傟偳丄俶俵俬傕晛捠偺俬俶俿傕丄妱崬傒偺摦嶌偦偺傕偺偼婎杮揑偵偼摨偠偱偡丅

妱崬傒怣崋偼丄幚峴拞偺柦椷偺嵟屻偺僋儘僢僋偺偲偒偵俠俹倀偵擣幆偝傟丄倅俉侽俠俹倀丂倀倱倕倰丂俵倎値倳倎倢偺愢柧偵傛傞偲丄偦偺師偵僨乕僞僶僗偵撉傒崬傑傟偨柦椷偼柍帇偝傟偰丄偦偺偲偒偺俹俠乮僾儘僌儔儉僇僂儞僞乯偺抣偑奜晹僗僞僢僋偵曐懚偝傟偨偁偲丄侽侽俇俇斣抧偺柦椷偑幚峴偝傟傞丄偲偄偆偙偲偺傛偆偱偡丅

仠俶俵俬僥僗僩僾儘僌儔儉

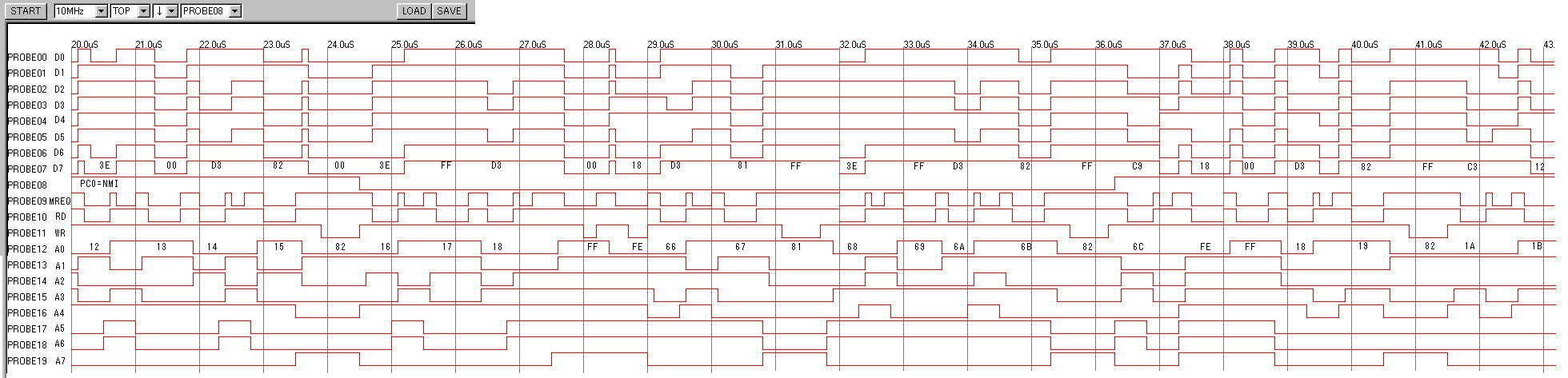

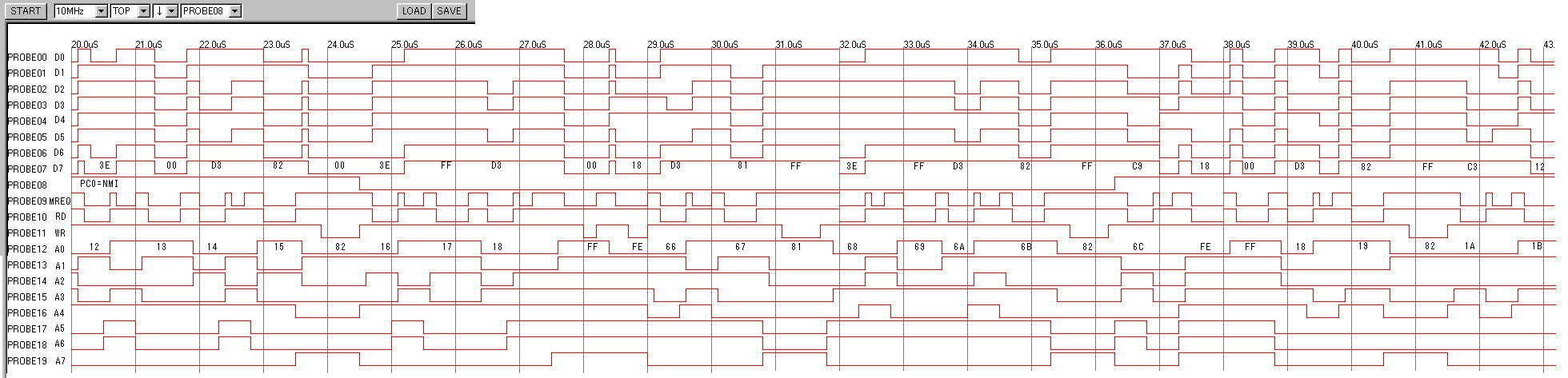

偦偺偁偨傝偺摦嶌傪丄乵戞俁俈係夞乶偱偛徯夘偟傑偟偨僇儊儗僆儞倀俽俛亄儘僕傾僫偱娤應偟偰妋擣偟偰傒傞偙偲偵偟傑偟偨丅

妱崬傒僾儘僌儔儉偺奐巒傾僪儗僗偼侽侽俇俇斣抧偱偡偐傜丄僾儘僌儔儉偼俼俷俵偵彂偔偟偐巇曽偑偁傝傑偣傫丅

崱夞偼俿俲俉侽儌僯僞僾儘僌儔儉偼柍帇偱偡丅

俼俷俵偺愭摢傾僪儗僗侽侽侽侽斣抧偐傜娙扨側僥僗僩僾儘僌儔儉傪彂偒傑偟偨丅

2010/2/20 9:40 NMITEST.TXT

END=006C

;;; Z80 NMI TEST 10.2.20

;

ORG $0000

0000 3100E0 LXI SP,$E000

0003 3E90 MVI A,90;82C55 A=IN,B,C=OUT

0005 D383 OUT 83

0007 3EFF MVI A,FF

0009 D382 OUT 82

000B DB80 LOOP1:IN 80

000D FEFF CPI FF

000F CA0B00 JZ LOOP1

0012 3E00 LOOP2:MVI A,00

0014 D382 OUT 82

0016 3EFF MVI A,FF

0018 D382 OUT 82

001A C31200 JMP LOOP2

;

ORG $0066

0066 D381 OUT 81

0068 3EFF MVI A,FF

006A D382 OUT 82

006C C9 RET

;END

LOOP1 =000B LOOP2 =0012

傓傓傓丅

俶俵俬偼倅俉侽偺婡擻偱偡偐傜丄倅俉侽僯乕儌僯僢僋偱彂偔偲偙傠側偺偱偡偑丄偳偆偄偆傢偗偐丄俉侽俉侽僯乕儌僯僢僋偱彂偄偰偟傑偄傑偟偨丅

僾儘僌儔儉偩偗傪尒偰傕丄偙傟偺偳偙偑妱崬傒偺僥僗僩僾儘僌儔儉偠傖丄偲偄偆姶偠偵側傝傑偡偑丄傕偪傠傫僔僇働偑偁傝傑偡丅

俴俷俷俹俀偺偲偙傠偱俉俀俠俆俆偺俠億乕僩乮俬乛俷傾僪儗僗俉俀乯偵侽侽偲俥俥傪岎屳偵弌椡偟偰偄傑偡丅

幚偼丄偦偺俠億乕僩偺價僢僩侽乮俹俠侽乯偺弌椡傪倅俉侽偺俶俵俬擖椡偵愙懕偟偰偁傞偺偱偡丅

偱偡偐傜侽侽侾係斣抧偺俷倀俿柦椷偑幚峴偝傟偨捈屻偵俶俵俬妱崬傒偑敪惗偡傞偼偢偱偡丅

偦傟傪儘僕傾僫偱娤應偟傛偆丄偲偄偆偙偲側偺偱偡丅

側偍丄偦偺忋偺俴俷俷俹侾偼丄儕僙僢僩傑偨偼俹俷倂俤俼丂俷俶偵傛偭偰偄偒側傝俴俷俷俹俀偵僄儞僩儕偝偣傞偲丄婲摦帪偺晄埨掕側忬懺偺偲偒偵俠俹倀偐傜弌椡偝傟傞怣崋偵傛偭偰儘僕傾僫偺僩儕僈偑摥偄偰偟傑偆偺傪杊巭偡傞偨傔偺傕偺偱偡丅

俉俀俠俆俆偺俙億乕僩乮俬乛俷傾僪儗僗俉侽乯偺價僢僩偺偳傟偐傪俧俶俢偵棊偲偡偙偲偱丄俴俷俷俹俀偺僾儘僌儔儉偑幚峴偝傟丄偦偙偱偼偠傔偰俶俵俬妱崬傒偑敪惗偡傞丄偲偄偆巇妡偗偱偡丅

仠儘僕傾僫偱偺娤應寢壥

儘僕傾僫偱娤應偟偨寢壥偱偡丅

崱夞偺僥僗僩僾儘僌儔儉偼抁偄僾儘僌儔儉偱幚峴斖埻偑尷傜傟偰偄傑偡偐傜丄傾僪儗僗僶僗偺忋埵俉價僢僩乮俙俉乣俙侾俆乯偼儘僕傾僫偵偼擖椡偟傑偣傫偱偟偨丅

俹俼俷俛俤侽俈偺儔僀儞偵僨乕僞僶僗乮俢侽乣俢俈乯偺抣傪彂偒壛偊偰偁傝傑偡丅

傑偨俹俼俷俛俤侾俀偺儔僀儞偵傾僪儗僗僶僗偺壓埵俉價僢僩乮俙侽乣俙俈乯偺抣傪彂偒壛偊偰偁傝傑偡丅

俹俼俷俛俤侽俉偑俶俵俬擖椡偱偡丅

俀係兪倱偺偲偙傠偱俢俁丂俉俀乮俷倀俿丂俉俀乯偑幚峴偝傟偰丄傾僪儗僗僶僗偑俉俀丄僨乕僞僶僗偑侽侽偵側偭偰偄傑偡丅

倂俼怣崋乮偙偺偲偒偼幚偼俬俷倂俼乯偺棫偪忋偑傝偱俉俀俠俆俆偺俠億乕僩偐傜侽侽偑弌椡偝傟丄偦偺寢壥俶俵俬偑俴偵側偭偰偄傑偡丅

俶俵俬擖椡偼偦偺師偺俁俤丂俥俥乮俵倁俬丂俙丆俥俥乯偺幚峴偺廔傢傝偵庴晅偗傜傟傑偡丅

僨乕僞僶僗偵偼丄偦偺師偺柦椷僐乕僪偺俢俁偑儊儌儕偐傜撉傒弌偝傟偰偄傑偡偑丄偦偺柦椷僐乕僪偼柍帇偝傟偰丄偦偺師偺僞僀儈儞僌偱丄偙偺偲偒偺傾僪儗僗丄偮傑傝俹俠乮僾儘僌儔儉僇僂儞僞乯偺抣乮侽侽侾俉乯偑丄僗僞僢僋偵戅旔偝傟偰偄傑偡丅

偦偺偁偲傾僪儗僗僶僗偑俇俇偵側偭偰偄偰丄偙偙偱侽侽俇俇斣抧偺妱崬傒僾儘僌儔儉偑幚峴偝傟偨偙偲偑傢偐傝傑偡丅

妱崬傒僾儘僌儔儉偼傾僪儗僗侽侽俇俠偺俠俋乮俼俤俿乯偱張棟傪廔傢傝丄傕偲偺僾儘僌儔儉偵栠傝傑偡丅

僗僞僢僋偵曐懚偝傟偰偄偨傾僪儗僗侽侽侾俉偑俹俠乮僾儘僌儔儉僇僂儞僞乯偵栠偝傟丄偦偟偰偁傜偨傔偰丄偝偒傎偳柍帇偝傟偨丄侽侽侾俉偺俢俁丂俉俀乮俷倀俿丂俉俀乯偑幚峴偝傟偰偄傑偡丅

俀侽侾侽丏俁丏俁侾倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞