トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK-80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第173回]

●CLR信号の入力

前回はトランジスタCPUのCLOCK回路基板の出力信号をPIC-CPLDロジアナで確認しました。

CLOCK回路基板ではもうひとつ確認しておきたい信号があります。

それはCLR信号です。

そもそもはCLR信号の入力のためにカウンタ回路に入れたダイオードと電流制限抵抗が災いしてQ_出力がなまってしまっていたのに気が付いて、その部分の対策のために、何回かの試作の末にやっと出来てきたCLOCK回路基板をまたしても作り直す羽目になったのでした([第167回]、[第169回])。

ということなので、新しく作り直したCLOCK回路に外部からCLR信号を入れて、カウンタ出力が考え通りにちゃんとクリアされるかどうかを、PIC-CPLDロジアナで確認してみることにしました。

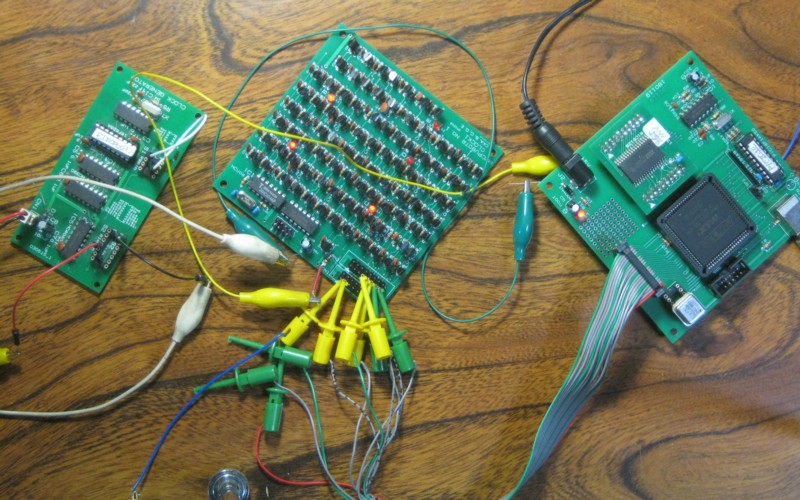

下はPIC-CPLDロジアナでCLOCK信号を記録中の写真です。

外部から入力するCLR信号は写真左側のCLOCK発生回路の出力を使いました。

観測し易い適当な信号であればよいので、250KHzの出力をCLR信号として入力しました。

中央はCLOCK回路基板です。

右側はPIC-CPLDロジアナです。

前回はCLOCK回路基板のコネクタとロジアナ基板のコネクタの入出力信号の丁度合うところをみつけてフラットケーブルで接続しましたが、それではCLR信号を見ることはできません。

今回は手抜きはやめて、ちゃんとフラットケーブルの先にフッククリップをつけたものを製作して、それで測定を行ないました。

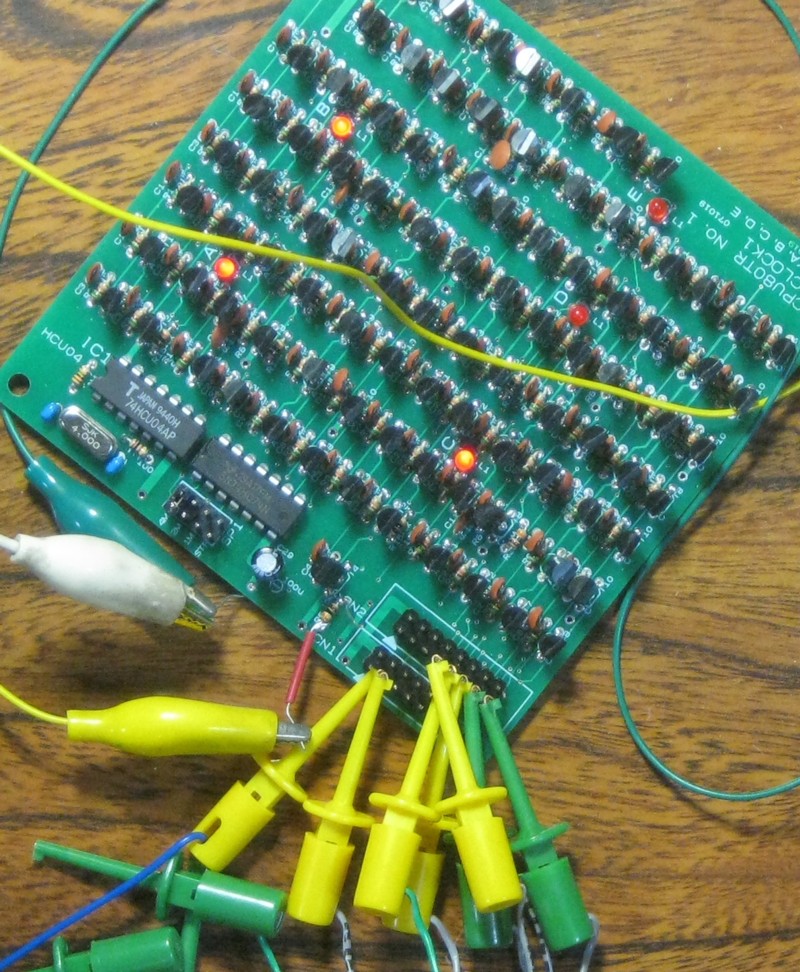

CLOCK回路基板にはA、B、C、D、Eの5段(5ビット)のバイナリカウンタ回路があります。

各出力にはLEDがつけてあります。

テストで入力したCLR信号は250KHzで、これは丁度D出力の周波数と同じです。

CLR信号はCLOCK回路の動作とは同期していませんが、D出力と同じ周波数のため、D出力、E出力はほぼ常時クリア状態になります。

写真でははっきりわかりませんが、D出力LEDはかすかに点灯し、E出力LEDは完全に消灯しています。

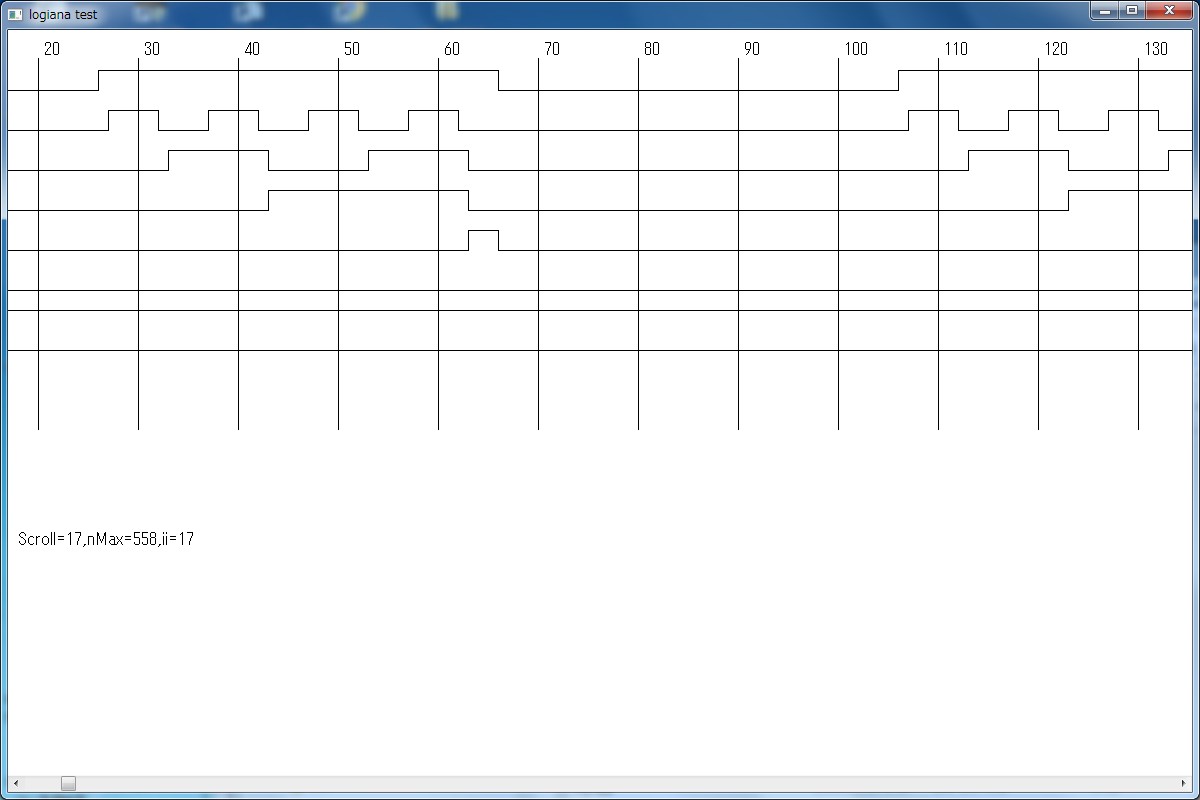

下は上で記録したデータをPIC-CPLDロジアナで表示した画面です。

一番上がCLR信号(250KHz)です。

250KHzの1周期は4μsです。

サンプリングクロックは20MHzで縦線は10サンプリング毎に入ります。

ですから縦線の間隔は2MHz(0.5μs)です。

CLR信号は2μs毎にON、OFFを繰り返しています。

その下の信号は、上から順にクロックA(2MHz)、クロックB(1MHz)、クロックC(500KHz)、クロックD(250KHz)、クロックE(125KHz)です。

CLR信号がLの期間中は各出力はクリアされてLになっています。

CLR信号はCLOCK回路とは非同期ですから、たまたまD出力がHになったすぐあとでクリアされています。

今回はテストなのでCLR信号はCLOCK回路とは非同期に入力しましたが、実際のトランジスタCPU回路ではCLOCK信号に同期してCLR信号が出力されるはずです。

ともあれ今回のテストでCLR回路が正しく機能することが確認できました。

トランジスタでCPUをつくろう![第173回]

2019.11.1upload

前へ

次へ

ホームページトップへ戻る