トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK−80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第357回]

●CPLDロジアナで74HC175回路(Tクロック回路)の出力波形を確認しました

前回ジャノメ基板に組んだ74HC175を使ったTクロック回路テスト基板の出力波形をCPLDロジアナで確認しました。

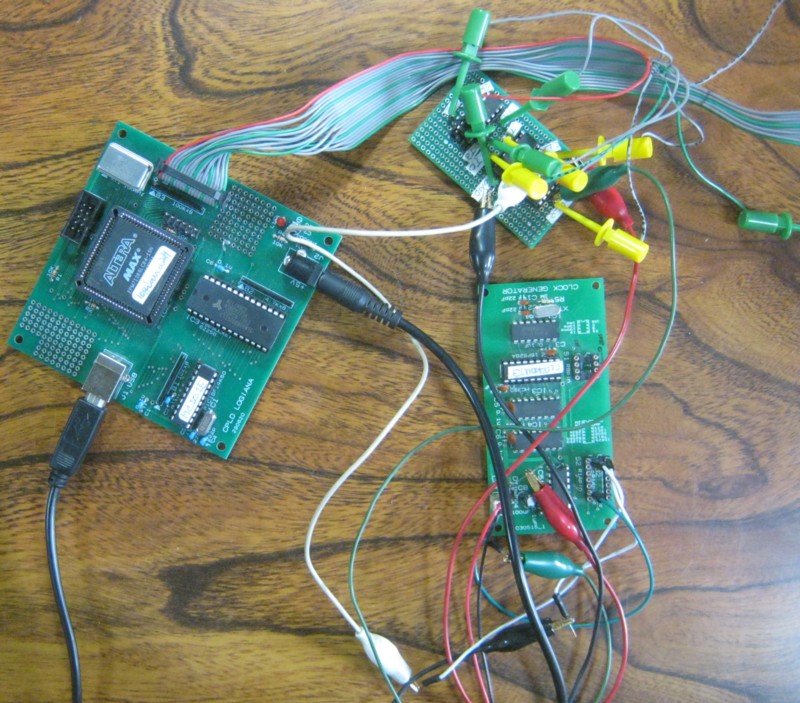

下はテスト中の写真です。

左はCPLDロジアナで右下はクロック発生ボード、右上が74HC175を使ったTクロック回路基板です。

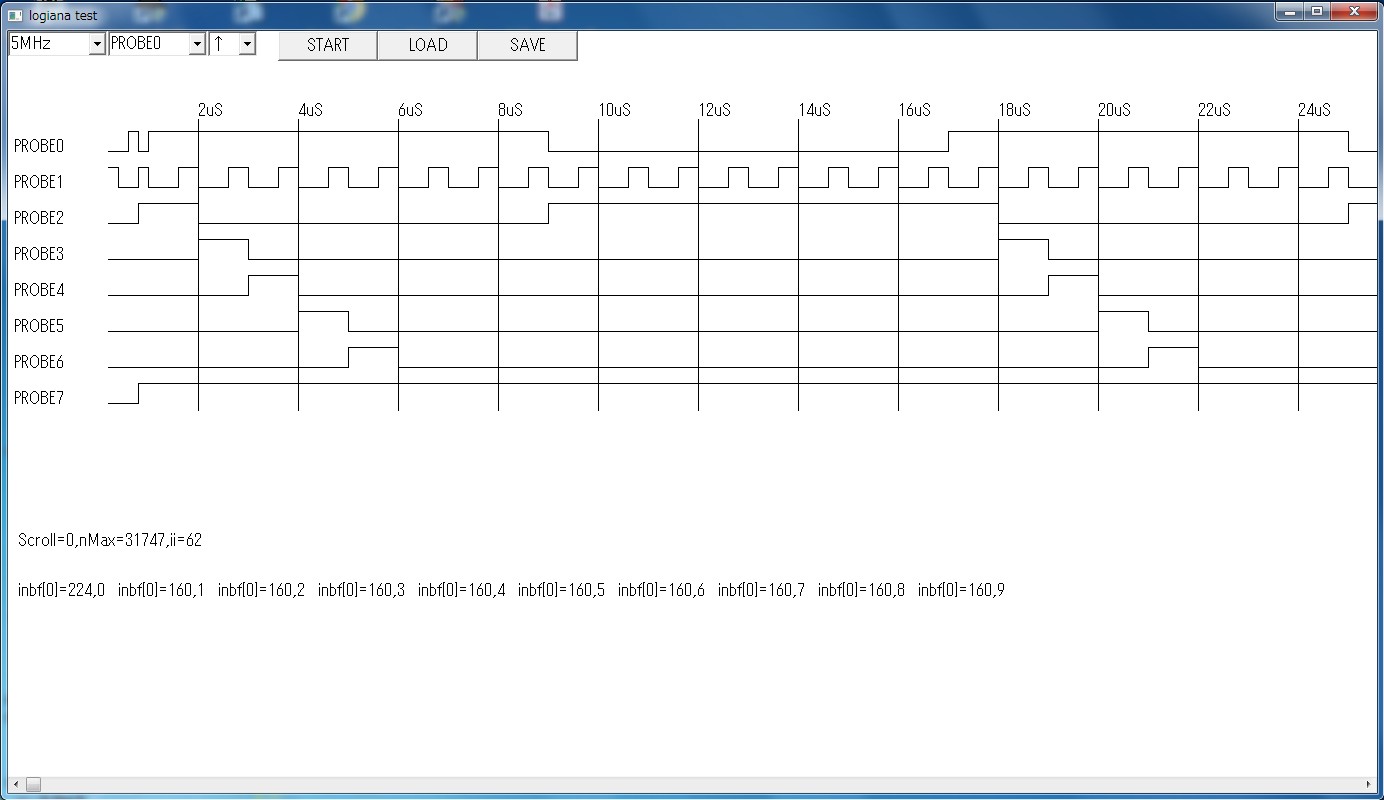

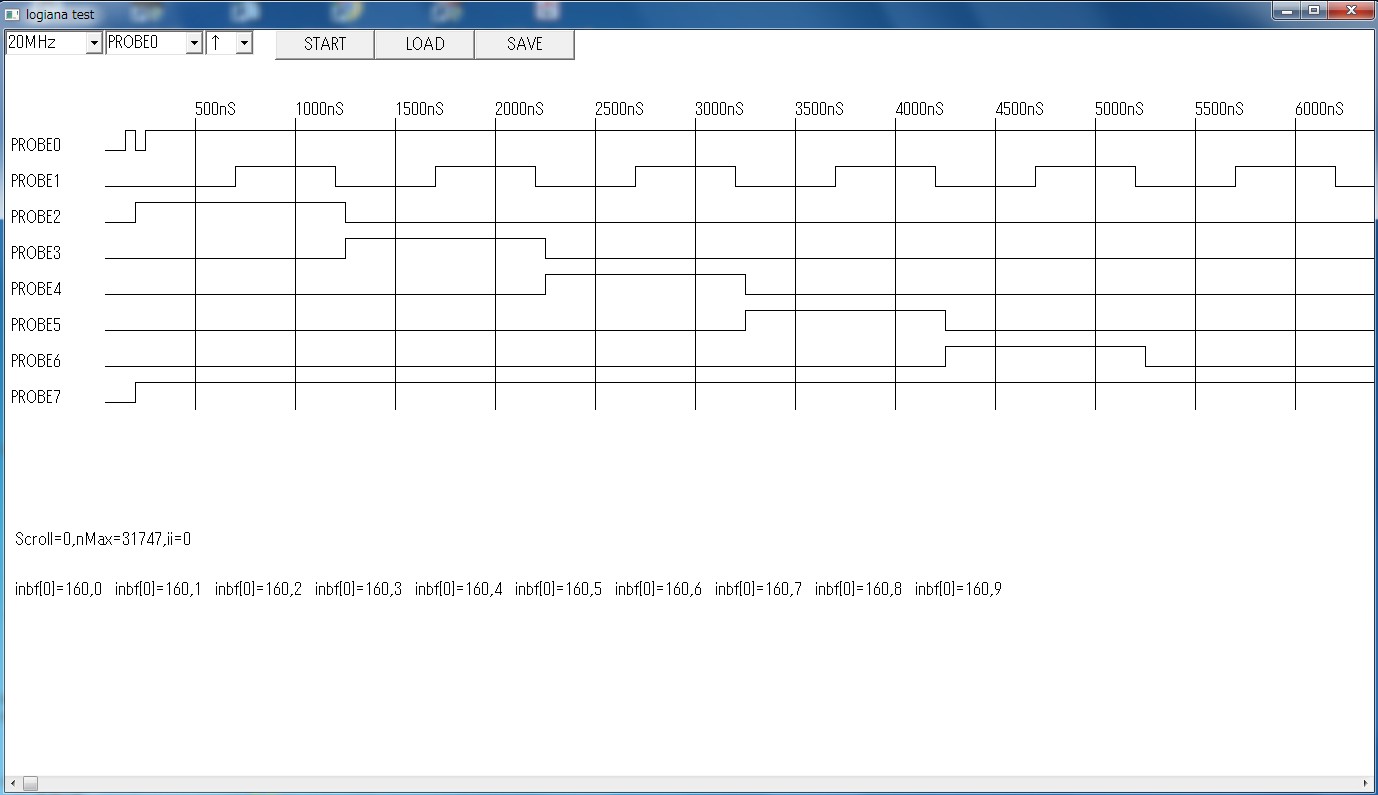

下はロジアナの出力波形です。

まずはサンプリングクロック5MHzで確認しました。

PROBE0はCLR信号です。

CLR信号として62.5KHzを入れています。

PROBE1はCLK信号です。

CLK信号として1MHzを入れています。

PROBE2がT0出力です。

PROBE3〜PROBE6がT1〜T4出力です。

T1〜T4はCLKの1周期分の幅のパルスです。

T0はCLRがHになったあとの1周期の期間にHになりますが、CLRがLの期間中もHになります。

CLRがLのときはCPU回路は動作しませんから、その期間中ずっとT0=Hであっても問題はないと考えています。

CPLDロジアナで出力波形を確認した結果、74HC175で作ったテスト回路ではT0〜T4まで正しい出力が得られていることが確認できました。

今回は問題はないようです。

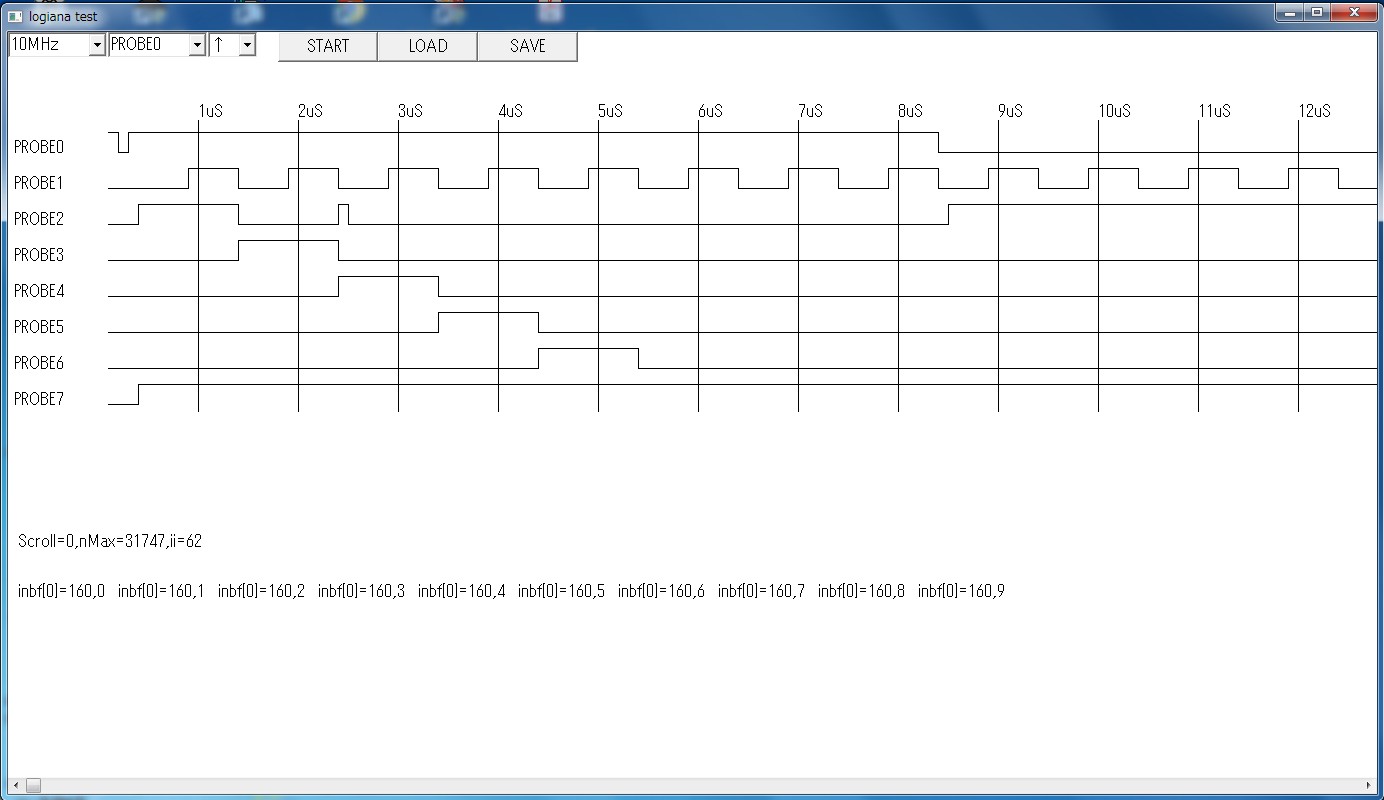

サンプリングクロックを10MHzにしました。

PROBE2(T0クロック)にヒゲが出ています。

T0だけは2つの信号のANDを取っていますから出力遅れの影響が出ていると考えられます。

この位置でのヒゲは問題ないと思いますが、もしこれが問題になるようならそのときに何か対策を考えることにします。

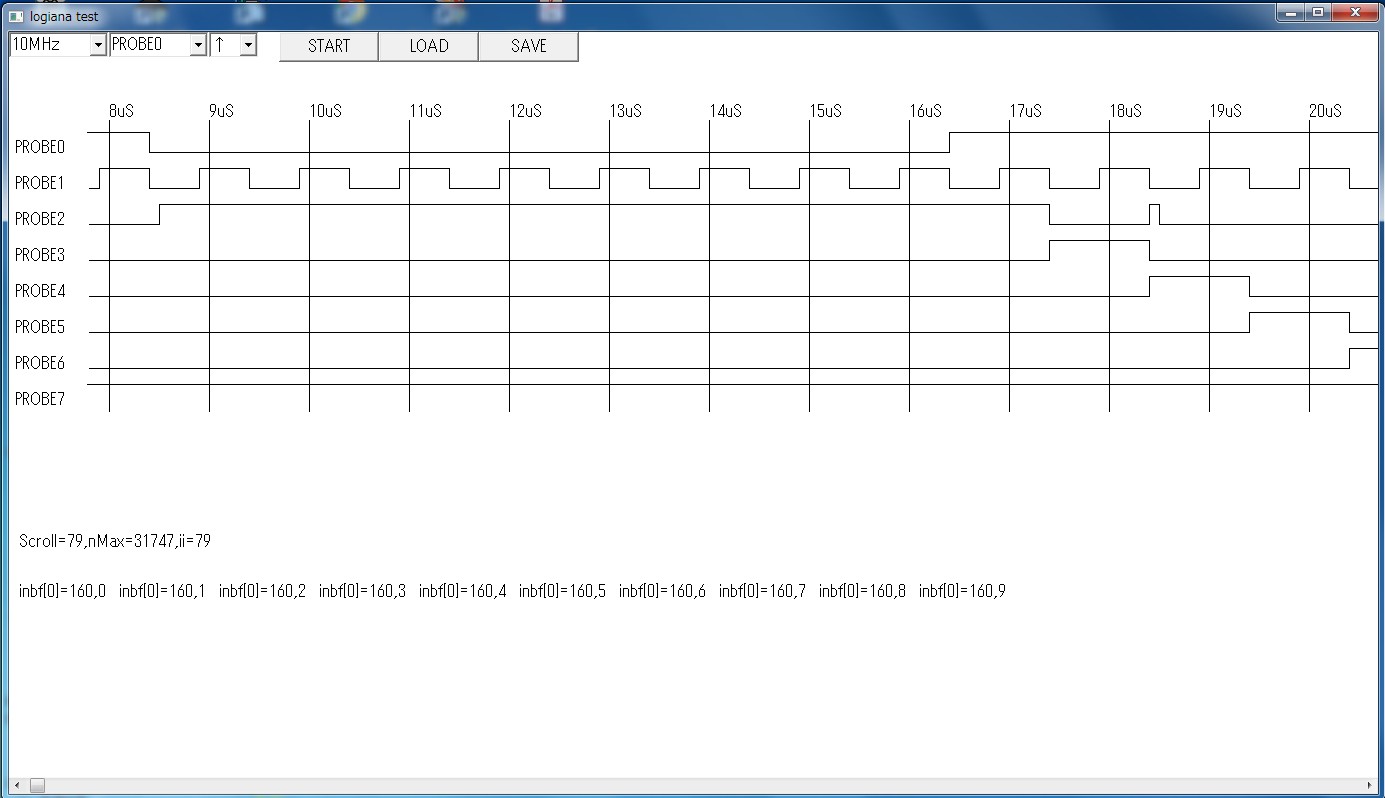

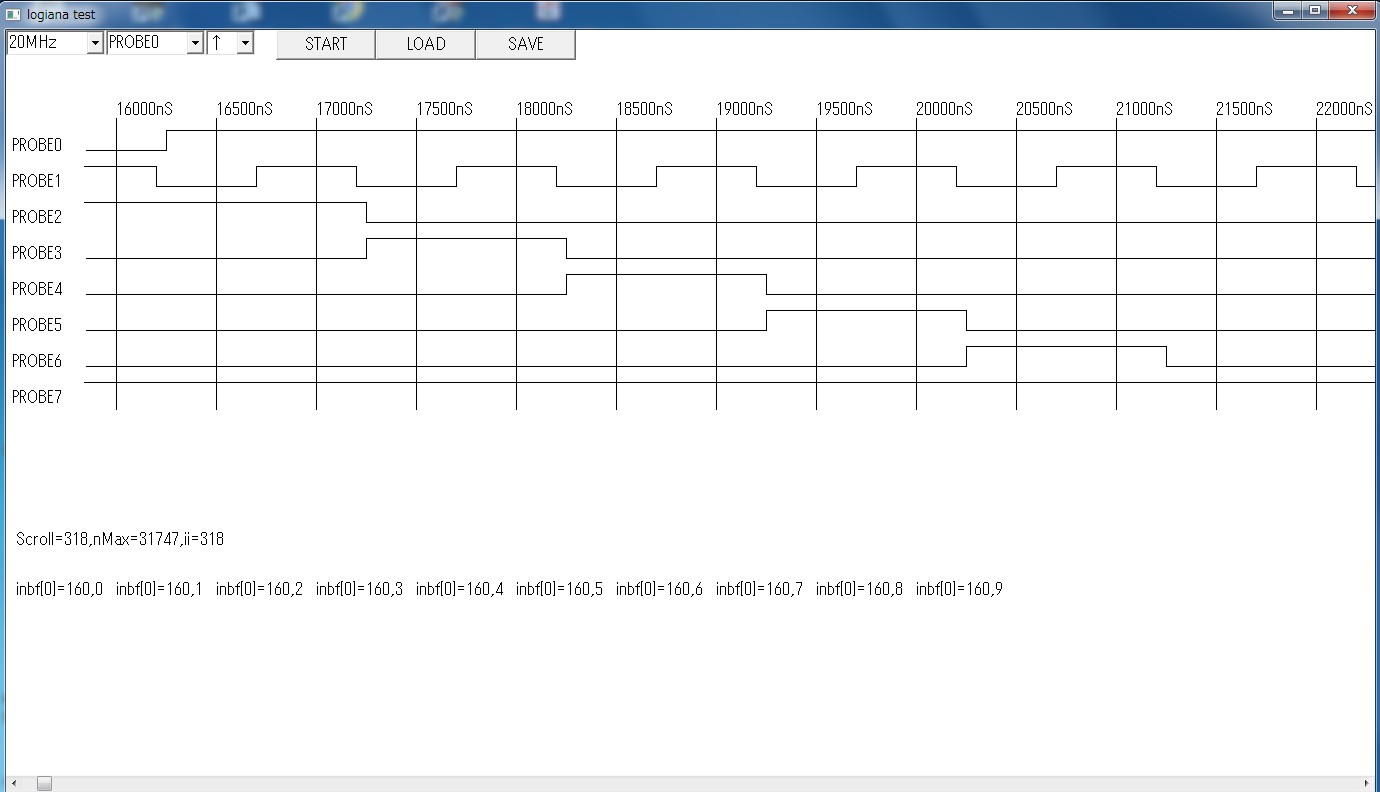

表示画面を少しスクロールしました。

やはりT0は同じ位置にヒゲが見えます。

サンプリングクロックを20MHzにしました。

おや。

PROBE2(T0)のヒゲが消えてしまいました。

サンプリングのタイミングでヒゲが見えたり見えなかったりするようです。

おそらくこのヒゲは非常に幅のせまいパルスだと考えられます。

表示をスクロールさせました。

やはりヒゲは見えません。

とにかく74HC175を使ったTクロック回路は正しく動作するようです。

そこまで確認ができましたから、次回はMクロック回路を作ってみることにします。

トランジスタでCPUをつくろう![第357回]

2021.5.26upload

前へ

次へ

ホームページトップへ戻る