トランジスタで8080をつくってしまおうというまさにびっくり仰天、狂気のプロジェクトです!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

見事にできましたら、もちろんTK−80モニタを乗せて、それからBASIC、CP/Mを走らせましょう!

☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆☆

[第87回]

●スリーステートバッファ

このところずっとCPUのレジスタについて検討を重ねてきました。

その過程でなんだかんだがありまして、結局のところ大幅なトランジスタ数の削減には至らず、そこそこの削減に終ってしまいそうです。

今回は最後まで残っておりました、レジスタの出力段、スリーステートバッファについて検討をします。

その部分は[第83回]でお見せした下の回路図の右側の出力部です。

その部分だけ取り出してテストしてみましたところ、やっぱり速度が出ないことがわかりました。

OE_として与える信号の周波数が低いときはよいのですが、MHzになると出力がめちゃくちゃになってしまいます。

あ。

もともとこの回路図には欠けているところがありまして、右下部分の2N7000のゲートにはプルダウン抵抗が必要でした。

2N7000のゲートにはOE_が入力されている2SA1015のコレクタ出力がつながっていますが、OE_がHのときには2SA1015がOFFになるため、2N7000のゲート入力がオープンになってしまいます。

それを防ぐために抵抗でプルダウンしておく必要があります。

テストではもちろんプルダウン抵抗をつけてテストしたのですが、それでもやっぱりだめでした。

当連載の最初のところでトランジスタのコレクタを抵抗でプルアップした回路は信号の立ち上がりが遅い、ということを書いておきながら([第5回])、書いた張本人がこういう回路を平気で描いているのですから、我ながらあきれてしまいます。

そこでは2N7000のドレインをプルアップしてのテストでしたが、2SA1015でも同じことで、PNPトランジスタの場合にはコレクタ出力をプルダウンすることになります。

遅まきながらそういうことに気が付きましたので、その部分を下のように改めました。

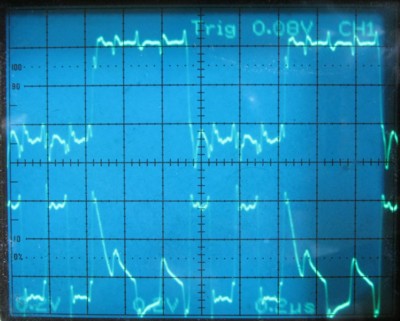

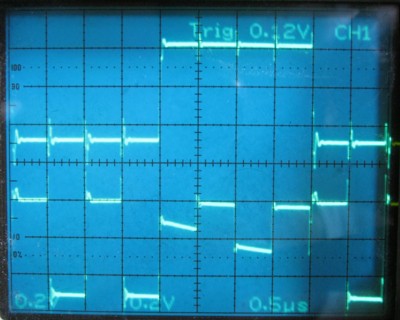

そのようにした回路でテストした結果が下の写真です。

スリーステート出力の効果を確認するため、スリーステートバッファへの入力にはRSフリップフロップの出力ではなくて、4MHzのパルスを与えました。

上側(CH1)はOE_として与えた1MHzのパルスです。

下側がスリーステートバッファの出力です。

OE_がHの期間に出力がハイインピーダンスであることが確認できるように1KΩでプルダウンしました。

しかし4MHzもの周波数になると、かなり入力信号が出力に漏れてしまっています。

ま、しかしこのテストはちょっと乱暴で、実際にはスリーステートバッファへの入力はRSフリップフロップの出力ですから、HまたはLのスタティックなレベル信号のはずですから、問題はありませんでしょう。

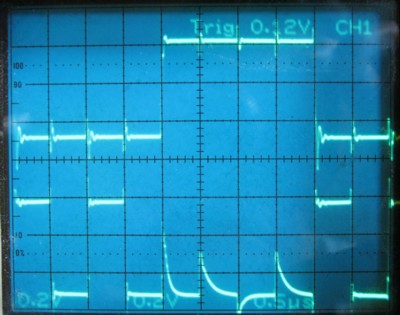

OE_に250KHz、データ入力として1MHzパルスを与えてみました。

かなり出力が落ち着きました。

出力につけていた1KΩのプルダウン抵抗を外しました。

OE_がHの期間(上側、CH1)は出力信号(下側、CH2)はハイインピーダンスです。

入力信号の漏れ(?)、ノイズ(?)で出力がバタついています。

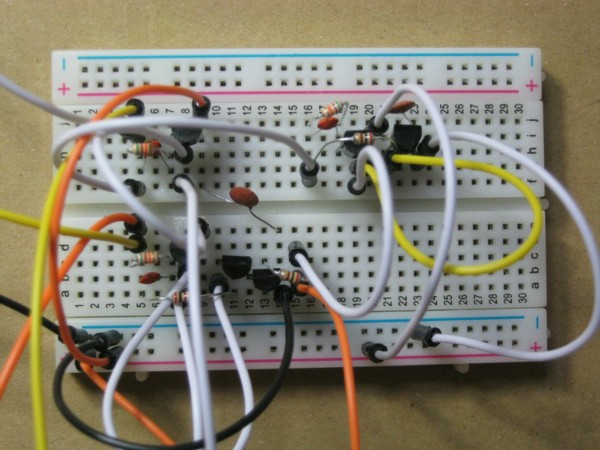

こちらがテストに使った回路です。

ブレッドボードに組んでテストしました。

今までの検討の結果、最終的な回路図は下のようになりました。

破線で囲んだ部分が1ビット分の回路です。

NANDゲートが3つとインバータが1つですから、トランジスタ数は12+2=14個です。

その8ビット分では14×8=112個になります。

それにOE_とWR_の部分のトランジスタを加えると112+10=122個になります。

当初の目論見よりもちょっと増えてまいましたが、精度アップのためにはやむを得ませんでしょう。

トランジスタでCPUをつくろう![第87回]

2015.6.24upload

前へ

次へ

ホームページトップへ戻る