乵怴楢嵹乶俠俹俴俢擖栧両

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

偄偮偐巊偆偙偲偵側傞偩傠偆偲巚偭偰偼偄偨偺偱偡偑丅

壗傪崱崰偵側偭偰丄偲偄偆傛偆側傕偺偱偡偑丅

傛偆傗偔杮婥偱丄俠俹俴俢偲巐偮偵庢傝慻傒傑偡丅

乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣乣

乵戞侾俀俁夞乶

仠俠俹俴俢儘僕傾僫乮侾俁乯侾侽侽俵俫倸偱僥僗僩

慜夞偼懯栚尦偺偮傕傝偱傗偭偰傒偨俆侽俵俫倸偱偺僥僗僩偑怣偠傜傟側偄偙偲偵側傫偲傎偲傫偳僄儔乕傕側偔幚峴偱偒偰偟傑偄傑偟偨丅

傑偝偵嬃堎揑側寢壥偱偡丅

傕偲偼俀侽俵俫倸偺怣棅惈傪妋曐偡傞偨傔偵偦傟傛傝傕崅偄廃攇悢偱僥僗僩偟偰傒傛偆偲偄偆偙偲偱巒傑偭偨崱夞偺堦楢偺僥僗僩偱偟偨偑堄奜側寢壥偲側傝傑偟偨丅

堦懱偳偆側偭偰偄傞傫偱偟傚偆偐偹偊丅

傑丄偟偐偟丄偙傟偼婌偽偟偄偙偲偱偡丅

偙偙傑偱偆傑偔偄偭偨偺側傜丅

摉弶偺俀侽俵俫倸偵壛偊偰偦偺忋偵俆侽俵俫倸僋儘僢僋傪捛壛偟偰傕傛偄偺偱偼丅

傕偪傠傫摦嶌曐徹偼偁傝傑偣傫丅

俼俙俵偺傾僋僙僗僞僀儉傪偼傞偐偵墇偊傞崅懍偱偺傾僋僙僗偱偡偐傜丄僄儔乕偑敪惗偟偰傕巇曽偑偁傝傑偣傫丅

偆傑偔摦嶌偟偨傜栕偗傕偺偲偄偆偖傜偄偺寉偄婥帩偪偱側傜傛偄偱偟傚偆丅

偲偙傠偱僇儊儗僆儞儘僕傾僫偺嵟崅廃攇悢偼侾侽侽俵俫倸偱偡丅

偦傟偼偦偙偵巊傢傟偰偄傞俠俹俴俢偺僋儘僢僋傕崅懍偱俼俙俵偺傾僋僙僗僞僀儉傕挻崅懍偩偐傜偙偦偱偒傞偙偲偱偡丅

偟偐偟丅

傢偑俠俹俴俢儘僕傾僫傕俼俙俵偺傾僋僙僗僞僀儉傪偼傞偐偵墇偊傞傑偝偐偺俆侽俵俫倸偱摦嶌偟偨偱偼偁傝傑偣傫偐丅

偙偙傑偱偒偨傜丅

偦傟偙偦懯栚尦偱侾侽侽俵俫倸偵挧愴偟側偄傢偗偵偼偄偒傑偣傫偱偟傚偆丅

偁丅

偱傕巆擮側偑傜俆侽俵俫倸偼偙偺僔僗僥儉偲偟偰偼忋尷側偺偱丄侾侽侽俵俫倸偺僷儖僗偼嶌傟傑偣傫乧丅

巆擮偱偡乧丅

偆丅

懸偰傛丅

妋偐偵俆侽俵俫倸偱偼俵俤俵倂俼僷儖僗傪們倢倠倵倠俀乮侾侽侽俵俫倸乯傪俀暘廃偟偰嶌傝弌偟偰偄傑偡丅

們倢倠倵倠俀偼偦傕偦傕俠俹俴俢偵嫙媼偟偰偄傞僋儘僢僋傪偦偺傑傑巊偭偰偄傑偡丅

偦傟側傜偽丅

崱傑偱偺傛偆偵們倢倠倵倠俀傪壗暘廃偐偟偰偦傟傪俵俤俵倂俼偵偡傞偺偱偼側偔偰丄們倢倠倵倠俀傪偦偺傑傑俵俤俵倂俼偵偟偨傜侾侽侽俵俫倸偵側傞偠傖偁傝傑偣傫偐丅

崱夞巚偄偮偄偨侾侽侽俵俫倸偺応崌偼壓偺攇宍恾偺傛偆偵側傝傑偡丅

偁偁丄偟偐偟丅

侾侽侽俵俫倸偺侾廃婜偼側傫偲偨偭偨偺侾侽値倱偱偡丅

偦傟傪偦偺傑傑俵俤俵倂俼怣崋偲偟偰巊偄傑偡丅

偲偄偆偙偲偼丅

偦偺僷儖僗暆偼俴婜娫偑偨偭偨偺俆値倱偱俫婜娫傕摨偠偔俆値倱偱偡乮両乯丅

俵俤俵倂俼偺僒僀僋儖僞僀儉偼侾侽値倱偲偄偆偙偲偵側傝傑偡丅

偄傗偄傗偄傗丅

偝偡偑偵崱搙偙偦偼愨懳偵柍棟偱偟傚偆丅

俙俽俇俠俇俀俀俆俇偺僇僞儘僌抣偼慜夞傕彂偒傑偟偨傛偆偵倂俼俬俿俤僷儖僗偺俴婜娫偺嵟彫抣偑係俆値倱丄僒僀僋儖僞僀儉偼俆俆値倱偱偡乮乵戞侾侾俉夞乶乯丅

崱夞偺侾侽侽俵俫倸偱偼僒僀僋儖僞僀儉偼僇僞儘僌抣偺侾俉亾丄倂俼俬俿俤僷儖僗暆偵偄偨偭偰偼側傫偲偨偭偨偺侾侾亾偱偡丅

崱搙偙偦杮摉偵帋偟偰傒傞傑偱傕側偄偲巚偄傑偟偨丅

偱傕偳偆側傞偺偐丄偪傚偄偲嫽枴傕偁傝傑偟偨丅

壓偼俵俤俵倂俼怣崋晹暘偺倁俫俢俴僾儘僌儔儉偱偡丅

--MEMWR

--

MWR<=cntrs or r_w or cntrH(15);

--

|

壓偼們値倲倰倱偵偮偄偰婰弎偟偰偄傞僾儘僌儔儉晹暘偱偡丅

cntrs<=clkwk2 when r_w='0' and trigon='1' else not IORD;

|

們値倲倰倱亙亖們倢倠倵倠俀偲偟偰偍偄偰俵倂俼亙亖們値倲倰倱側偳偲偟側偄偱偄偒側傝俵倂俼亙亖們倢倠倵倠俀偲偡傟偽傛偄偺偱偡偗傟偳丄偲傝偁偊偢偺僥僗僩偱偡偐傜傕偲偺僾儘僌儔儉傪昁梫嵟掅尷捈偡偩偗偵偟偨偨傔忋偺儕僗僩偺傛偆偵忕挿側僾儘僌儔儉偵側偭偰偄傑偡丅

偝偰丅

寢壥偼偳偆側偭偨偱偟傚偆偐丅

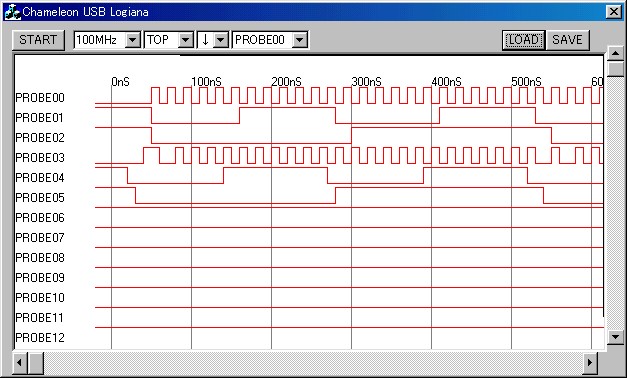

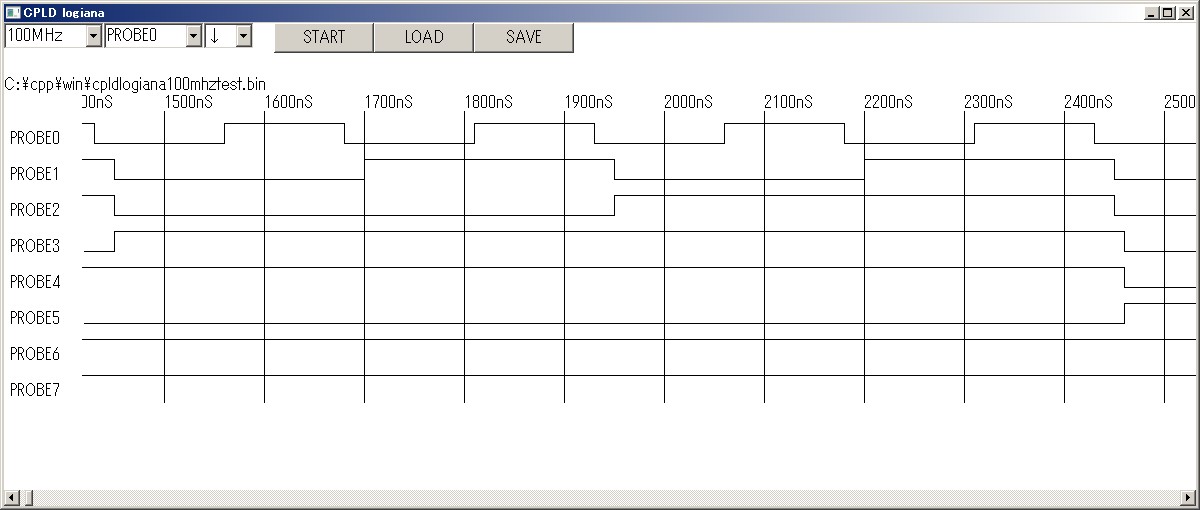

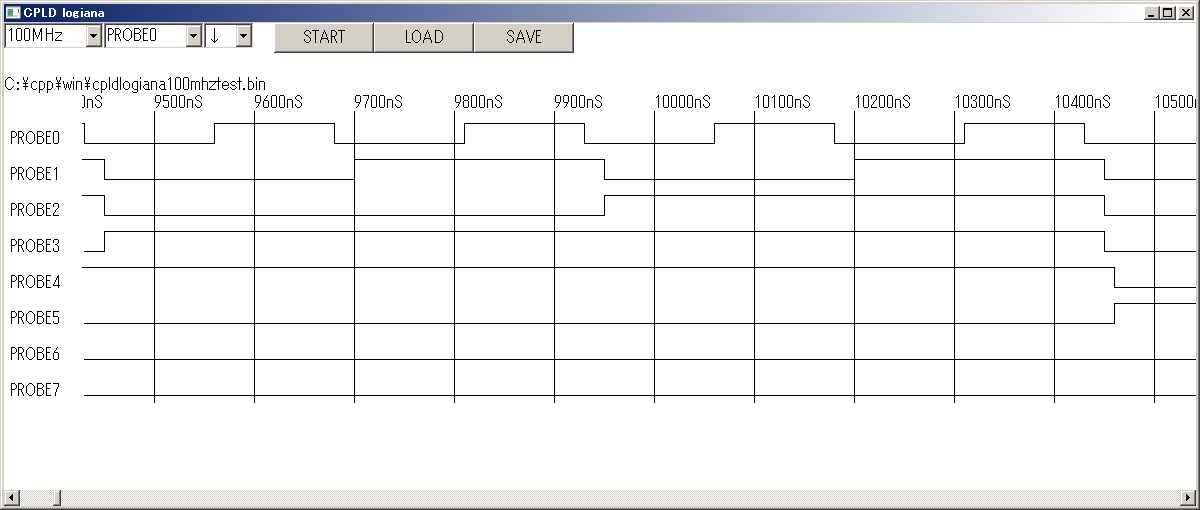

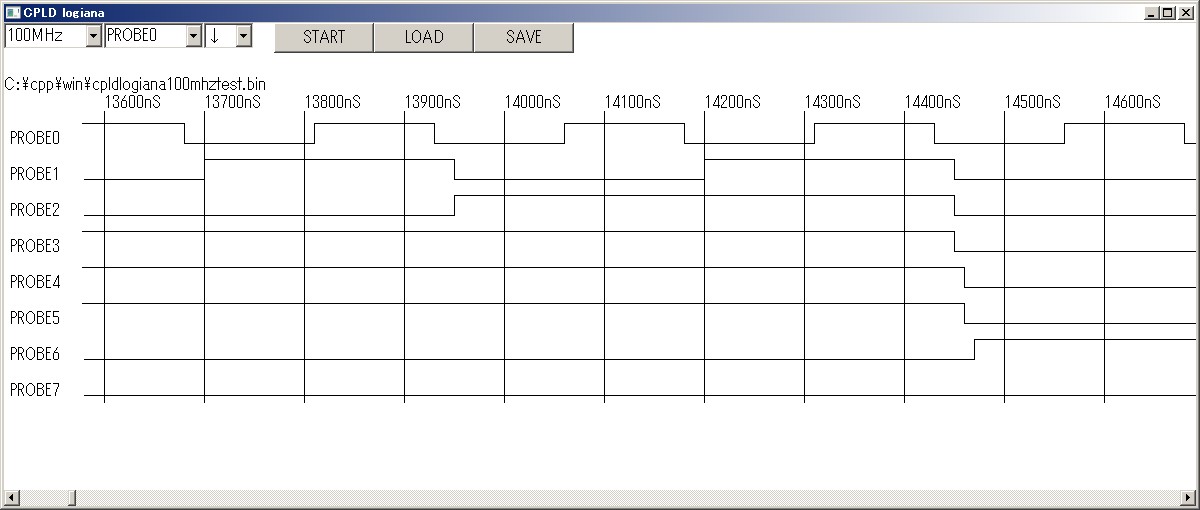

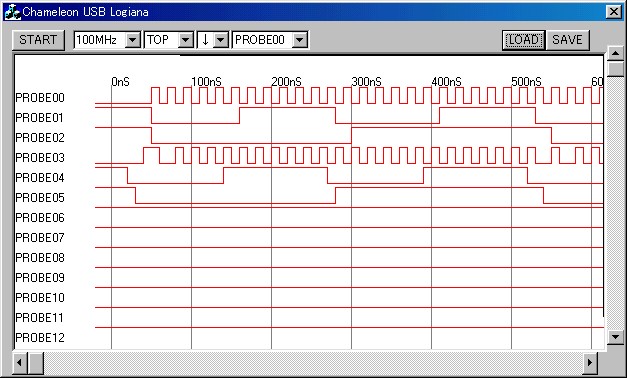

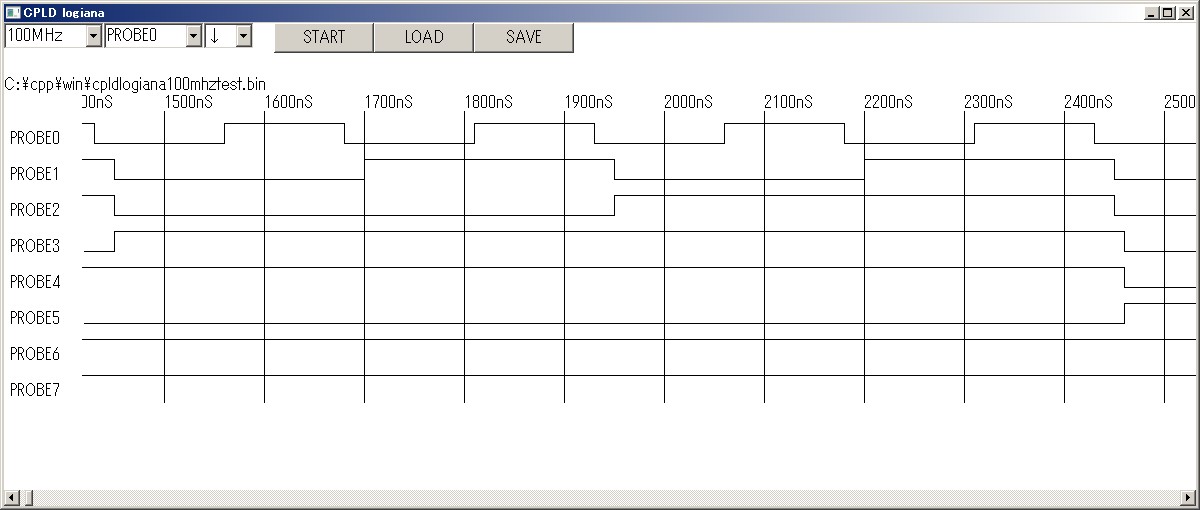

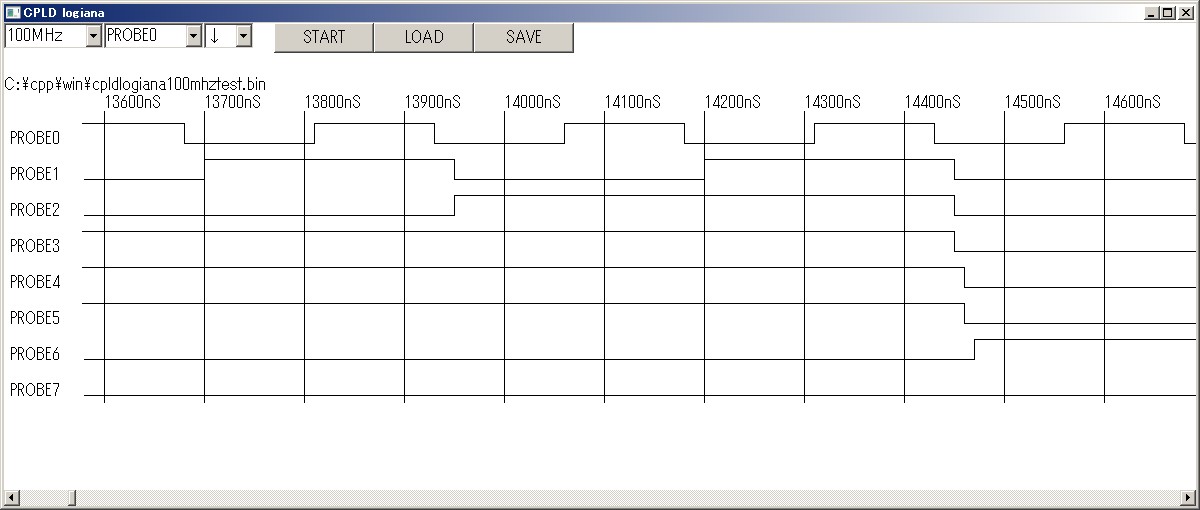

壓偼僒儞僾儕儞僌僋儘僢僋侾侽侽俵俫倸偱偺俠俹俴俢偐傜偺弌椡攇宍傪僇儊儗僆儞儘僕傾僫偱娤應偟偨攇宍偱偡丅

俹俼俷俛俤侽侽偼俠俹俴俢偐傜弌椡偝傟傞儊儌儕傾僪儗僗俙侽偱偡丅

僒儞僾儕儞僌儘僢僋偑侾侽侽俵俫倸偱偡偐傜侾侽値倱偛偲偵俫丄俴傪孞傝曉偟傑偡丅

偍偍丅

傑偲傕偵摦偄偰偄傞丠

俹俼俷俛俤侽侾偼俠俹俴俢儘僕傾僫偺俹俼俷俛俤侽偱儔僢僠偝傟偨僨乕僞乮係俵俫倸乯偱偡丅

俫丄俴偑侾俀俆値倱偺擖椡僨乕僞傪侾侽値倱偛偲偵儔僢僠偟偨僨乕僞偱偡丅

侾俀夞儔僢僠偡傞偛偲偵俆値倱偺偢傟偑弌傑偡丅

寁嶼忋偼俫丄俴偺偳偪傜偐偑侾俀侽値倱偱偳偪傜偐偑侾俁侽値倱偵側傞偼偢偱偡偑丄栤戣偼偝傜偵偦偺怣崋傪儔僢僠偟偰偄傞僇儊儗僆儞儘僕傾僫偺僋儘僢僋傕侾侽侽俵俫倸偩偲偄偆揰偱偡丅

偦偺偨傔傕偁偭偰偐忋偺夋憸偱偼侾侾侽値倱乣侾俁侽値倱偺攇宍偲偟偰昞帵偝傟偰偄傑偡丅

俹俼俷俛俤侽俀偼俠俹俴俢儘僕傾僫偺俹俼俷俛俤侾偱儔僢僠偝傟偨僨乕僞乮俀俵俫倸乯偱偡丅

俫丄俴偑俀俆侽値倱偺僨乕僞偱偡丅

偙偪傜偼俴丄俫偲傕偵偪傚偆偳俀俆侽値倱偵側偭偰偄傑偡丅

偦偟偰俹俼俷俛俤侽俁偑拲栚偺俵俤俵倂俼偱偡丅

俴偑俆値倱丄俫偑俆値倱丄廃婜偼侾侽値倱側偺偱偡偑丅

偙傟偼偝偡偑偺僇儊儗僆儞儘僕傾僫偱傕柍棟偱偡丅

俴偑侾侽値倱偐俫偑侾侽値倱偐偺攇宍偵側偭偰偄傑偡丅

偲偒偳偒偦傟傕旘傫偱偟傑偄俀侽値倱暆偵側偭偰偄傞偲偙傠傕偁傝傑偡丅

俹俼俷俛俤侽係偼僋儘僢僋敪惗夞楬婎斅偺係俵俫倸弌椡怣崋偱偡丅

俠俹俴俢儘僕傾僫偺俹俼俷俛俤侽偱儔僢僠偝傟傞慜偺怣崋偱偡丅

俹俼俷俛俤侽係傪侾侽値倱偺僒儞僾儕儞僌僋儘僢僋偱儔僢僠偟偨怣崋偑俹俼俷俛俤侽侾偱偡丅

棟孅偲偟偰偼嵟戝偱侾侽値倱偺抶傟偑敪惗偡傞偼偢偱偡偑丄忋偵彂偒傑偟偨傛偆偵僇儊儗僆儞儘僕傾僫偺僋儘僢僋傕娭學偟偰偄傞偼偢偱俀侽値倱偺抶傟偲偟偰尒偊偰偄傞偲偙傠傕偁傝傑偡丅

俹俼俷俛俤侽俆偼僋儘僢僋敪惗夞楬婎斅偺俀俵俫倸弌椡怣崋偱偡丅

俠俹俴俢儘僕傾僫偺俹俼俷俛俤侾偱儔僢僠偝傟傞慜偺怣崋偱偡丅

俹俼俷俛俤侽俆傪侾侽値倱偺僒儞僾儕儞僌僋儘僢僋偱儔僢僠偟偨怣崋偑俹俼俷俛俤侽俀偱偡丅

偙偪傜傕俀侽値倱偺抶傟偑偁傞傛偆偵尒偊偰偄傑偡丅

偦偟偰偄傛偄傛偱偡丅

俠俹俴俢儘僕傾僫偺僒儞僾儕儞僌僋儘僢僋侾侽侽俵俫倸偺攇宍偱偡丅

俹俼俷俛俤侽偑僋儘僢僋敪惗夞楬婎斅偐傜弌椡偝傟偨係俵俫倸偺攇宍偱偡丅

俫丄俴偺侾俀俆値倱傪侾侽値倱偱儔僢僠偟偰偄傑偡偐傜攇宍偵抁偄偲偙傠乮侾俀侽値倱乯偲挿偄偲偙傠乮侾俁侽値倱乯偑弌棃偰偄傑偡丅

忋偺夋憸偱偼偨傑偨傑俫亖侾俀侽値倱丄俴亖侾俁侽値倱偵側偭偰偄傞傛偆偱偡丅

偍偍丅

側傫偲侾侽侽俵俫倸僋儘僢僋偱傕僕儍僗僩寁嶼捠傝偠傖偁傝傑偣傫偐両

俹俼俷俛俤侾偼俀俵俫倸偱偡偐傜廃婜偼俆侽侽値倱偱偡丅

敿攇偼俀俆侽値倱偱偡偑偪傚偆偳偦偺捠傝偺攇宍偵側偭偰偄傑偡丅

偡偛偄両

俹俼俷俛俤俀偼侾俵俫倸偱偡偐傜廃婜偼侾侽侽侽値倱丄敿攇偼俆侽侽値倱偱偡丅

俹俼俷俛俤俀傕俫亖俆侽侽値倱丄俴亖俆侽侽値倱偱傄偭偨傝偱偡両

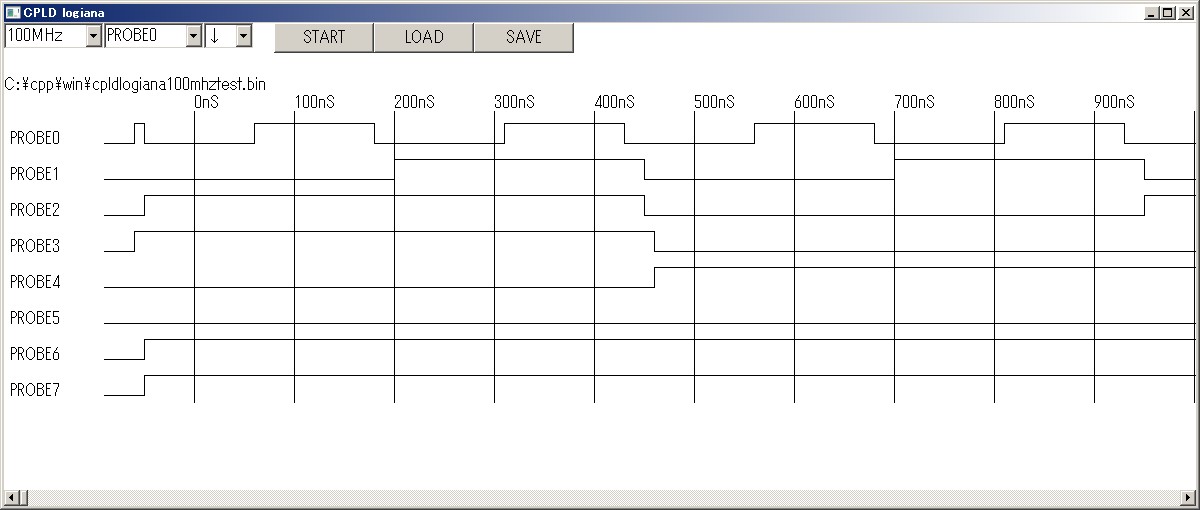

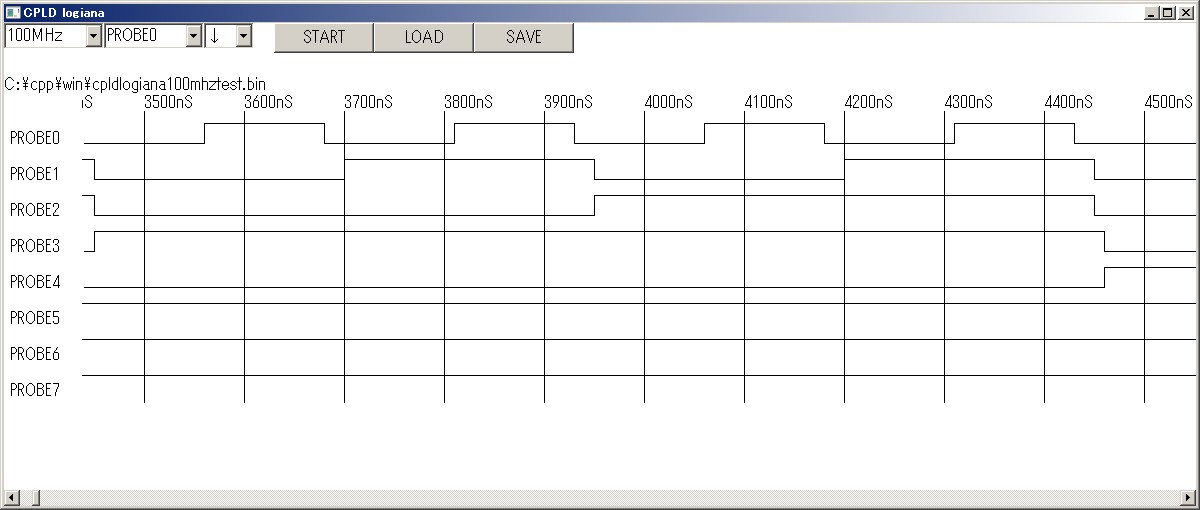

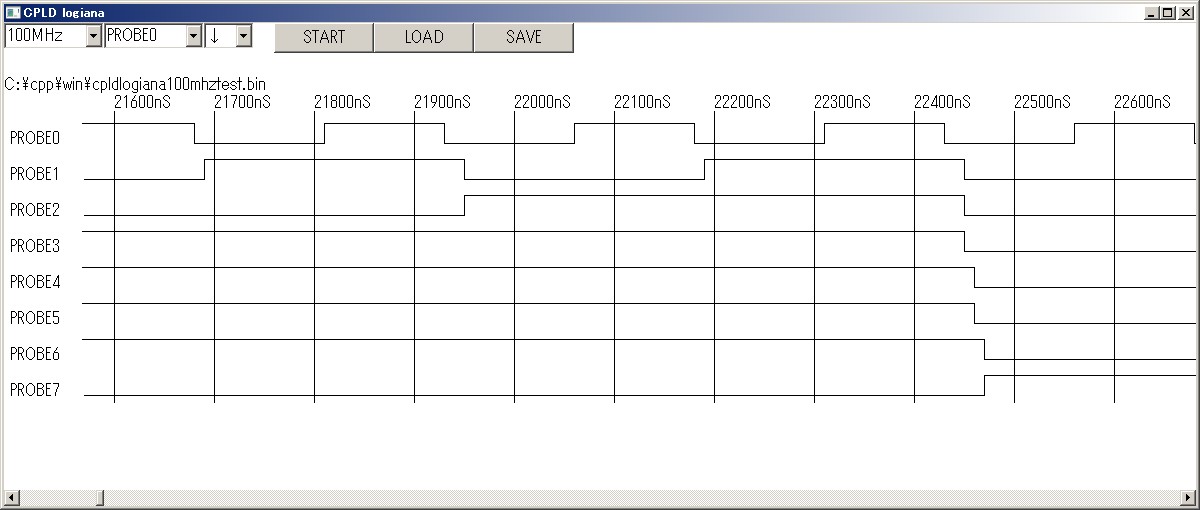

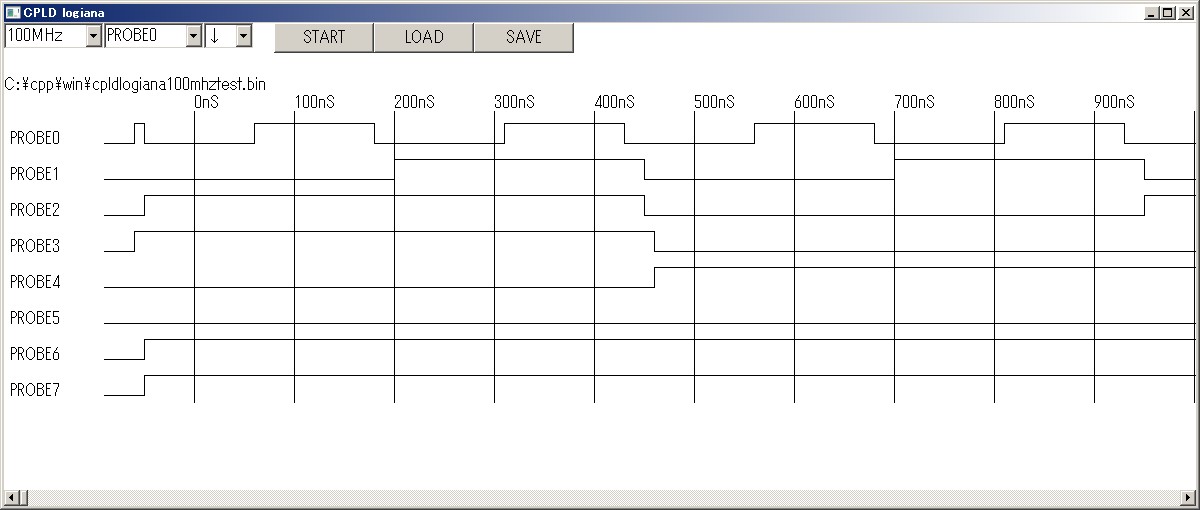

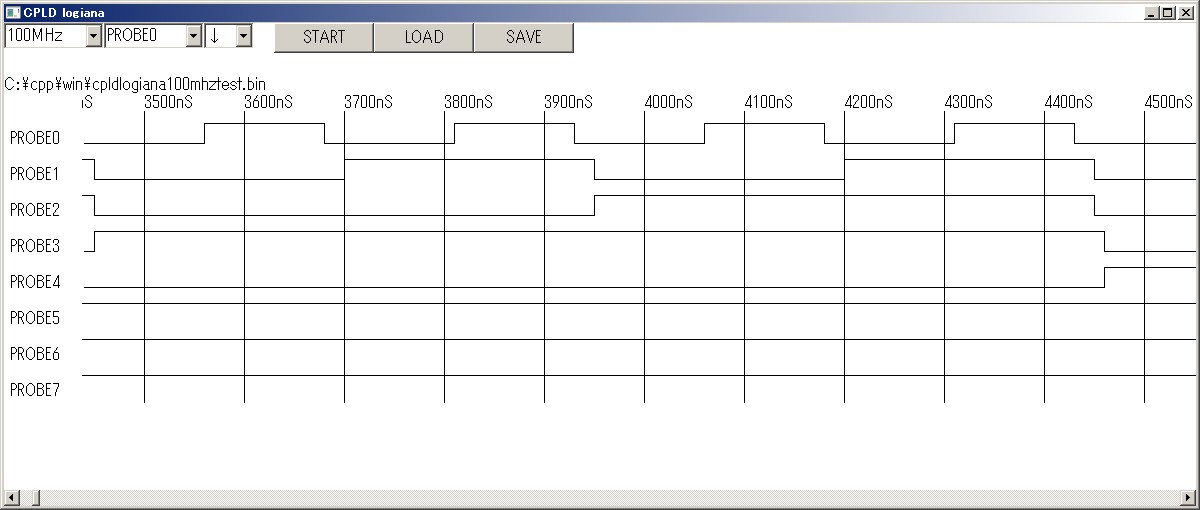

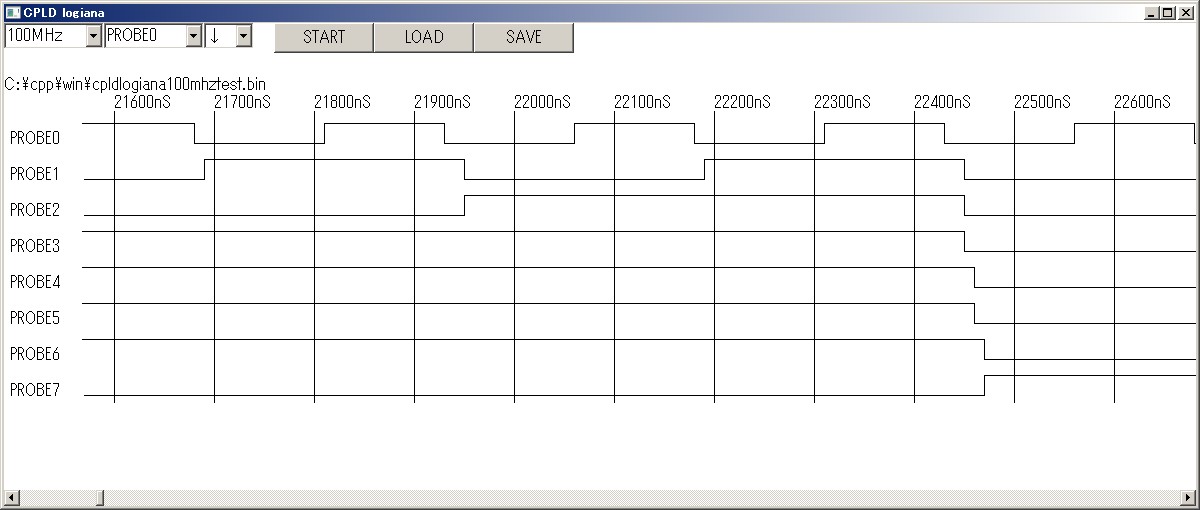

俹俼俷俛俤俁偐傜俹俼俷俛俤俈偼侾廃婜偺堦晹偟偐尒偊偰偄傑偣傫偑塃偵僗儔僀僪偟偰偄偗偽侾廃婜偺慡懱傪尒傞偙偲偑偱偒傞偼偢偱偡丅

俹俼俷俛俤俁偼係俇侽値倱偱棫偪壓偑偭偰偄傑偡丅

媡偵俹俼俷俛俤係偼偦偙偱棫偪忋偑偭偰偄傑偡丅

塃偵僗儔僀僪偟傑偟偨丅

俹俼俷俛俤俁偺俴嬫娫偑尒偊偰偄傑偡丅

侾係俆侽値倱偱棫偪忋偑偭偰偄傑偡丅

俹俼俷俛俤俁偼俆侽侽俲俫倸偱偡丅

廃婜偼俀侽侽侽値倱偱偡偐傜敿攇偼侾侽侽侽値倱偱偡丅

俴嬫娫偼侾係俆侽亅係俇侽亖俋俋侽値倱偱偡丅

侾侽値倱偼岆嵎偺斖埻偱偡偐傜寁嶼捠傝偱偡丅

塃偵僗儔僀僪偟傑偟偨丅

俹俼俷俛俤俁偺俫嬫娫偑尒偊偰偄傑偡丅

俀係俇侽値倱偱棫偪壓偑偭偰偄傑偡丅

俀係俇侽亅侾係俆侽亖侾侽侾侽値倱偱偡偐傜俫嬫娫傕寁嶼捠傝偱偡丅

俹俼俷俛俤係傕俀係俇侽値倱偱棫偪壓偑偭偰偄傑偡丅

棫偪忋偑傝偼係俇侽値倱偱偟偨丅

俹俼俷俛俤係偺俫嬫娫偼俀侽侽侽値倱偱偡丅

俹俼俷俛俤係偼俀俆侽俲俫倸偱偡丅

廃婜偼係侽侽侽値倱丄敿攇偼俀侽侽侽値倱偱偡偐傜寁嶼捠傝偱偡丅

俹俼俷俛俤俆傕俀係俇侽値倱偱棫偪忋偑偭偰偄傑偡丅

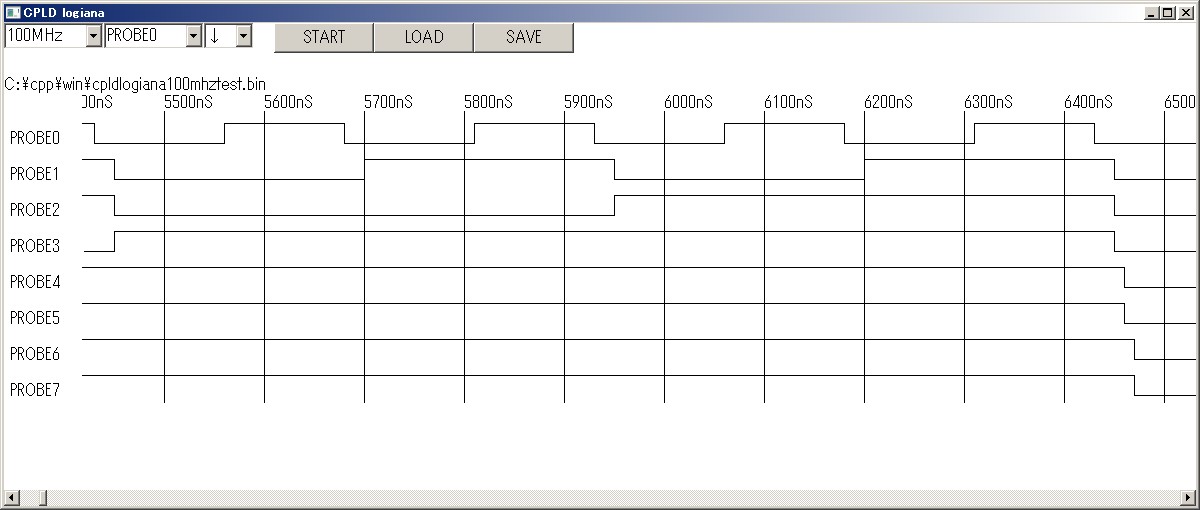

塃偵僗儔僀僪偟傑偟偨丅

俹俼俷俛俤係偑係係俇侽値倱偱棫偪忋偑偭偰偄傑偡丅

棫偪壓偑傝偼俀係俇侽値倱偱偟偨偐傜俹俼俷俛俤係偺俴嬫娫傕俀侽侽侽値倱偱寁嶼捠傝偱偡丅

塃偵僗儔僀僪偟傑偟偨丅

俹俼俷俛俤俆偑俇係俇侽値倱偱棫偪壓偑偭偰偄傑偡丅

棫偪忋偑傝偼俀係俇侽値倱偱偟偨偐傜俹俼俷俛俤俆偺俫嬫娫偼係侽侽侽値倱偱偡丅

俹俼俷俛俤俆偼侾俀俆俲俫倸偱偡偐傜侾廃婜偼俉侽侽侽値倱丄偦偺敿攇偼係侽侽侽値倱偱偡丅

偪傚偆偳寁嶼捠傝偱偡丅

俹俼俷俛俤俇偲俹俼俷俛俤俈偑俇係俈侽値倱偱棫偪壓偑偭偰偄傑偡丅

塃偵僗儔僀僪偟傑偟偨丅

俹俼俷俛俤俆偑侾侽係俇侽値倱偱棫偪忋偑偭偰偄傑偡丅

棫偪壓偑傝偼俇係俇侽値倱偱偟偨偐傜俹俼俷俛俤俆偺俴嬫娫傕係侽侽侽値倱偱寁嶼捠傝偱偡丅

塃偵僗儔僀僪偟傑偟偨丅

俹俼俷俛俤俇偑侾係係俈侽値倱偱棫偪忋偑偭偰偄傑偡丅

俹俼俷俛俤俇偼俇係俈侽値倱偺偲偙傠偱棫偪壓偑偭偰偄傑偟偨丅

俴嬫娫偼俉侽侽侽値倱偱偡丅

俹俼俷俛俤俇偼俇俀丏俆俲俫倸偱偡偐傜侾廃婜偼侾俇侽侽侽値倱丄偦偺敿攇偼俉侽侽侽値倱偱偡偐傜偪傚偆偳寁嶼捠傝偱偡丅

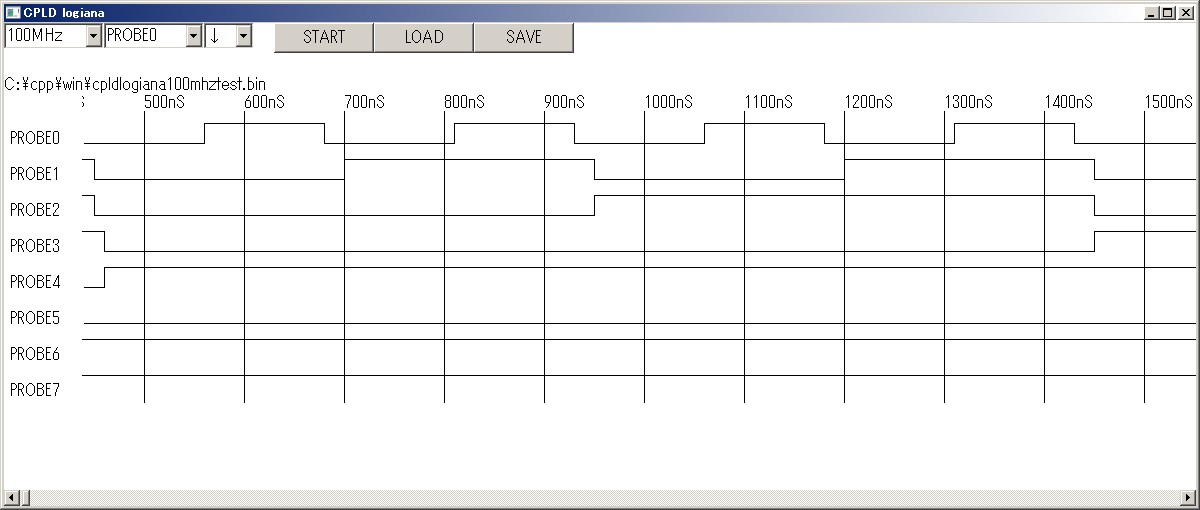

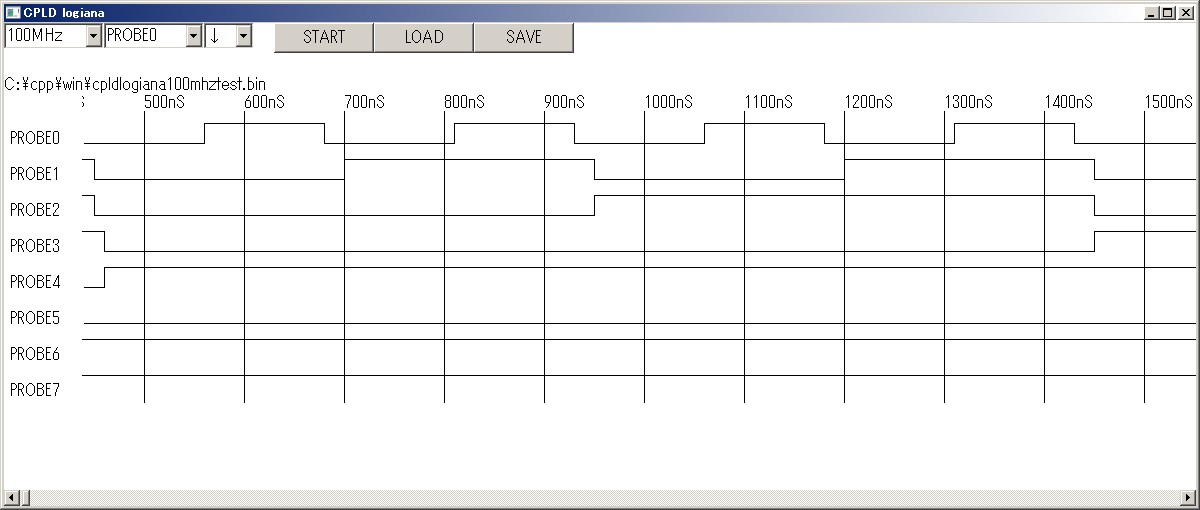

偝傜偵塃偵僗儔僀僪偟傑偟偨丅

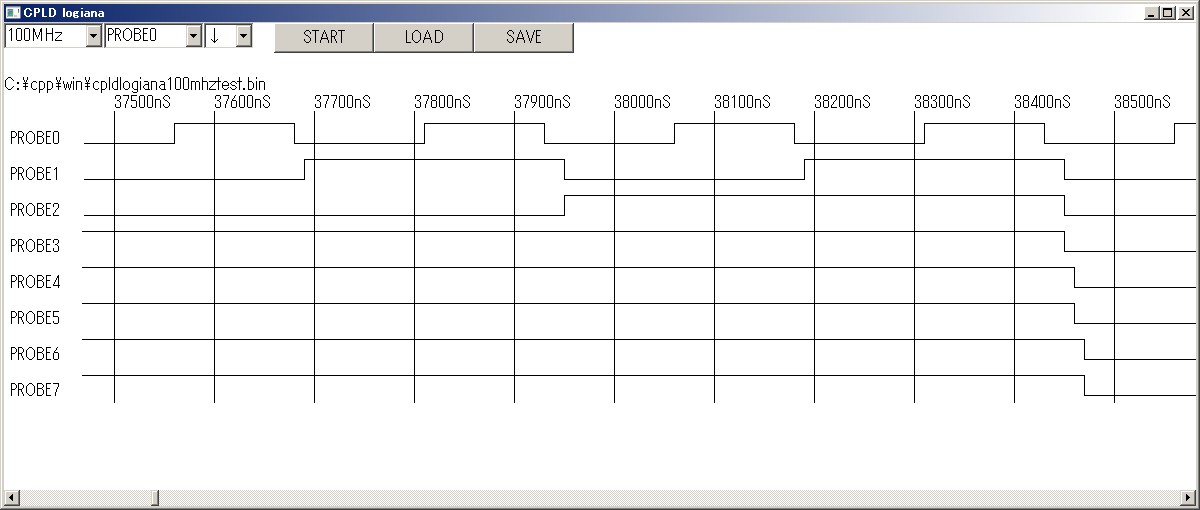

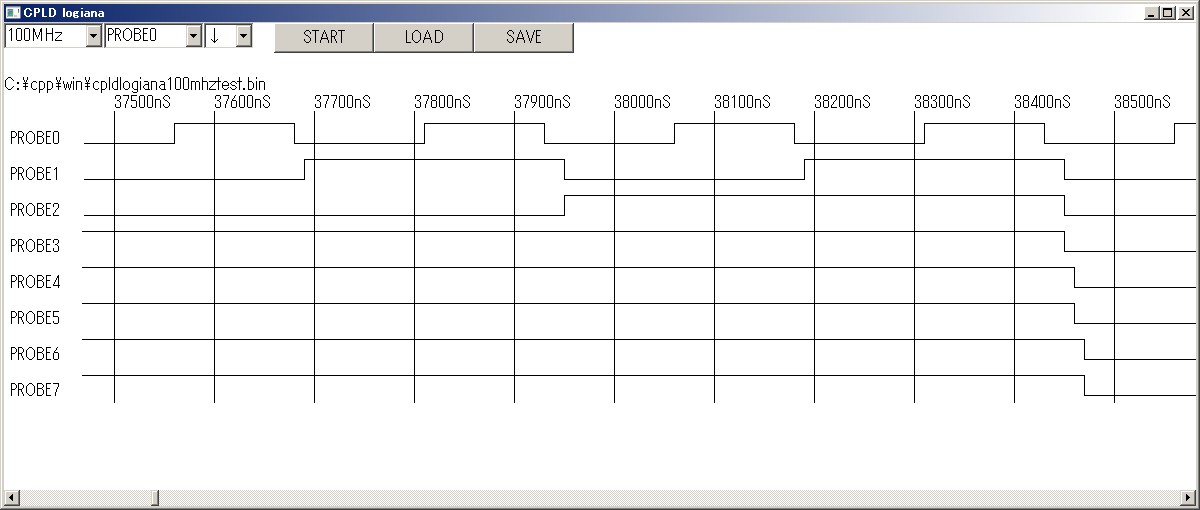

俹俼俷俛俤俇偑俀俀係俈侽値倱偱棫偪壓偑偭偰偄傑偡丅

偝偒傎偳偼侾係係俈侽値倱偱棫偪忋偑偭偰偄傑偡偐傜俫嬫娫傕俉侽侽侽値倱偱寁嶼捠傝偱偡丅

俹俼俷俛俤俈傕俀俀係俈侽値倱偱棫偪忋偑偭偰偄傑偡丅

俹俼俷俛俤俈偼俇係俈侽値倱偱棫偪壓偑偭偰偄傑偟偨偐傜俴嬫娫偼侾俇侽侽侽値倱偱偡丅

俹俼俷俛俤俈偼俁侾丏俀俆俲俫倸偱偡偐傜侾廃婜偼俁俀侽侽侽値倱丄偦偺敿攇偼侾俇侽侽侽値倱偱偡丅

偪傚偆偳寁嶼捠傝偱偡丅

偝傜偵塃偵僗儔僀僪偟傑偟偨丅

俹俼俷俛俤俈偑俁俉係俈侽値倱偱棫偪壓偑偭偰偄傑偡丅

偝偒傎偳偼俀俀係俈侽値倱偱棫偪忋偑偭偰偄傑偟偨偐傜俫嬫娫傕侾俇侽侽侽値倱偱偡丅

偙偪傜傕偪傚偆偳寁嶼捠傝偱偡丅

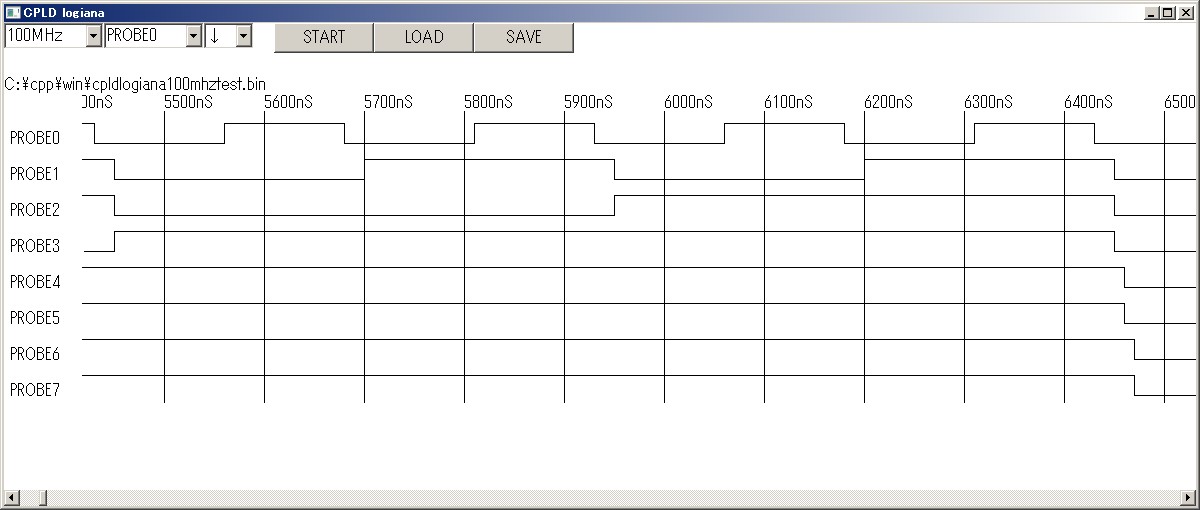

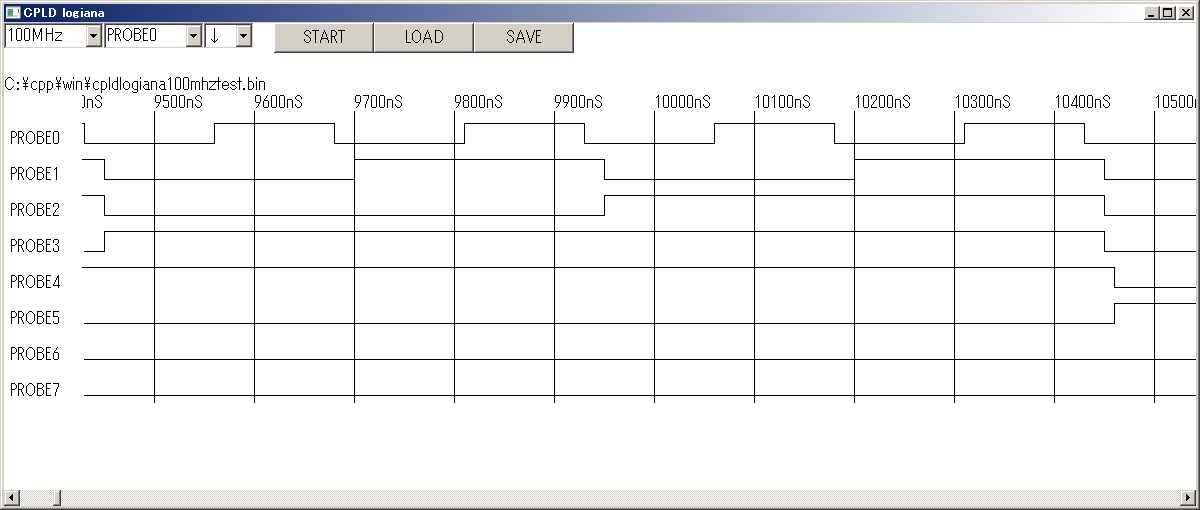

嵟屻傑偱僗儔僀僪偟傑偟偨丅

僨乕僞僄儞僪偼俁俀俈俁侽侽値倱偱偡丅

俁俀俈俁侽侽乛侾侽亖俁俀俈俁侽偱偡丅

俼俙俵偵偼俁俀俈俇俉屄偺僨乕僞偑彂偒崬傑傟傑偡偑僾儘僌儔儉偺搒崌偱幚嵺偵偦傟傪撉傒弌偟偰攇宍偲偟偰昞帵偡傞偺偼俁俀俈俁俆屄偱偡丅

嵟弶偺夋柺偱愭摢偺侽値倱偺慜偵俆僶僀僩暘偺昞帵僨乕僞偑偁傞偺偱偦傟傪壛嶼偡傞偲俁俀俈俁俆僶僀僩偵側傝傑偡丅

偪傚偆偳寁嶼捠傝偱偡丅

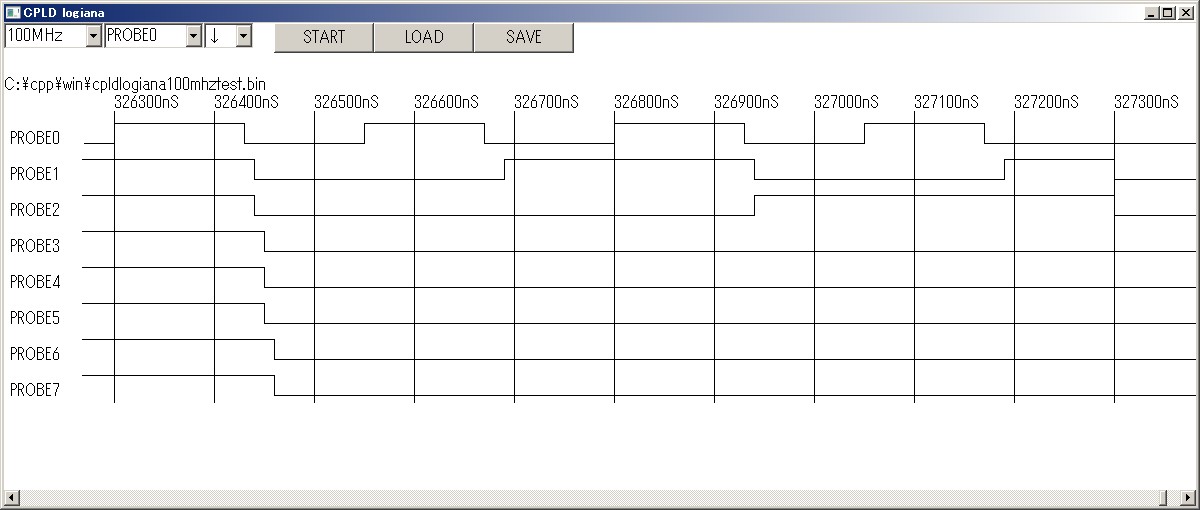

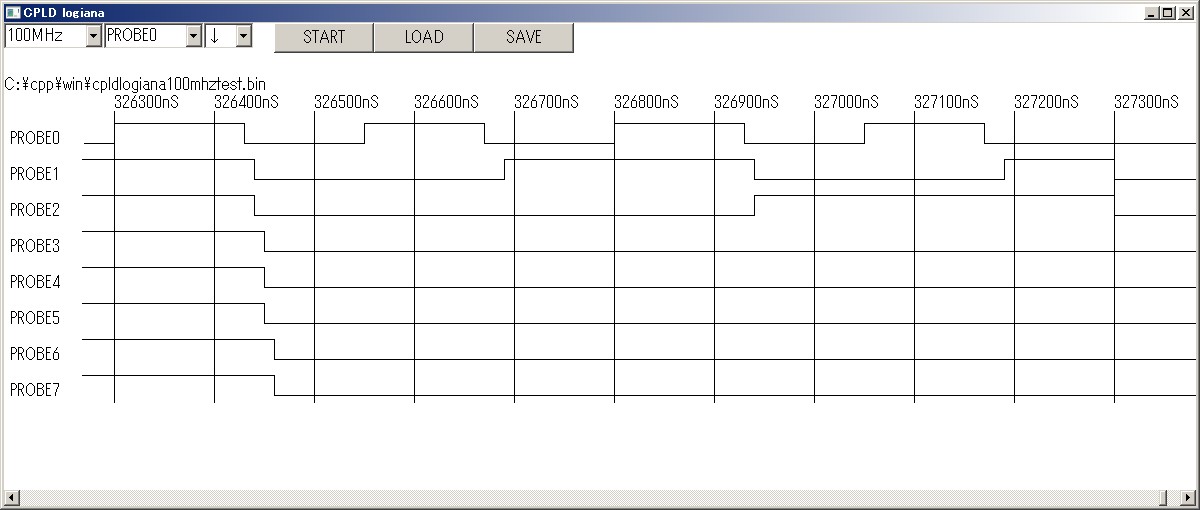

偝傜偵俁俀俇係侽侽値倱偁偨傝偺偲偙傠傪尒偰傒傑偡偲丅

俹俼俷俛俤侾偲俹俼俷俛俤俀偑俹俼俷俛俤侽偵侾侽値倱抶傟偰棫偪壓偑偭偰偄傑偡丅

俹俼俷俛俤俁乣俹俼俷俛俤俆偼偝傜偵偦傟偵侾侽値倱抶傟偰棫偪壓偑偭偰偄傑偡丅

偦偟偰俹俼俷俛俤俇偲俹俼俷俛俤俈偑偝傜偵偦傟偵侾侽値倱抶傟偰棫偪壓偑偭偰偄傑偡丅

偙偺偲偙傠側偳偼僋儘僢僋敪惗夞楬偐傜偺弌椡偑僶僀僫儕僇僂儞僞偐傜偺弌椡偺偨傔彮偟偢偮抶墑偡傞條巕傪偦偺傑傑懆偊偰偄傞傛偆偱偡丅

偄傗偁丅

偡偛偄両

慜夞偼俆侽俵俫倸偱僥僗僩傪偟傑偟偨丅

偦偺寢壥偼傑偝偵乽嬃堎揑乿側傕偺偱偟偨丅

崱夞偼偦傟偙偦傑偝偐偺傑偝偐偺侾侽侽俵俫倸偱偡丅

偙傟偼傕偆嬃堎揑側傫偰傕傫偠傖偁傝傑偣傫丅

偁傝偊側偄偙偲偑婲偒偨偲偄偆傋偒偱偁傝傑偟傚偆丅

崱偼偪傚偭偲嫽暠偟偰偍傝傑偡丅

惓忢側敾抐偑偱偒傞忬懺偱偼偁傝傑偣傫丅

傑傑丅

偙偙偼偲偵偐偔棊偪拝偄偰丅

偦偆偦偆丅

傑偢偼嬥敒偱姡攖両偱偡丅

俠俹俴俢擖栧両乵戞侾俀俁夞乶

俀侽俀俀丏侾丏侾俉倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞