昗弨俿俿俴偩偗乮両乯偱CPU傪偮偔傠偆両乮慻棫偰僉僢僩偱偡両乯

(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞俁俈侾夞乶

仠偳偙偑愝寁儈僗側偺偐丠

慜夞偺廔傢傝偺偲偙傠偱丄乽偍偽偐側愝寁儈僗乿偲彂偒傑偟偨丅

僸僎偺弌傞夞楬偼懠偵傕偁傝傑偟偨丅

偦偆偱偡丅儅僔儞僋儘僢僋偺弌椡夞楬偱偡乮乵戞侾係係夞乶乯丅

偱傕偙偺偲偒偵偼丄乽偍偽偐側愝寁儈僗乿偩偲偼彂偒傑偣傫偱偟偨丅

偄偗偟傖偁偟傖偁偲乽僐儞僨儞僒偱偮傇偣偽傛偄乿偲暯婥偱彂偄偰偄偨偺偱偡傛偹丅

暯婥偳偙傠偠傖偁傝傑偣傫丅

乵戞俁俇係夞乶偲傕側傞偲丄傕偆姰慡偵嫃捈傝偱偡丅

乽抶傟偨偭偰偄偄乿乽僸僎側偳僣僽偟偰偟傑偊偽偄偄乿傕偆偟偭偐傝偲嫃捈偭偰偄傑偡丅

偦傟偑崱夞偼堦揮偟偰乽偍偽偐側愝寁儈僗乿偱偡丅

庱旜堦娧偟偰偄傑偣傫偹偉丅

傑丄偦偙偑婡夿偲恖娫偲偑堘偆偲偙傠偱偡丅恖側偳偼傕偲傕偲柕弬偟偨懚嵼側偺偱偡丅

偲丄傑偁丄偦傟偼忕択偱偡丅

乵戞俁俇侽夞乶偱丄俀俆擭慜偵巹偑乽僩儔儞僕僗僞媄弍乿乮俠俻弌斉幮乯偵楢嵹偟偨偲偒偺婰帠傪堷梡偟偰丄乽俀俆擭慜傕崱傕愝寁偵懳偡傞巹偺峫偊曽偼曄傢偭偰偄傑偣傫乿丄側偳偲傛偣偽偄偄偺偵戝尒摼傪愗偭偰丄

乽側傫偨偭偰僨僕僞儖夞楬側傫偩偐傜丄梋桾偼偨偭傉傝廫暘偡偓傞偔傜偄偁傞偺偩偐傜丄岆摦嶌側偳偡傞傢偗偑側偄丅

岆摦嶌側傫偐偟偨傜丄偦傝傖偁丄偁側偨丅傛偭傐偳愝寁偵傾僫偑偁傞偺偱偡傛丅乿

側傫偰儂儔傕儂儔丄戝朄梿傪悂偄偰丄偛挌擩偵丄乽偁傫傑傝戝尒摼傪愗傞偲堷偭崬傒偑偮偐側偔側偭偰抪傪偐偔偺偑棊偪乿偭偰帺暘偱傕傢偐偭偰傞偠傖側偄偺丅

偦偺捠傝丅偟偭偐傝偲抪傪偐偄偰偟傑偄傑偟偨丅

偱傕偦偆偄偆偙偲側偺偱偡丅

帺暘偱傢偐偭偰偄偰丄偦偆偄偆夞楬傪慖戰偟偰丄偦偺偨傔偵乽傗傓傪摼偢乿弌偰偟傑偆僸僎傪僐儞僨儞僒偱偮傇偡偺偼丄抪偩偲偼巚偄傑偣傫丅懠偵夞旔嶔偑偁偭偰傕丄偁偊偰偙傟傪慖傇丄偲偄偆崻嫆偑偁傟偽丄傛偄偺偱偼偁傝傑偣傫偐丅

偦傟偼愝寁儈僗偱偼偁傝傑偣傫丅

偟偐偟丄崱夞偼僟儊偱偡丅偙傟偼丄偼偭偒傝尵偭偰丄偍偽偐丅

偳偙偑丄偍偽偐偐丠

偙偆偄偆偙偲偱偡丅

偩偄偨偄倰倕倗倂俼偑抶傟傞偙偲偼偼偠傔偐傜傢偐偭偰偄傑偟偨丅

峀戝側婎斅慡懱偵峀偑偭偨倰倕倗倂俼偺攝慄偺偁偪偙偪偐傜憲傜傟傞僆乕僾儞僐儗僋僞弌椡怣崋傪僾儖傾僢僾掞峈偱庴偗偰偄傞偺偱偡偐傜丄棫壓傝偼傑偁椙偄偗傟偳丄棫偪忋偑傝偵偮偄偰偼斶嶴側攇宍偵側傞偙偲偼傢偐偭偰偄傑偟偨丅

偦偺偙偲偵偮偄偰偼丄乵戞俈俀夞乶偱丄倰倕倗倂俼偱偼偁傝傑偣傫偑乽倓俁乣倓侽偺棫偪忋偑傝偑抶偄乿偲彂偄偰偄傑偡丅彂偄偰偄傞偩偗偱偼側偔偰丄僆僔儘僗僐乕僾偱娤應偟偨攇宍幨恀傑偱偮偗偰偄傑偡丅

偦偟偰偦偺偮偓偺乵戞俈俁夞乶偱偼乽偙偺抶傟偼俀侽侽値倱偔傜偄偼偁傝偦偆乿側偺偱乽俠俹倀僋儘僢僋偼俀俵俫倸偵棊偲偡偟偐側偄乿偲彂偄偰偄傑偡丅

偦偙傑偱傢偐偭偰偄傞偺偱偡偐傜丄摉慠偺偙偲側偑傜丄倰倕倗倂俼偺抶傟傕摢偵偟偭偐傝擖偭偰偄偨偼偢側偺偱偡偑乧丅

傑偭偨偔丄偆偐偮偱偟偨丅

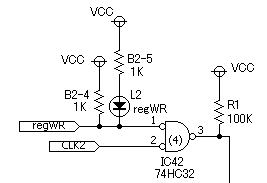

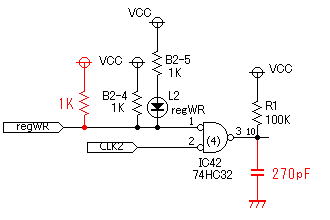

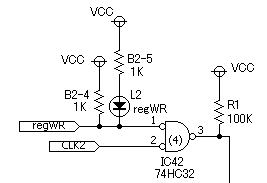

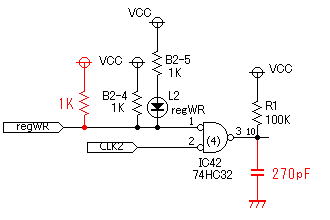

俼倃偺僞僀儈儞僌僠儍乕僩傪倰倕倗倂俼傪拞怱偵偟偰傾儗儞僕偟偨偺偑壓恾偱偡丅

倰倕倗倂俼怣崋偼弌椡僨乕僞乮俢侽亅俢俈丄倝俛侽亅倝俛俈乯偺傎傏恀拞偵偁偭偰丄偟偐傕棫偪忋偑傝偺抶傟傪堄幆偟偰丄慜傛傝傕屻傠傪戝偒偔偁偗偰偄傑偡丅

俠俴俲偼俀俵俫倸偱偡偐傜慜偑俀俆侽値倱丄屻傠偵偼俆侽侽値倱偺梋桾偑偁傞偙偲偵側傝傑偡丅

偙傟偼俼倃偺僞僀儈儞僌僠儍乕僩側偺偱偡偑丄懠偺偳偺柦椷偱傕倰倕倗倂俼偺僞僀儈儞僌偼偙偺傛偆偵側偭偰偄傑偡丅

偳偆揮傫偩偭偰愨懳偵岆摦嶌側偳偟側偄偼偢偺夞楬偩偭偨偺偱偡偑乧丅

晛捠偺夞楬偼偦傟偱椙偐偭偨偺偱偡丅

俼倃傕丄晛捠偵幚峴偝傟偰偄傞乮偮傑傝忦審偑惉棫偟偰丄晛捠偺俼俤俿偲摨偠傛偆偵儕僞乕儞偡傞乯尷傝偵偍偄偰偼丄慡偔栤戣偼側偐偭偨偺偱偡丅

偲偙傠偑俼倃偼丄忦審偑惉棫偟側偄応崌偵偼丄搑拞偱幚峴傪拞巭偟偰偟傑偄傑偡丅

嬶懱揑偵偼俿係偺偼偠傔偺偲偙傠偱俵們倢倰僷儖僗傪弌椡偟偰丄儅僔儞僋儘僢僋僇僂儞僞傪僋儕傾偟偰偟傑偄傑偡丅

偙偙偵棊偲偟寠偑偁傝傑偟偨丅

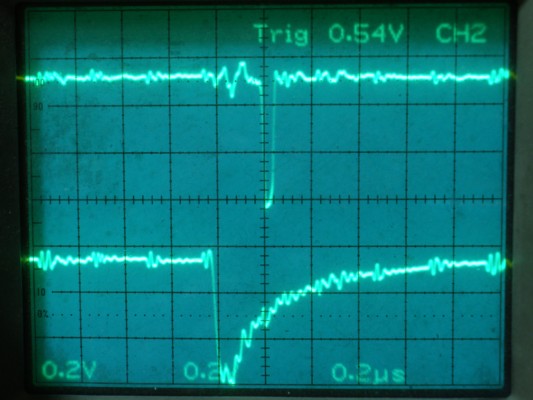

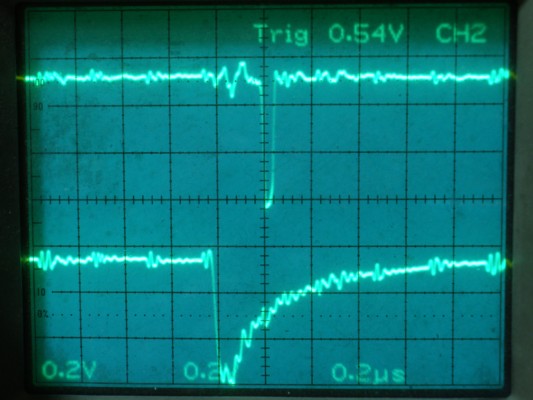

慜夞偵傕偍尒偣偟偨丄儘僕傾僫偺攇宍傪傕偲偵偟偨恾偱偡丅

堦斣壓丄俿係偺偲偒偵俵們倢倰偑弌椡偝傟傑偡偑丄乽偦傟偼偡偱偵俿係偑弌偝傟偨偁偲側偺偱乿丄偦偟偰偝傜偵偦傟偵抶墑偑壛傢傝傑偡偐傜丄俿係偼偁傞掱搙偺婜娫偼弌椡偝傟偰偟傑偆偙偲偵側傝傑偡乮侾侽侽値倱偖傜偄乯丅

偡傞偲偦偺婜娫偼倰倕倗倂俼乮俬俠係俀偺倫倝値侾擖椡怣崋乯傕傾僋僥傿僽偵側傝傑偡丅

偟偐偟丄偙偺倰倕倗倂俼偼俬俠係俀偱僎乕僩偝傟偰偄傞偨傔丄倫倝値俀偵擖椡偝傟傞俠俴俲俀偑俴偺婜娫偱側偄偲丄儗僕僗僞傊偺彂偒崬傒怣崋偲偟偰弌椡偝傟傞偙偲偼偁傝傑偣傫丅

傕偟傕丄倰倕倗倂俼偺棫偪忋偑傝偑俠俴俲俀偑俴偵側傞傛傝傕憗偗傟偽丄偱偡丅

倰倕倗倂俼偺攇宍偱偡丅

壓乮俠俫俀乯偑倰倕倗倂俼乮俬俠係俀偺倫倝値侾擖椡怣崋乯偱丄忋乮俠俫侾乯偑岆弌椡偝傟偨俬俠係俀偺倫倝俁偐傜偺弌椡怣崋偱偡丅

偪側傒偵偙偺僞僀儈儞僌偼偐側傝儚乕僗僩側傕偺偱丄偄偮傕偙偺傛偆偵側傞偲偼尷傝傑偣傫丅

僆僔儘偱懆偊傛偆偲偟偰僾儘僌儔儉傪儖乕僾偝偣偰傒偨偺偱偡偑丄側偐側偐曔傑偊傜傟傑偣傫偱偟偨丅

俬俠係俀偺倫倝値侾偵僆僔儘偺僾儘乕僽傪偁偰偰丄偝傜偵偪傚偄偲亄傾儖僼傽偟偰傗偭偲昁偢弌椡偝傟傞忬懺偵側傝傑偟偨丅

偲偙傠偱丄夞楬偑娫堘偭偰偄傞丄偲偄偆偐傜偵偼丄偱偼偳偆偄偆夞楬偵偡傋偒偩偭偨偺偐丄偲偄偆栤戣偵側傞偺偱偡偑丄偦傟偵偮偄偰偼丄傑偨師夞偵彂偔偙偲偵偄偨偟傑偡丅

偍庤帩偪偺俵倄俠俹倀俉侽偑丄俼倃偱岆摦嶌偡傞偐偳偆偐偺僥僗僩偵偮偄偰丄傑偢愢柧傪偄偨偟傑偡丅

俿俲俉侽夞楬偺僉乕偐傜擖椡偟偰丄師偺僾儘僌儔儉傪彂偄偰偔偩偝偄丅

俉侽侽侽偐傜偱傕俋侽侽侽偐傜偱傕椙偄偺偱偡偑棟桼偑偁偭偰丄偐側傜偢壓俀寘偑侽侽偺傾僪儗僗偐傜彂偄偰偔偩偝偄丅

俉侽侽侽丂俁俤俥俥丂丂丂俵倁俬丂俙丆俥俥

俉侽侽俀丂俛俈丂丂丂丂丂俷俼俙丂俙

俉侽侽俁丂俠俉丂丂丂丂丂俼倅

俉侽侽係丂俠俁侽俁俉侽丂俰俵俹丂亹俉侽侽俁

彂偒廔傢偭偨傜俉侽侽侽偐傜俼倀俶偝偣偰傒偰偔偩偝偄丅

朶憱偟偨傜丄懳嶔偑昁梫偱偡丅

傕偟朶憱偟側偄偱儖乕僾傪幚峴偟懕偗偨傜丄偲傝偁偊偢偼岆摦嶌偣偢偵摦偄偰偄傑偡丅

朶憱偟側偄偱惓偟偔摦偄偰偄傞応崌偵偼丄俠俹倀偼俉侽侽俁偐傜俉侽侽俈偺娫傪孞傝曉偟幚峴偟懕偗傑偡偐傜丄俹俠乮僾儘僌儔儉僇僂儞僞乯偺俴俤俢偼侾侽侽侽侽侽侽侽丂侽侽侽侽侽侾侾侾偺傛偆偵揰摂偟偰尒偊傑偡丅

偙偺応崌偵偼丄偲傝偁偊偢偼懳嶔偼偟側偔偰傕傛偄偺偱偡偑丄側偵偟傠偐側傝偓傝偓傝偺僞僀儈儞僌偩偲巚偄傑偡偐傜丄婥壏側偳偺曄壔偵傛偭偰丄偄偮岆摦嶌偑弌偰偔傞偐傢偐傝傑偣傫丅

偱偒偨傜偍庤悢偱怽偟栿偁傝傑偣傫偑丄岆摦嶌杊巭偺懳嶔傪偟偰偄偨偩偄偨傎偆偑傛傠偟偄偐偲巚偄傑偡丅

偲偙傠偱丄傕偟岆摦嶌偟偰偄偨傜丄偺榖側偺偱偡偑乧丅

壓偺傛偆偵丄俉侽侽係埲壓傪彂偒姺偊偰丄傕偆堦搙幚峴偟偰傒偰偔偩偝偄丅

俉侽侽侽丂俁俤俥俥丂丂丂俵倁俬丂俙丆俥俥

俉侽侽俀丂俛俈丂丂丂丂丂俷俼俙丂俙

俉侽侽俁丂俠俉丂丂丂丂丂俼倅

俉侽侽係丂侽侽丂丂丂丂丂俶俷俹

俉侽侽俆丂俠俁侽俁俉侽丂俰俵俹丂亹俉侽侽俁

崱搙偼岆摦嶌偟側偔側偭偨偼偢偱偡乮側偤側偺偐偵偮偄偰偼丄師夞偵愢柧偄偨偟傑偡乯丅

仠僸僎戅帯偺懳嶔偱偡

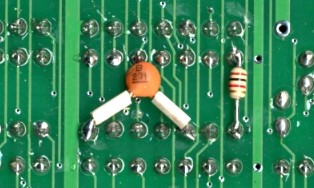

弌偰偟傑偭偨僸僎傪偮傇偡偵偼俀俈侽倫俥偺僐儞僨儞僒傪俬俠係俀偺倫倝値俁偲俧俶俢乮倫倝値俈乯偲偺娫偵庢傝晅偗傑偡丅

傕偆傂偲偮丄弌側偔偡傞偨傔偺懳嶔偲偟偰丄俬俠係俀偺倫倝値侾偲倁們們乮倫倝値侾係乯偲偺娫偵侾俲兌偺掞峈傪庢傝晅偗傑偡丅偙傟偼傕偲偺僾儖傾僢僾掞峈乮侾俲兌乯偵丄偝傜偵暲楍偵侾俲兌傪捛壛偡傞偙偲偱丄僾儖傾僢僾掞峈傪俆侽侽兌憡摉偵偡傞傕偺偱偡丅偙偆偡傞偙偲偱丄倰倕倗倂俼擖椡怣崋偺棫偪忋偑傝傪僗僺乕僪傾僢僾偡傞偙偲偑偱偒傑偡丅

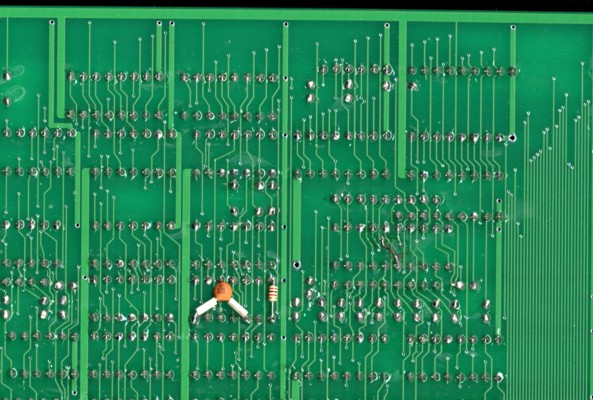

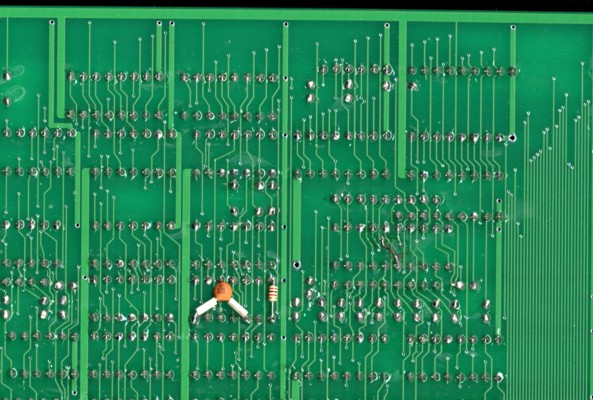

俵倄俠俹倀俉侽偺婎斅棤偺幨恀偱偡丅

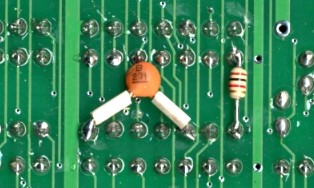

俬俠係俀乮俈係俫俠俁俀乯偺倫倝値侾偲倫倝値侾係偲偺娫偵侾俲兌偺掞峈傪庢傝晅偗丄倫倝値俁偲倫倝値俈偺娫偵俀俈侽倫俥僐儞僨儞僒傪庢傝晅偗傑偡丅

傕偆彮偟奼戝偟偰傒傑偟偨丅

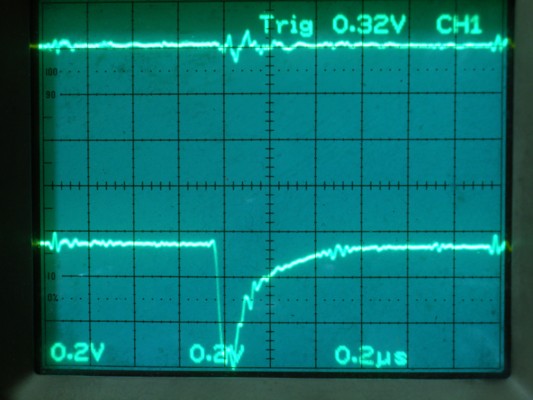

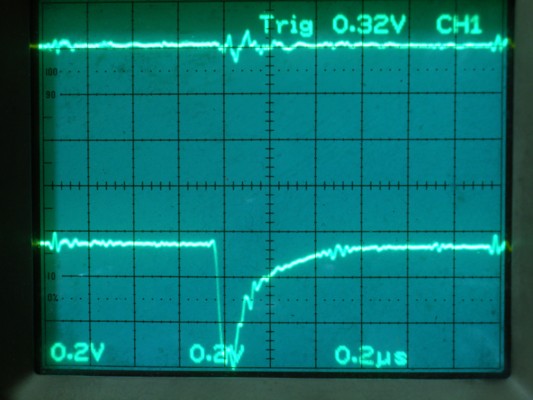

掞峈傪庢傝晅偗偨偁偲偺丄俬俠係俀偺倫倝n侾擖椡偲倫倝値俁弌椡怣崋偺攇宍幨恀偱偡丅

壓乮俠俫俀乯偑倰倕倗倂俼乮俬俠係俀偺倫倝値1擖椡乯偱忋乮俠俫侾乯偑倫倝値俁偺弌椡偱偡丅

倰倕倗倂俼怣崋偺棫偪忋偑傝偑憗偔側傝丄僸僎偼姰慡偵徚偊偰偄傑偡丅

乮師夞偵懕偒傑偡乯

俀侽侽俋丏侾侽丏俀俇倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞