(儂儞僩偼俈係俫俠丄俠俵俷俽側傫偩偗偳乧乯

乵戞俁俋侾夞乶

仠倰倕倗倂俼偺僥僗僩夞楬偺愢柧偱偡

倰倕倗倂俼偺僥僗僩夞楬偺攇宍幨恀傪偁傜偨傔偰嶣傝捈偟傑偟偨丅

愢柧傪偡傞偨傔偵丄傕偆堦搙夞楬恾傪偍尒偣偟傑偡丅

俈係俫俠侽俆偺倫倝値侾俀偑丄柦椷夞楬偐傜弌椡偝傟傞倰倕倗倂俼怣崋偺儌僨儖偱偡丅

弌椡偝傟傞倰倕倗倂俼怣崋偼丄俿値僋儘僢僋偵摨婜偡傞僞僀儈儞僌偱弌椡偝傟傑偡丅

僥僗僩夞楬偱偡偐傜丄偰偒偲偆側俿値怣崋偲偟偰丄偙偙偱偼俿係傪慖傃丄偦偺婜娫偵弌椡偟偰偄傑偡丅

倰倕倗倂俼怣崋偼暋悢偺柦椷夞楬偐傜弌椡偝傟傑偡偐傜丄僆乕僾儞僐儗僋僞弌椡偵側傝傑偡丅

偦偺倰倕倗倂俼怣崋傪庴偗偰偄傞偺偑俈係俫俠侽係偺倫倝値侾俁偱偡丅

偙偺俈係俫俠侽係偺弌椡傪傕偲偵偟偰丄奺儗僕僗僞傊偺乽傎傫偲偆偺倰倕倗倂俼怣崋乿傪嶌傝傑偡丅

幚嵺偵奺儗僕僗僞偵憲傜傟傞倰倕倗倂俼傗儊儌儕偵懳偡傞俵俤俵倂俼怣崋偼丄偙偺僥僗僩夞楬偱偼丄俈係俫俠俈係偺俻丵弌椡怣崋偱偡丅

幨恀傪偍尒偣偡傞慜偵丄僞僀儈儞僌僠儍乕僩偱愢柧傪偟傑偡丅

倰倕倗倂俼乮倝値乯偼俿値怣崋偺偼偠傔偵弌椡乮伀乯偝傟丄偦偺婜娫偺廔傢傝偵棫偪忋偑傝乮仾乯傑偡偑丄僆乕僾儞僐儗僋僞弌椡側偺偱棫偪忋偑傝偼備偭偔傝偵側傝傑偡丅

偙偺攇宍傪惍宍偡傞偨傔偵俈係俫俠俈係傪巊偄傑偡丅

俠俴俷俠俲乮俀俵俫倸乯傪斀揮偟偨僋儘僢僋傪俈係俫俠俈係偺俠俲擖椡偵偟傑偡丅

倰倕倗倂俼乮倝値乯偼僀儞僶乕僩偝傟偰俈係俫俠俈係偺俠俴俼偲俢偵擖椡偝傟傑偡偐傜丄偦偺婜娫偩偗俈係俫俠俈係偺俻丄俻丵弌椡偑擻摦偵側傝傑偡丅偦傟埲奜偺婜娫偼俻丵偼俫偱偡乮俠俴俼亖俴側偺偱乯丅

倰倕倗倂俼乮倝値乯偑棫偪壓偑偭偰偐傜敿僋儘僢僋抶傟偰丄俈係俫俠俈係偺俠俲擖椡偑仾偵側傝傑偡丅

偙偺僞僀儈儞僌偱丄俈係俫俠俈係偺俻丵偑俴偵側傝傑偡丅

偙傟偑倰倕倗倂俼乮倧倳倲乯丄俵俤俵倂俼偺棫偪壓傝偵側傝傑偡丅

僨乕僞僶僗傗傾僪儗僗僶僗偼俿値乮杮摉偼俵値乯偵摨婜偟偰傾僋僥傿僽偵側傝傑偡偐傜丄僨乕僞僶僗丄傾僪儗僗僶僗偑傾僋僥傿僽偵側偭偰偐傜俈係俫俠俈係偺俻丵偑俴偵側傞偲偒傑偱偵丄嵟戝偱俀俆侽値倱偺梋桾偑偱偒傑偡丅

倂俼怣崋偺棫偪壓傝偑栤戣偵側傞偺偼丄俵俤俵倂俼偩偗偱偡乮儗僕僗僞偼倂俼怣崋偺忋偑傝僄僢僕偱儔僢僠偝傟傞偑丄儊儌儕偼倂俼怣崋偑壓偑偭偨忬懺偱傾僪儗僗偑晄埨掕偱偁傞偲岆傑偭偨傾僪儗僗偵彂偒崬傑傟偰偟傑偆乯丅

偦偺夞旔偺偨傔偵丄嵟戝偱俀俆侽値倱偺梋桾偑偁傞偙偲偵側傝傑偡丅

偦偟偰倂俼怣崋偺棫偪忋偑傝偼丄倰倕倗倂俼乮倝値乯偺棫偪忋偑傝偲摨偠僞僀儈儞僌偵側傝傑偡丅

倰倕倗倂俼乮倝値乯傪僀儞僶乕僩偟偰俈係俫俠俈係偺俠俴俼擖椡偵偟偰偄傞偨傔丄倰倕倗倂俼乮倝値乯偑棫偪忋偑傞偲丄俈係俫俠俈係偺俻丄俻丵弌椡偑僋儕傾偝傟傞偺偱俻丵偮傑傝倰倕倗倂俼乮倧倳倲乯丄俵俤俵倂俼偑俫偵側傞偺偱偡丅

堦扷僋儕傾偝傟偨弌椡偼丄師偺俠俲擖椡偑仾偵側傞傑偱丄嵞傃曄壔偡傞偙偲偼偁傝傑偣傫偐傜丄倰倕倗倂俼乮倝値乯偺棫偪忋偑傝偑備偭偔傝偱傕丄偦傟偵傛偭偰僠儍僞儕儞僌揑側岆弌椡偼偍偙傝傑偣傫丅

偨偩棫偪忋偑傝偺僞僀儈儞僌偑抶傟傞偙偲帺懱偼夵慞偝傟傑偣傫偐傜丄乵戞俁俈侽夞乶偺傛偆側岆摦嶌傪杊偖偙偲偵偼栶棫偪傑偣傫乮偦偺岆摦嶌懳嶔偵偮偄偰偼暿偺曽朄傪峫偊偰偄傑偡乯丅

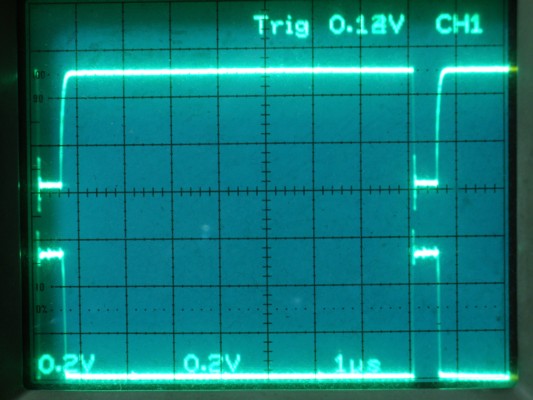

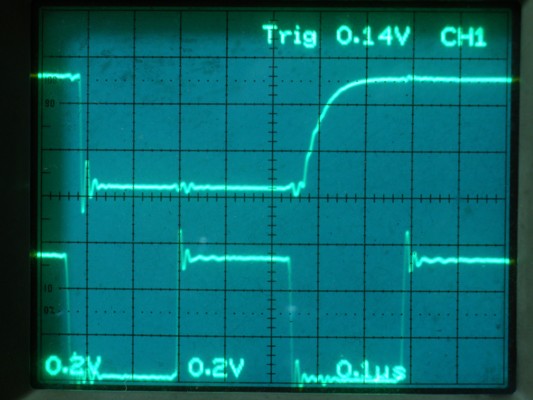

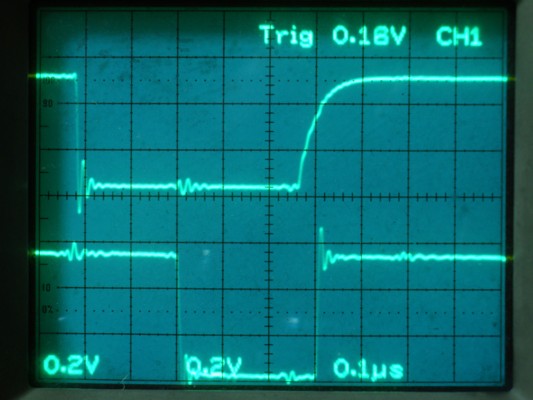

仠倰倕倗倂俼夞楬偺攇宍幨恀偱偡

忋乮俠俫侾乯偑倰倕倗倂俼乮倝値乯丄俈係俫俠侽俆偺弌椡怣崋偱丄壓乮俠俫俀乯偑俈係俫俠俈係偺俢偲俠俴俼傊偺擖椡怣崋偱偡丅

倰倕倗倂俼乮倝値乯偺棫偪忋偑傝偑備偭偔傝側偺偱偡偑丄偙傟偱偼梋傝偼偭偒傝傢偐傝傑偣傫丅

悈暯幉傪侾侽攞偵偟傑偟偨丅

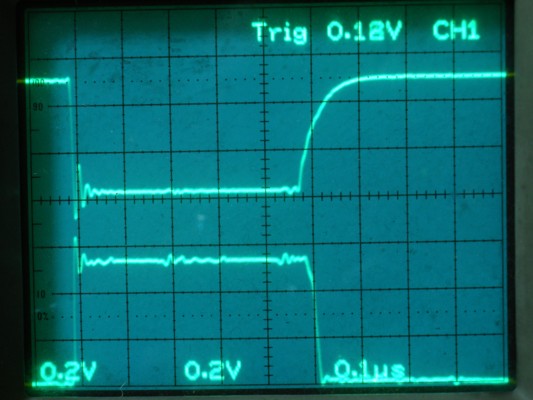

偍偍丄偙傟側傜傛偔傢偐傝傑偡丅

僷儖僗暆偼栺俆侽侽値倱偁傝傑偡丅

俠俫俀乮壓懁乯偼俈係俫俠俈係偺俠俲擖椡偱偡丅

俠俴俷俠俲偺斀揮怣崋側偺偱丄俈係俫俠俈係偺俻丵弌椡偼倰倕倗倂俼乮倝値乯傛傝傕敿僋儘僢僋乮俀俆侽値倱乯抶傟偰俴偵側傝傑偡丅

俠俫俀乮壓懁乯偼俈係俫俠俈係偺俻丵弌椡偱偡丅

偙傟偑儗僕僗僞傗儊儌儕傊偺倂俼怣崋偵側傝傑偡丅

怣崋暆偼俁侽侽値倱偔傜偄偁傝傑偡丅

俀侽侽俋丏侾俀丏俁倳倫倢倧倎倓

慜傊

師傊

儂乕儉儁乕僕僩僢僾傊栠傞